Aleksei_Rostov

Свой-

Постов

313 -

Зарегистрирован

-

Посещение

Весь контент Aleksei_Rostov

-

работает так, если нулевой разряд обнулять только по ресету if (reset) begin mode <= 0; cnt <= 0; shiftReg <= 0; end else begin case (mode) 0: begin mode <= 1; shiftReg[0] <= In; shiftReg[1:14] <= 0; end 1: begin cnt <= cnt + 1; shiftReg <= {In, shiftReg[0:271]}; if (cnt==257) begin mode <= 2; cnt <= 0; end else begin mode <= 1; end end

-

всем большое спасибо за советы! не подумал задержать ресет, хотя раньше с подобным случаем сталкивался. буду двигаться дальше!

-

Понял. спасибо так и сделал. Заморгали лампочки RJ-45. О чудо! есть клоки на tx_clk wireshark ом наблюдаю свой пакет ( по весу (71 байт) совпадает)

-

Спасибо, действительно не подумал. Уровень на ресете высокий

-

Проект загрузил и проверил питающие. Напряжения соответствуют даеашиту. Внешние 25 МГц вижу, txclk и rx clk отсутствуют :laughing:

-

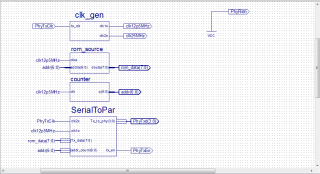

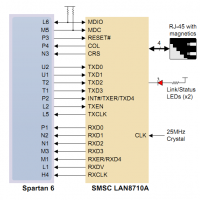

в схемантике модули чтение по 4 бита и формирование txen module SerialToPar( input clk2x, input clk1x, input [7:0] Tx_data, input [6:0] addr_count, output tx_en, output [3:0] Tx_to_phy ); reg tmp, cnt = 1'b1; reg [3:0] tx_tmp; always @(posedge clk2x) begin cnt <= ~ cnt; end always @(posedge clk2x) begin case (cnt) 1'b1: tx_tmp <= Tx_data[7:4]; 1'b0: tx_tmp <= Tx_data[3:0]; endcase end //always @(posedge clk2x) begin // Tx_to_phy <= tx_tmp; // end assign Tx_to_phy = tx_tmp; always@(addr_count) begin if (addr_count <= 72) begin tmp = 1'b1; end else begin tmp = 1'b0; end end assign tx_en = tmp; endmodule клок для чтения ROM и счетчика адреса module clk_gen( input tx_clk, output clk1x, output clk2x ); reg [1:0] cnt = 2'b0; assign clk1x = ~cnt[0]; always @(posedge tx_clk) begin cnt <= cnt + 2'b1; end endmodule UCF ## SMSC ethernet PHY NET "PhyRstn" LOC = "P3" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L2N, Sch name = ETH-RST #NET "PhyCrs" LOC = "N3" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L1N_VREF, Sch name = ETH-CRS #NET "PhyCol" LOC = "P4" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L2P, Sch name = ETH-COL #NET "PhyClk25Mhz" LOC = "N4" | IOSTANDARD = "LVCMOS33"; #Unconnected if R172 is not loaded, Bank = 3, Pin name = IO_L1P, Sch name = ETH-CLK25MHZ NET "PhyTxd<3>" LOC = "T1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L33N_M3DQ13, Sch name = ETH-TXD3 NET "PhyTxd<2>" LOC = "T2" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L33P_M3DQ12, Sch name = ETH-TXD2 NET "PhyTxd<1>" LOC = "U1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L32N_M3DQ15, Sch name = ETH-TXD1 NET "PhyTxd<0>" LOC = "U2" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L32P_M3DQ14, Sch name = ETH-TXD0 NET "PhyTxEn" LOC = "L2" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L37P_M3DQ0, Sch name = ETH-TX_EN NET "PhyTxClk" LOC = "L5" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L43P_GCLK23_M3RASN, Sch name = ETH-TX_CLK #NET "PhyTxEr" LOC = "P2" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L34P_M3UDQS, Sch name = ETH-TXD4 #NET "PhyRxd<3>" LOC = "M3" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L36P_M3DQ8, Sch name = ETH-RXD3 #NET "PhyRxd<2>" LOC = "N1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L35N_M3DQ11, Sch name = ETH-RXD2 #NET "PhyRxd<1>" LOC = "N2" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L35P_M3DQ10, Sch name = ETH-RXD1 #NET "PhyRxd<0>" LOC = "P1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L34N_M3UDQSN, Sch name = ETH-RXD0 #NET "PhyRxDv" LOC = "L1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L37N_M3DQ1, Sch name = ETH-RX_DV #NET "PhyRxEr" LOC = "M1" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L36N_M3DQ9, Sch name = ETH-RXD4 #NET "PhyRxClk" LOC = "H4" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L44P_GCLK21_M3A5, Sch name = ETH-RX_CLK #NET "PhyMdc" LOC = "M5" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L31N_VREF, Sch name = ETH-MDC #NET "PhyMdio" LOC = "L6" | IOSTANDARD = "LVCMOS33"; #Bank = 3, Pin name = IO_L31P,

-

Как я понял настройка происходит автоматически. Потому как больше никаких воздействий кроме вышеописанных я оказать не могу. Как я разобрался сигналы MDC(клок) и MDI для чтения контрольных регистров трансивера, никаких настроек ими не производится.

-

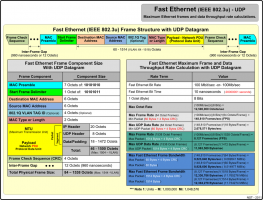

Код довольно прост. Создаю ROM на 1500 байт. В ячейки ROM записываю побайтно UDP пакет: 7 байт преамбула (10101010), 1 байт SFD (10101011), MAC компьютера (6 байт), MAC ПЛИС задаю сам (6 байт), и т.д. весь кадр: Выводы с ПЛИС на трансивер следующие: я задействовал reset, TXD[0:3], TXen, TXclk. Выводы COL, CRS и для контроля MDC, MDIO я не задействовал. Также я не трогал все выводы на прием, т.к. на начальном этапе пытаюсь освоить передачу. Далее на PC есть приложение для установления соединения и приема UDP пакетов, плюс WIreshark. ВЫходные данные ROM я по 4 бита подаю на TXD[0:3], со скоростью TXclk (то есть клок беру из трансивера) Это все я пытался сделать сначала в надежде освоить передачу "слету". Однако не получилось: трансивер не запустился, TXclk отсутствовал. Не судите строго: прекрасно понимаю что такая попытка обречена на провал, но с чего то начать надо было :laughing: К тому же такой путь подсказал человек, у кого есть реализация подобного проекта. Теперь вот что думаю сделать: 1. При запущеном процессоре chipscop'ом сниму все сигналы на трансивер. 2. Подготовлю проект для передачи данных как и раньше считывая с ROM, где задействую все пины на трансивер. 3. Вопрос с контрольными суммами в пакете. По идее wireshark должен увидеть данный пакет (как писали выше в ветке), даже с неправильно рассчитанными суммами. Если такой путь также утопия, с удовольствием выслушаю критику. :rolleyes: Замечу дополнительно: все адреса (MAC, IP, порты) я заранее задаю, таким образом пытаюсь избежать работы с ARP запросами.

-

Создал проект с процессором, вставил туда ядро MAC contr., запустил Hello world/. на RJ 45 заморгали светодиоды. Проверил питающие трансивера -- в норме согласно мануала, осцилографом посмотрел клоки rx tx. Тоже нормально 25 МГц. Сходу попробывал запустить пример для процессора с MAC ядром. Чтобы потом настроить передачу данных на компьютер и Chipscop ом снять сигналы с ног на трансивер. Пример "слету" запустить не получилось. Далее думаю в буфер записать полный кадр и выдать на трансивер. В кадр вставить заданные адреса (MAC, IP, порт). Но для начала небходимо добиться работы трансивера (клоков) без процессора.

-

собрал проект с процессором и Mac ядром, запустил hello world для начала, проект заработал, и заработали светодиоды на разъеме Ethernet, они в свою очередь питаются от трансивера думаю что трансивер жив, в следующий раз проверю наличие клоков

-

совершенно верно

-

большое спасибо за понимание:-) задача следующая: организовать обмен данными с компьютером. протокол UDP. приоритетом является скорость передачи, при чем с компьютера идут управляющие сигналы, реже чем данные с платы.

-

то есть, если сформировать полный кадр для UDP протокола ( преамбулу, маки, ip header, udp пакет, CRC) и отправить на ноги трансивера, сетевая карта его просто не увидит?

-

совершенно верно. если я правильно понял медленная скорость работы процессора с шиной не позволяет разогнать Ethernet. если не прав буду рад любому объяснению. внутренней памяти должно хватить, в том же Spartan 6 18 килобайт аппаратно реализованных блоков ram, пакеты рассматриваю только по 1.5 кб режим работы трансивера задается автоматически на плате. задачу вижу следующим образом: на начальном этапе сформировать кадр и отдать на ноги трансивера по его же клокам, кадр считывать с буфера, потом двигаться дальше

-

Mac я рассматриваю как аппаратно реализованый HDL модуль для формирования пакетов по UDP протоколу например. реализация на базе автомата, когда последовательно на ноги трансивера подается сформированныи Ethernet кадр для передачи по UDP. это случай передачи. совершенно верно. если я правильно понял медленная скорость работы процессора с шиной не позволяет разогнать Ethernet. если не прав буду рад любому объяснению.

-

благодарю за ответ, я не совсем точно выразился. речь идет не о доработке готового проекта с процессором, а о написании своего mac controller чтобы вообще уйти от работы с медленным процессором

-

совершенно верно, другого варианта я просто не вижу

-

Под исходниками я понимаю собранную систему софт-контроллер плюс блок MAC controller. И написанный Си шный код для работы этого контроллера. В Сишном коде реализован сокет Беркли. У меня получилось соединение на другой плате Altera со Stratix II. Там я разобрался как реализован стек на Ниосе и по аналогии поднял Микроблейз в Xilinx. Проблема в Алтере была в том, что там стек реализован на RTOS, а это в свою очередь накладывает ограничения по скорости обмена PC - FPGA (может я ошибаюсь?). Ограничения вызваны, на мой взгляд тем, что контроллеру необходимо время для чтения/записи данных во внутренние буферы. Даже если контроллер тактируется 100 МГц, скорость формирования пакетов все равно низкая. Самый простой пример. Записываю во внутренний регистр в контроллере 0 и единицу. Вывожу содержимое регистра на оссцилограф. Наблюдаю меандр 11 МГц. (около 10 тактов для записи/чтения регистра, при тактировании контроллера 100МГц). Так возникла необходимость написать свой MAC Controller. Под рукой оказался Spartan 6.

-

Запустил трансивер с помощью готового блока с Microblaze. По работе проблем нет. С исходниками проекта (сокет Беркли) более менее понятно. Подскажите пожалуйста, если chipscope'ом снять данные с пинов ПЛИС - трансивер, и по аналогии сделать свой HDL модуль, возможно ли запустить Ethernet?

-

Отсутствуют клоки из трансивера. Причем проверил питающие, ресет...

-

Спасибо. При отсутствии тактовых rx tx действительно есть подозрение на работоспособность трансивера

-

Благодарю за ответы. Сниффер (wireshark) ничего не порказывает. Как проверить трансивер на наличие линка? Режим трансивера устанавливается автоматически, из мануала на боард Что позволяет режим цифровой заглушки? То есть я постоянно должен наблюдать тактовые трансивера? Микроблейз трогать не хочу, тем более с Nios II похожий проект сделал. Интересно свой MAC. Если я правиьлно понял в трансивер по TDX можно пихать все что угодно и наблюдать сниффером?

-

Здравствуйте. Подскажите пожалуйста как можно поднять Ethernet на плате Nexys 3. Перед написанием MAC controllera решил начать с передачи данных на компьютер. Для этого записал кадр в ROM и выдаю его на трансивер (lan8710a). Составил Ethernet фрейм для передачи UDP пакета, записал его в ROM и начал побайтно считывать с частотой 12.5 МГц, чтобы на трансивер выдать по 4 бита на частоте 25МГц. Схема подключения трансивера и плис использовал TXD[3:0], txer, txen, txclk, eth_rst. Из трансивера решил проверить наличие tx_clk оссцилографом. Тактового сигнала нет. Хотя кварц 25 МГц на трансивер работает. Понимаю, что что то не так делаю, но не знаю что. Достаточно ли UDP пакета для установления соединения? или необходим ARP запрос? В UDP пакете указал MAC, IP, port компьютера.

-

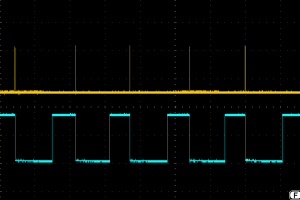

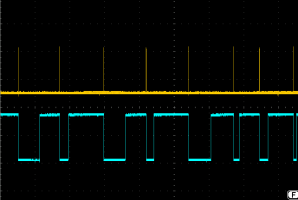

На осцилограф вывел два сигнала: сигнал о наличии пакета (голубым цветом по rising edge) и сигнал о том что пакет отправлен (желтым цветом) Для 3.5 Мбит/с Для 7 Мбит/c На 7 Мбит/с происходит пропуск пакетов

-

Ethernet рассчитан на 100/10 Мбит/с. Пока получил только 3,5 Мбит/c. Необходимо догнать хотя бы до 20-30 Мбит/с. При попытке увеличить скорость, некоторые пакеты просто теряются (последовательно передаю четыре пакета, и сниффером контролирую содержимое принятых пакетов). Размер буфера оставил фиксированный 1458 байт, для предотвращения нарезки пакетов сервером (stratix II). Размер окна пока не варьировал. Хочу отказаться от RTOS но пока не понимаю как (мне кажется причина медленной скорости в RTOS???). Может подскажите можно ли переделать Simple socket server под UDP? как один из вариантов повышения скорости? Поясните пожалуйста, что значит весь протокол? Я рассматривал в качестве начальной точки сокет Беркли, в SSS он и реализован. Если я правильно понял как то можно уменьшить структуру TCP/IP протокола? Пока на очереди идея только с UDP, сам stack в SSS обрезал до минимума.