dde29

Участник-

Постов

112 -

Зарегистрирован

-

Посещение

Весь контент dde29

-

Может тогда подскажете как? Но лично мне то, что я привел - помогало увеличить максимальную частоту работы счётчиков, как на Альтере, так и на Ксилинксе...

-

Cordic на Verilog

dde29 ответил dips11 тема в Алгоритмы ЦОС (DSP)

Здрасьте, я - автор статьи) Писал очень давно, не все помню. Но - что точно можно сказать - точность вычислений зависит от разрядности и количества поворотов вектора на плоскости. В цифре - количества итераций. В реальной жизни можно промоделировать разные варианты, разные разрядности и количество итераций. Получить синус/косинус в виде отчетов и исследовать на паразитные составляющие спектра в MathCAD/MatLAB - добиться допустимых значений и не усложнять себе жизнь. Честно говоря, я щас пользуюсь другим модулем кордика, более лаконичным - а на тот мой древний 2011 года, глаза б мои не смотрели)))) Но он работает, да и в качестве самой математики вычислений - самое то, для новичка, думаю... -

Может пригодится еще: Вот пример конвейерезированного счетчика 24 бит, который разбит на два 12-битных: reg [11:0] cnt_low = 12'd0; reg [11:0] cnt_high = 12'd0; reg cnt_low_done = 1'b0; wire cnt_low_done_buf; assign cnt_low_done_buf = (cnt_low == 12'hFFE) ? 1'b1 : 1'b0; always @ (posedge clk) begin if ((cnt_high == MAX_VALUE[23:12])&(cnt_low == MAX_VALUE[11:0])) begin cnt_high <= 12'd0; cnt_low <= 12'd0; cnt_low_done <= 1'b0; end else begin cnt_low <= cnt_low + 1'b1; cnt_low_done <= cnt_low_done_buf; if (cnt_low_done) cnt_high <= cnt_high + 1'b1; end end Если вдруг оказывается, что самое "узкое" по времянке место в проекте это именно большеразрядный счетчик, то данное решение в виде конвейера - поможет однозначно...

-

Благодарю, учту! Да, это максимум - 2В размах, настраивается резюками, не помню какими - в доке описано...

-

Я немного ввел в заблуждение: AD9235 - это на другой моей плате - второй итерации. А на моделировании, что я приводил - там АЦП стоит LTC2241 - оно 2,5 вольтовое...

-

AD9235 Всем за схемы и ссылки спасибо, обязательно изучу. Вот только вчера наткнулся на какие-то чудеса в железе. Поменял резисторы R1 и R2 с 1к до 1,2к (чтобы увеличить усиление, а значит и размах пик-ту-пик), скомпенсировав потерю амплитуды после резистора 1k на землю - а по факту усиление не увеличилось, а уменьшилось. Причем в LTSpice все ок, а в реале - какая-то хрень - буду разбираться... Если не разберусь - кину свою эту часть схему сюда...

-

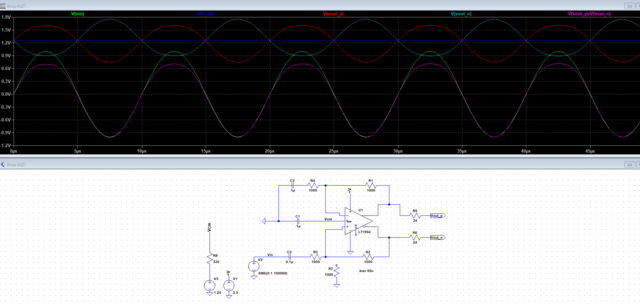

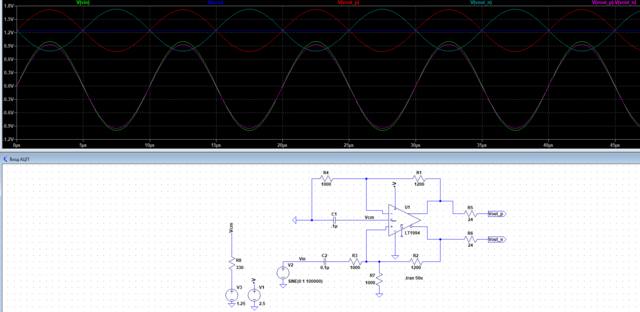

К сожалению, по Вашему совету выходное дифференциальный сигнал получается искаженным... А вот по совету тау: увеличив R1 и R2 с 1к до 1.2к сигнал получился удовлетворительным: Не воспринимаю на словах описание предложенной Вами схемы - не могли бы Вы на бумажке накидать, чтоб хоть какая-то ясность была...

-

В симуляции работает! Оказывается все элементарно же! Благодарю. В скором времени проверю на железе! А с точки зрения физики - почему так? Как токи перераспределяются?

-

Схемотехникам - привет! Возник вопрос с входной цепью АЦП, в которую входит полностью дифференциальный ОУ. Сразу оговорюсь - я не силен в аналоговой схемотехнике и, в частности, в схемах с применением ОУ... На входе платы - сигнал single-ended, который нужно преобразовать в дифференциальный для АЦП. Для этого я собрал в моделировании и в железе следующую схему: (рисунок 1) На осциллограмме симулятора входной Vin и выходной дифференциальный V(vout_p)-V(vout_n) слились Сигнал Vin - без постоянной составляющей подаю с генератора V2, с амплитудой 1В. На выходе получаю дифференциальный сигнал V(vout_p)-V(vout_n) также с амплитудой 1В (2В пик-ту-пик) Так и должно быть - мне это и нужно. НО! Реальный генератор (на другой плате) не может мне выдать двух-полярный сигнал с 0м смещением. Чтобы избавиться от постоянной составляющей я сигнал с генератора пропускаю через конденсатрор C2 Казалось бы я просто убрал постоянку и на выходе должен получить тот же сигнал V(vout_p)-V(vout_n), что и на первом рисунке... Но нет. Оказывается конденсатор влияет на всю схему с ОУ в целом. и на АЦП сигнал приходит с диким смещением а значит обрезается... Это наблюдается как при моделировании, так и в реальном железе... 1й вопрос - почему так??? 2й вопрос - какое схемотехническое решением мне впиндюрить между конденсатором С2 и резистором R3, чтобы получить сигнал V(vout_p)-V(vout_n) как на рисунке 1... Буду благодарен за любые советы... Ругательства разрешаются ))

-

Нашел косяк, почему загруженная прошивка MCS не конфигурировалась в ПЛИС: В одном и скрипте generate_bitstreams.tcl нашел фрагмент, описывающий настройки при генерации MCS: # BPI Flash Programming set_property CONFIG_MODE BPI16 [current_design] set_property BITSTREAM.CONFIG.BPI_SYNC_MODE Type1 [current_design] set_property BITSTREAM.CONFIG.CONFIGRATE 9 [current_design] set_property CONFIG_VOLTAGE 1.8 [current_design] set_property CFGBVS GND [current_design] # Generate Tandem PCIe Bitstreams if { [lsearch -exact $bitstreamTypes "TandemPCIe"] >= 0 } { set_property HD.OVERRIDE_PERSIST False [current_design] set_property HD.TANDEM_BITSTREAMS Separate [current_design] write_bitstream -force -bin_file -file ${outputPrefix}_tpcie > ${outputPrefix}_tpcie_write_bitstream.log # Generate Flash Files Example. This must be updated to match your board and flash settings. ############################################################################### # Flash Programming Example Settings: Modify as required by your design. ############################################################################### write_cfgmem -force -format mcs -interface bpix16 -size 256 -loadbit "up 0x0 ${outputPrefix}_tpcie_tandem1.bit" ${outputPrefix}_tpcie_tandem1.mcs } Проверил каждую строчку... Смутил режим загрузки: BITSTREAM.CONFIG.BPI_SYNC_MODE Type1 Что это за Type1 вообще. Порылся в документации и нашел описание: Sets the BPI synchronous configuration mode for different types of BPI flash devices. Disable (the default) disables the synchronous configuration mode. Type1 enables the synchronous configuration mode and settings to support the Micron G18(F) family. Type2 enables the synchronous configuration mode and settings to support the Micron (Numonyx) P30 and P33 families. Моя конфигурационная флеш никак не относилась ни к семейству G18 ни к P30/P33. Поэтому изменив значение параметра "Type1" на "Disable" и прошивка ver1_tpcie_tandem1.mcs стала правильно загружаться в ПЛИС, сигнал DONE устанавливается в 1 и плата начала определяться в системе... Буду идти дальше в плане загрузки user-logic в ПЛИС...

-

Выложу архив сгенерированного template-проекта в режиме Tandem with Field Updates https://disk.yandex.ru/d/AI_ZLjtWQkbeXA В папке field_update_script расположены скрипты для генерации файлов прошивки В папке Bitstreams находятся уже сгенерированные файлы для Ver1. Это вроде как и должно быть ядро pcie Но, повторюсь, загружая во флеш файл ver1_tpcie_tandem1.mcs. При сбросе питания загрузки конфигурации в ПЛИС не происходит (пин DONE = 0) Но, в тоже время загрузив в ПЛИС мимо флеш файл ver1_pcie_tandem1.bit и после горячей перезагрузки ОС - система определяет плату. Почему не работает вариант с mcs до сих пор не разобрался... Вопрос остановился уже на месте - почему формат MCS не загружается в ПЛИС (DONE = 0, STARTUP_STATE = 0, EOS = 0). Что ему мешает? FLASH BPIx16 подключена к банку 65, к нему же подключен сигнал PERSTN на пин K22

-

Xilinx - Tandem with Field Update

dde29 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Стоит задача: реализовать конфигурацию ПЛИС (Kintex UltraScale) с интерфейсом PCI-Express, позволяющую загружать пользовательскую конфигурацию (user-logic), через приложение ПК посредством PCI-Express. Т.е. при подаче питания в ПЛИС конфигурируется только ядро PCIe (pcie-core), позволяющее операционной системе сконфигурировать устроство. Далее, уже GUI-приложение в любой момент загружает user-logic. У меня возникли проблемы. Опишу ход своих действий дабы местные гуру в данном вопросе подсказали, что я сделал не так. Руководствовался документом PG156: UltraScale Devices Gen3 Integrated Block for PCI Express v4.4 Сразу скажу, что уже создана обычная конфигурация с pcie-core и user-logic. Налажено взаимодействие между ядром и логикой, а также между приложением ПК и устройством. Т.е. проблем с конфигурации самого IP-ядра не было (вернее они были, но решены 🙂 ) - устройство определяется системой при включении. В wizard IP UltraScale Devices Gen3 Integrated Block for PCI Express v4.4 мне следует обратить внимание на следующую опцию: Tandem Configuration or Partial Reconfiguration, которая предлагает следующие варианты: - None - Tandem - Tandem with Field Update - PR over PCIe Под пунктом Tandem понимается два варианта: Tandem PROM и Tandem PCIe. Tandem PROM: создается один bitstream, но внутри он логически разделен на pcie-core и user-logic. Этот bitstream загружается целиком в конфигурационную флеш, посредством программатора или иным способом. При подаче питания первым делом в ПЛИС загружается pcie-core, чтобы успеть, в установленные стандартом, 100мс. Далее, загружается user-logic и устройство становится работоспособным. Проверил - все так и есть. Tandem PCIe: создается два bitstream: tandem1 и tandem2. Tandem1 содержит только pcie-core (на самом деле помимо самого ядра, еще и чуть-чуть окружающей логики) и загружается во флеш. При подаче питания загружается в ПЛИС pcie-core и устройство становится доступным в операционной системе (распознается). В любой момент через особый интерфейс MCAP приложение на ПК может загрузить tandem2, содержащий user_logic и устройство становится работоспособным. Проверил - все так и есть. Казалось бы - БИНГО, проблема решена! Рано радовался, так как создается битстрима то два, но логически они все равно между собой жестко связаны. При изменении в проекте что-то, что касается только user-logic и перекомпиляции опять таки создается два битстрима, и новый tandem2 со старым tandem1 уже не фурычит... Тогда я начал разбираться с Tandem with Field Update: насколько я понял это то, что мне нужно (но это не точно 🙂 ). 1. Сгенерировал IP-корку; 2. Создал template-проект на основе IP Example Design (чтобы уж точно быть уверенным в том, что проект рабочий); 3. При этом создается такой проект, который нужно компилировать в непроектом режиме (non-project). Т.е. предоставляются скрипты (field_update_scripts), запуская которые проект в нужном нам виде компилируется. Имеется главный скрипт, который запускает когда нужно остальные скрипты - design_field_updates.tcl Главное в нем нужно обратить внимание на строки: # Steps for the static portion of the design set runStaticSynth 1 # Steps for the update version 1 portion of the design dependent on having completed runSynthStatic. set runUpdateVer1Synth 1 set runUpdateVer1Impl 1 set runUpdateVer1Bitstreams 1 # Steps for the update version 2 portion of the design dependent on having completed runImplUpdateVer1. set runUpdateVer2Synth 0 set runUpdateVer2Impl 0 set runUpdateVer2Bitstreams 0 # Steps for PR Verify across all Update versions set runPrVerify 0 Т.е. скрипт может создать две конфигурации - Ver1 и Ver2. Насколько я понял Ver1 - это именно то, что нужно записать во флеш и оно будет стартовать первым, т.е. pcie-core. Ver2 - это user-logic. Сначала нужно создать Ver1 записать его на флеш, а потом, проинвертировав флаги скрипта, создать Ver2 - это и будет то, что нужно загружать посредством PCI-Express. Проделав все, как я думаю, как положено я получил следующие файлы: ver1_tpcie_tandem1.bin ver1_tpcie_tandem2.bin ver1_tpcie_update_region_partial.bin ver1_tpcie_update_region_partial_clear.bin ver1_tprom.bin ver1_tprom_update_region_partial.bin ver1_tprom_update_region_partial_clear.bin ver1_tpcie_tandem1.bit ver1_tpcie_tandem2.bit ver1_tpcie_update_region_partial.bit ver1_tpcie_update_region_partial_clear.bit ver1_tprom.bit ver1_tprom_update_region_partial.bit ver1_tprom_update_region_partial_clear.bit ver1_tpcie_write_bitstream.log ver1_tprom_write_bitstream.log ver1_tpcie_tandem1.mcs ver1_tprom.mcs ver1_tpcie_tandem1.prm ver1_tprom.prm Насколько я понял, сначала я должен загрузить во флеш ver1_tpcie_tandem1.mcs. Причем при перезагрузки питания системы, PCIe устройство у меня должно определиться в системе - этого не произошло. НО! Если я загружаю напрямую в ПЛИС ver1_tpcie_tandem1.bit, а затем перезагружаю на горячую систему (чтобы ОС опросила устройства), то все ОК - мое устройство определяется. Т.е. pcie-core сформировано верно. Где-то проблема в процессе старта системы. Но где именно я пока не понял. Может местные гуру - подскажут где я свернул не туда) Ну помимо того, что я в принципе связался с PCIe ))) P.S.: Vivado 2018.1 - Kintex UltraScale xcku060 -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Вы оказались правы! Прочитав конфигурационное пространство командой: hexdump /sys/bus/pci/device/0000:01:00.0/config оказалось, что командный регистр, находящийся по адресу 0x04 гол как сокол (рис.1), а значит флаги I/O Space Enable, Memory Space Enable, Bus Master Enable сброшены в ноль. Аналогичную картину я увидел JTAGом, глядя на регистр cfg_function_status (рис.2) предоставляемый коркой pcie3_ultrascale. Соответствующие флаги Физической Функции 0 были сброшены (Функцию 1 я и не использую, на нее пофиг). С помощью команды sudo setpci -s 01:00.0 04.B=07 попробовал установить все 3 флага. Прочитав после этого снова конфигурационное пространство, убедился что в командном регистре заветную 7-ку (рис.3) Посмотрев JTAGом регистр cfg_function_status, еще раз железно убедился в установленных флагах... После этого отправляя на resource0 мимо всякого драйвера в map я увидел заветные транзакции чтения (рис.4) и записи (рис.5) Смотрел JTAGом цепляясь на интерфейс Completer Request (CQ). Так что, текущая проблема решена, буду двигаться дальше... -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Какую конкретно ip-корку вы имеете в виду под "корка gpio"? В этом проекте имется память. JTAGом я смотрел числе и сигналы память - при операции чтения/запись шевеления на сигналах памяти не было, соответственно делаю вывод, что память не читается и не записывается... И еще: как понять фразу " Gpio автоматом должен обновиться, без всяких своих транзакций"? Ведь, если не было никаких транзакция, то ничего и не должно поменяться, или я что-то не понимаю? 1. Линк поднялся, так как через lspci мое устройство отображается с некоторыми параметрами. С какими конкретно, если нужно, могу позже написать сюда... 2. Так же отображаются адреса BARов и их размер, можно сделать вывод, что система их сконфигурировала? 3. "разрешены соответствующие транзакции (IO, MEM, Master)". А вот это надо глянуть... -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Именно так! Пишем в map и я на интерфейсе CQ не вижу никаких шевелений, цепляясь триггером на valid или last -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Продолжаю разбираться в корке pcie3_ultrascale_0 в Vivado2018.1 Пытаюсь зафиксировать транзакции между Хостом и Таргетом, наблюдая за сигналами в ПЛИС через JTAG. В Вивадо имеется полезная функция Open IP Example Design. Т.е. имеется возможность сгенерировать полностью заведомо рабочий (по крайней мере задумано так) проект с настроенной мной IP-коркой pcie3_ultrascale_0. Таким образом, создается проект где можно и записать в регистры ПЛИС и считать. Проделав все вышеописанное, при записи в БАР никаких транзакция не наблюдаю. Вообще никакого шевеления... Любая транзация, не важно запись/чтение memory или запись/чтения I/O производится через интерфейс Completer Request (CQ) протокола AXI4-Stream. Через следующие сигналы: wire [63 : 0] m_axis_cq_tdata; wire [1 : 0] m_axis_cq_tkeep; wire m_axis_cq_tlast; wire m_axis_cq_tready; wire [84 : 0] m_axis_cq_tuser; wire m_axis_cq_tvalid; Может местные эксперты по PCIe на Xilinx посмотрят на настройки корки, вдруг где-то заветную галочку не установил... (скрины корки прикрепил в ПДФ) Также прикрепляю архив сгенерированного проекта: pcie3_ultrascale_0_ex_1.xpr.zip P.S. Дополнительная информация: ОС Линукс, убунту Попытка чтения/записи в БАРы осуществляется без какого-либо собственного драйвера через отмапенную виртуальную память ПЛИС UltraScale Есть использовать корку AXI Bridge for PCI Express Gen3 Subsystem, но там интерфейс с еще большим количеством сигналов, а я про эту то корку начитался... P.P.S: Любые подсказки и нецензурная брань приветствуются!) Настроки корки.pdf -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

При генерации IP корки для PCIe установил галочку "JTAG Debaging", чтобы была возможность отладки. Сгенерировались скрипты на TCL, но в скриптах в самом начале подключаются нужные пакеты: package require Tcl 8.5 package require Tk Так вот первая строка успешно выполняется вот Tk вивадо не видит... В чем может быть проблема. Как выбрать версию интерпретатора TCL, так как в установочных каталогах версии разные имеются... -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Разобрался с проблемой. Проблема, естесно, не в измерениях): Я пользовался платой KCU105 к которой в нагрузку идет плата PCIe LoopBack в которой сигнал начального сброса PERST просто никуда не подцеплен! И по факту, подтянутая к земле, эта линия держала корку PCI в сброшенном состоянии - соотетственно ГУН ПЛЛ находился в крайнем положении. Поэтому корка выдавала user_clk частотой 25 МГц вне зависимости от настроек лэйнов и частот в визарде корки. Поэтому, пришлось в визарде на вкладке Basic изменить System reset polarity в значение ACTIVE_HIGH. Но! Когда плату планируется вставлять в слот ПК (а не в этот недоделанный LoopBack), то данное значение необходимо вернуть в ACTIVE_LOW -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Я понимаю, что могло быть искажение из-за дискретизации, но глюков измерения тут скорее всего нет, но я еще поковыряюсь конечно, так как это нельзя полностью исключать. Спасибо! -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Еще один момент, который я обнаружил, непонятный мне: сконфигурировав IP-блок UltraScale FPGA Gen3 Integrated Block for PCI Express, я должен был получить user_clock частотой 250 МГц, согласно настройкам корки... Вывед данный клок наружу ПЛИС - осциллом наблюдаю 25 Мгц (да, я не гоню, ноликом не ошибься ). Как можно это объяснить? -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Немного запутался в принципах интерфейса AXI4-Stream. Основными интерфейсам взаимодействия хоста и user logic через IP-блок являются: Completer Requester Interface (AXI4-Stream Master) Completer Completion Interface (AXI4-Stream Slave) Requester Requester Interface (AXI4-Stream Slave) Requester Completion Interface (AXI4-Stream Master) Насколько я понял, изучая документ PG156, взаимодействие между хостом и user logic происходит следующим образом: 1.1 Если хост инициирует передачу пакета - данные появятся на линиях интерфейса Completer Requester 1.2 В ответ на принятый пакет user logic отдает ответный пакет (а может и не отдавать) на линии интерфейса Completer Completion Interface 2.1 Если же user logic инициирует передачу пакета на хост, то это необходимо сделать через линии интерфейса Requester Requester Interface 2.2 В ответ хост может ответить посылкой на линии Requester Completion Interface Правильно ли я понял процесс обмена данными? -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Для первого этапа - достаточно BAR, так как необходимо просто обмен медленными посылками между ПЛИС на плате и ПК. Для второго этапа, скорее всего да - придется задействовать механизм DMA... -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! Драйвер еще не написан, им только занялись, причем не лично я (я плисовод и цифровик-железячник), а другой отдел программистов. По поводу xdma - могу уточнить... -

PCIe - начало...

dde29 ответил dde29 тема в Работаем с ПЛИС, области применения, выбор

Да, как выглядит пространство известно. Т.е. имеется возможность прочитать содержимое конфигурационного пространства через (как я понял) интерфейс: cfg_mgmt_addr, cfg_mgmt_write, cfg_mgmt_write_data, cfg_mgmt_byte_enable, cfg_mgmt_read, cfg_mgmt_read_data, cfg_mgmt_read_write_done, cfg_mgmt_type1_cfg_reg_access Только вот, у меня мозг так устроен, что лучше всего обмен данными устроен через изучение временных диаграмм, коих по данной теме почти нет (ну или мне было не по глазам). Буду Разбираться, благодарю! Да, есть вариант запустить симуляцию, но тут меня кидает в холодный пот. Причина - я раньше работал только с продуктами Altera/Intel? поэтому переход на Вивадо происходит у меня болезненно. Но, хныкать не будем, тоже буду копать в этом направлении! VID и PID, согласен известны уже в самой корке, и также, да, в Линуксе добился того, что ОС подружилась с платой, а значит корка по минимальным настройкам сконфигурирована верно (через lspci распознается как надо). Для того, чтобы начать писать драйвер, согласен достаточно VID PID, но в дальнейшем нужно чтобы корка как-то отвечала на посылки с хоста на плату. Как я понимаю, для этого нужно изучить интерфейс AXI4-Stream (вроде простой). Только вопрос: Посылку от хоста я (мой user code на ПЛИС) могу получить на интерфейсе Completer Request, в ответ мне нужно будет сформировать пакет на интерфейсе Completer Completion. Подскажите, я правильно понимаю данный процесс "запрос/ответ" в контексте простого взаимодействия хост-девайс ? А через этот стандартный драйвер каким образом можно реализовать простейший обмен данными между ОС и платой - через какие рычаги? В каком направлении мне тут покопать? Спасибо! Поизучаю инфу по Вашим ссылкам! -

PCIe - начало...

dde29 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! По роду своей деятельности появилась необходимость "поднимать" PCIe. Прочитано немноло даташитов и прочих талмудов. Собираюсь тут задавать вопросы по данной теме и внимательно слушать советы... Вводные данные: Плата на базе Xilinx Kintex UltraScale, PCIe Gen 3.0 x8, Vivado 2018.1 Первое, что я сделал сконфигурировал IP-блок UltraScale FPGA Gen3 Integrated Block for PCI Express. Сразу появилась нужна знать - как выглядит конфигурационное пространство, полученного IP-блока PCIe? (Данная информация нужна будет для тех, кто будет писать драйвер для ПК). Имеется ли возможность прочитать содержимое конфигурационного пространства (хотя бы ту часть, которую не трогает ОС) без непосредственного подлючения платы в слот ПК? Например, может в процессе генерации IP-блока создается некоторый файл или я могу это сделать через какой-либо интерфейс полученного IP-блока? Заранее, спасибо!