-

Постов

595 -

Зарегистрирован

-

Посещение

Весь контент Kopart

-

не пускает в чат :(

Kopart ответил Doka тема в Архив предложений и замечаний

Поддерживаю! Теперь собщение аналогичное. Чат он вобще живой? -

Если тактовая не с PLL - то и дальше "от нее" желательно работать по спаду. (А то в общем случае скважность может изменятся) В Verilog тоже просто ( @(negedge CLK) )

-

Это схоже с проблемой деления на логике тактовой НЕ на степень 2-ки (например 3) А самый очевидный вариант синтезируемой задержки - использовать 2-ух кратную тактовую (на PLL) :)

-

чистить базу пользователей

Kopart ответил GaLaKtIkUs™ тема в Архив предложений и замечаний

:bb-offtopic: Он же написал "читал регулярно". Или это как говорится раз в пол года :) Или просто и банально - под "Гостем" Но согласен, что стоил по мылу предупредить (например за день :) ) -

чистить базу пользователей

Kopart ответил GaLaKtIkUs™ тема в Архив предложений и замечаний

Страно Вы оцениваете форум - я думал, что среднестастический юзер открывает акаунт с целью написать ответ или создать тему, после того как он прочитал форум как "Гость" и он его заинтересовал. -

Моделирование на разных уровнях абстракции отличается (можно моделировать диод, а можно систему из нескольких комонентов). Вы задумывались о моделировании так широко? Нет общих методов моделирования - поэтому и нет ветки "Моделирование" Или уточняйте в каком разделе Вас интересует "Моделирование"

-

Уже давно привел бы код регистра, с которым "начал мутить" - тогда были исходные данные для ответа. А лучше, если возможно, приводить код на который ссылается "Ворнинг"

-

чистить базу пользователей

Kopart ответил GaLaKtIkUs™ тема в Архив предложений и замечаний

вот-вот мы же не мейл.ру, у которого уже наверно давно за миллион логинов :) :) :) -

чистить базу пользователей

Kopart ответил GaLaKtIkUs™ тема в Архив предложений и замечаний

А какой смысл этого? Люди решили свои проблемы и пока работают сами. Появятся проблемы - могут снова спросить. Ни какого смысла этого не вижу, кроме освобождения занятых "удобных" логинов. -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

Не думаю, что хорошая идея завязыватся на сигнал 1 на линии. От него ничего толового не сделать. Я же написал, что Вы правильно предположили производителя ПЛИС - поэтому сигнал сброса нужен по-определению(поверьте!). А по подстраивание по стопу я не понял - или, если это Вы совместно с начальным состоянием при наличие 1 на линии - то я про это уже написал. -

Если вам достаточно задержки при моделировании, Вы можете ее вставлять как и указалм "after X ns". В квартусе у Вас не получилось, тк Вы скорей всего смотрели диаграмму после фитинга где их и не может остатся(те после синтеза где они игнорируются), но и при "Functional Simulation" в квартусе эти задержки тоже не работают (по отзывам людей испробовавших) Поэтому (если задержка нужна только при моделировании!) Вы ее так получите, но тоько в другом симуляторе - например ModelSim или симулятор Active HDL

-

Средство для Q4.1sp2

Kopart ответил Camelot тема в Среды разработки - обсуждаем САПРы

Мог бы заметить отличие в написании ссылки и того, что у тебя в отображено в адресной строке броузера. Исправленная ссылка http://electronix.ru/forum/index.php?showtopic=2592&hl Про остальные ссылки надеюсь, что понял. -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

Что-то вы не сразу догадались про определение не SRAM-ПЛИС :) Не сталкивались видать... Там просто нет цепей сброса по причине того, что универсальная ячейка может быть как тригером так и логической функцией. -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

Этот ресет нужен обязательно при включении питания ПЛИС, а не для проекта. (я же говорю это НЕ SRAM-ПЛИС, а флеш) Подается от простого монитора питания, когда установилось. кста про четверть такта "0" - он и не поймет что был ноль - так и будет единица. А вот если >=2/3 такта "0", тогда есть вероятность что схватит "левый старт". Но ваш метод тоже схватит "левый ноль" >=1/2 такта - он же проверит снова в середине -> и будет принимать ... -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

reset должен быть, потомучто нету такого блока (для не SRAM ПЛИС проект) Я для этого и опубликовал, предполагая, что со стороны Вы (в полной мере) сможет обозначить узкие моменты самого алгоритма тк я прикинул много сложных вариантов и всегда находил из них выход в моем алгоритме. Мне он кажется проще - избавились от некоторых критичных элементов (хотя бы точность определения старта) Кста на AHDL я (как и Вы) тоже прием кадра разворачивл временой диаграмой по счетчикам - мне тоже нравится так. Но на Verilog'e решил попробовать по-другому - идейку подкинули про МЖФ -> и получилось :) -

ну это тоже самое, что в качестве сигнальника выбирать FreeScale марка известная и распространенная, но не у нас и нету пока веских аргументов переходить от xilinx к actel и от TI к FreeScale Ну насчет известности у Вас незнаю. Но тут (на форуме) много кто с ними работал, включая меня. Навскидку сразу один момент пришел в голову в пользу Actel для студентов - Больше возможностей, чем у CPLD'ышных FPGA

-

Реверсировать порядок бит

Kopart ответил zxazx тема в Языки проектирования на ПЛИС (FPGA)

Quartus Ему уже ответили - нажать на плюсик - там будем виден порядок бит -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

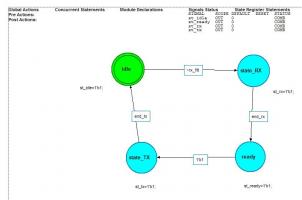

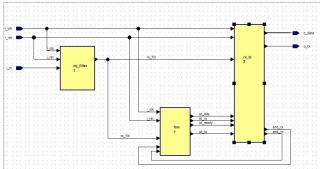

Привожу проект. Но тк это был мой первый пробный проект, то я в нем отрабатывал саму идею реализации. Поэтому это не универсальный стандарт RS232, а конкретная задача, правильность выполнения в живую проверялась в HyperTerminale Винды. Задача: скорость 115200, без паритета, 8 байт, один стоповый. Принимаем "байт" от компа -> суммируем с предыдущим принятым "байтом" и отправляем результат обратно в комп. На компе контролируем правильность работы по сумме скан-кодов. Схема блоками (наглядная) (МЖФ входной, FSM и "общий блок") Простой FSM (в графике наглядней) Сам код "Общего блока" - по нему наврное будет больше всего вопросов(коментил мало) - задавайте. parameter T = 1; //Mj_filter bitov-------------------------------------------- wire en_bit; reg [2:0] dd; always @ (posedge i_rst or posedge i_clk) if (i_rst) dd[2:0] <= #T 3'b111; else if (en_bit) dd[2:0] <= #T {dd[1:0], rx_filt}; reg rx_bit; always @ (posedge i_rst or posedge i_clk) if (i_rst) rx_bit <= #T 1'b1; else if (en_bit) rx_bit <= #T (dd[0]&dd[1])|(dd[0]&dd[2])|(dd[1]&dd[2]); //End Mj_filter bitov----------------------------------------- //Counter clk - Из 40МГЦ получает утроенную 115200 reg [7:0] cnt; always @ (posedge i_rst or posedge i_clk) if (i_rst) cnt[7:0] <= #T 8'h0; else if (cnt[7:0] == 8'd144 ) cnt[7:0] <= #T 8'h0; else cnt[7:0] <= #T cnt[7:0] + 8'h1; //------------------------------------------------------------ //Counter 3x i_clk reg [1:0] cnt_bit; always @ (posedge i_rst or posedge i_clk) if (i_rst) cnt_bit[1:0] <= #T 2'h0; else if (cnt_bit[1:0] == 2'h3) cnt_bit[1:0] <= #T 2'h0; else if ((st_rx | st_tx) & cnt==7'd114) cnt_bit<=#1 cnt_bit + 1; //---------------------------------------------------------------- // Main Block reg [9:0]rx_tx; // Типа общего сдвигового регистра для передачи и приема reg [7:0] rx_reg; // Регистр для хранения предыщего принятого значения, с которым симмирется нынешнее (циклически) always @ (posedge i_rst or posedge i_clk) if (i_rst) begin rx_tx[9:0] <= #T 10'h0; rx_reg[7:0]<= #T 8'h0; // Save RX data end else if(st_idle) rx_tx <= #T 10'h3ff; else if(st_rx & cnt_bit==2'h3) rx_tx[9:0] <= #T {rx_bit,rx_tx[9:1]}; else if(st_ready) begin rx_reg[7:0]<= #T rx_tx[8:1] + rx_reg[7:0]; rx_tx[8:1] <= #T rx_reg[7:0]; end else if(st_tx & cnt_bit==2'h3) rx_tx[9:0] <= #T {1'b1,rx_tx[9:1]}; //--------------------------------------------------------------- // assign en_bit = (st_rx & cnt==7'd114) ? 1'b1:1'b0; assign end_rx = (st_rx & rx_tx[0]==1'b0 & rx_tx[9])?1'b1:1'b0; assign end_tx = (rx_tx[9:0] == 10'h3ff & st_tx) ? 1'b1:1'b0; assign o_tx = (st_tx)?rx_tx[0]:1'b1; //--------------------------------------------------------------- assign o_data[3:0] = rx_reg[3:0]; И общий проект модуль на Verilog RS232.zip PS Принимаются замечания по стилю описания на Verilog!!! Совершенству - нет предела. -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

//Как можно не считая биты узнать, что кадр окончился? Это пишу уже в третий раз - до приема регистр[9:0] (в который будем сдвигать) устанавливаем ВСЕМИ "1", сдвигаем ТАКЖЕ и стартовый бит(который "0") - стартовый "0" добрался до скажем конца (регистр[9] ==0) -> это значит в Вашем понимании "кадр" принялся. под "бодовым байтом" я понимаю информационный "байт" + служебные биты(старт, стопы, четность). В вашем понимании это кадр - что тоже не коректно, тк кадром называют отдельный сегмент на более высоком уровне в транспортной моделе OSI. Хотя Кто-то нам подскажет точное название, приведенное в стандарте. А стробирование - думаю для любого инженера работающего с ПЛИС понятно как - пропуск асинхронного входа через тригер с глобальной тактовой ПЛИС -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

А есть ли смысл разговаривать с человеком, который даже не удосужился перед ответом "не слышал" попробовать посмотреть в любои поиске слово "стробирование". :twak: А особено который имеет дело с ПЛИС!! На пару актуальных вопросиков отвечу: 1. Да согласен - есть лишний такт на выходе МЖФ, впесто простого assign <wire>=... Но он ничего не меняет в алгоритме. Он нужен тк FPGA - "любит" синхронный дизайн. 2. Счетчик я использую только, чтобы считать отсчеты (до 3х) внутри бита. САМИ биты я не считаю! -

Реверсировать порядок бит

Kopart ответил zxazx тема в Языки проектирования на ПЛИС (FPGA)

не могу тут согласиться: вот представьте что вам надо разработать такой блок, оформив его как module реальный пример - бит-реверсивная адресация для БПФ. input [3:0]a; output [3:0]b; и какие бы внутренние wire не вводить, исхитряясь - операцию дающую в итоге "B[3:0] <= A[0:3]" без доп-х манипуляций не получить Да чего то я поверхностно последнее прикинул... Сейчас на проверялся - Verilog 2001 в одну строчку не может переварить :( :( :( А в AHDL это было очень удобно :a14: -

А чего Вы flash'и Actel не расматриваете они тоже маленькие и по настоящему флеши :) :) :) 3 семейство самое то будет для студентов... У них на сайте на халяву можно заказать семплы даже.

-

Лучше избегать таких решений, если не требуется еще большая производительность. Принцип синхронного дизайна предусматривает работу либо от фронта либо от спада. Во первых так вреде синтезаторам проще Во вторых у Вас точно не будет глюков, если скважность тактовой будет плавать

-

Реверсировать порядок бит

Kopart ответил zxazx тема в Языки проектирования на ПЛИС (FPGA)

а помоему вполне съест такое Вы будете очень смеяться, но я сам думал, что так писать можно, пока однажды не столкнулся (в Верилоге) с реальной необходимостью заюзать сию конструкцию. Так вот - синтезатором был послан далеко и надолго. Низзя так писать. Если вы задали вектор как wire [15:0] ddd; то писать потом ddd[0:15] неправомерно ЗЫ: cинтезатор XST от комплекта ISE6.1 (юзаю ка кудобный редактор - по сравнению с 8кой он не тормозит так жутко) Так задача - нужно одному регистру присвоить другой но в обратной последовательности бит. Если так то регистр A[3:0] нужно воспринимать как временный заданный как wire|reg [3:0] A Те сделать присвоение через временый регистр/линию!!! Так даже по Вашему всё оk -

RS-232 + FPGA

Kopart ответил maksya тема в Работаем с ПЛИС, области применения, выбор

Вы знаете что такое простое "стробирование по входу" - так вот МЖФ на входе это просто лучше. При таком сигнале на входе Вам ни какой фильтр не позволит принять сигнал стандарта RS-232. Речь шла о статистически случайных одиночных пичках сигнала на паде ПЛИС, которые МЖФ сглаживает лучше, чем стробирование. Нельзя ориентироватся по среднему - тк я не синхронизую отсчеты с началом бита и этот средний не будет в центре - в центре будет другой средний :) :) :) Так там Verilog'ом по белому и написано, что "грузится Rx прямо в rx_reg[0] " В каком месте (коде) я это написал???? Для асинхронных одиночных кадров совсем не обязателен стоповый бит, а вот для нескольких последовательных кадров - стоповый, скорее, нужен, чтобы на длином промежутке значительной не была рассинхронизация приемника и передатчика. У меня есть регистр, в который я сдвигаю данные, и откуда можо забирать информационый байт. И помимо этого я его же использую при передаче - только в обратную сторону. И вобщето сдвиговый регистр хранит то, что в него вдвинули. Понятие "декодер" - в оригинале это просто демукс, а счетчик это уже другое понятие :)