-

Постов

2 392 -

Зарегистрирован

-

Победитель дней

2

Весь контент repstosw

-

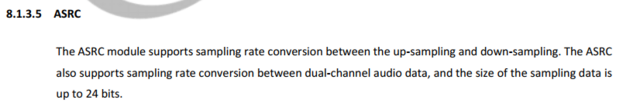

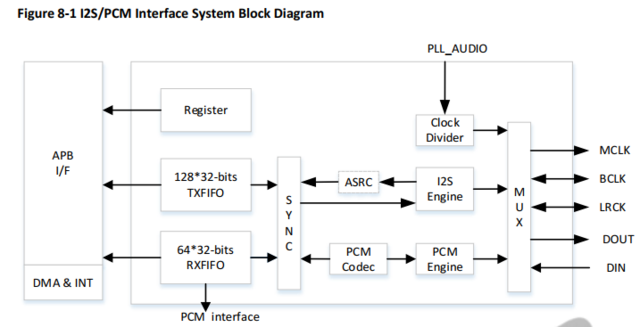

Эти ограничения у MAX98357. Про ресемплирование у T113-s3 здесь: И на структурной схеме показано только одно направление : из внешнего мира в T113:

-

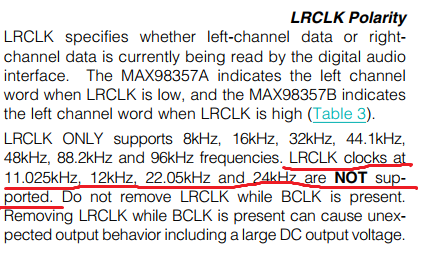

Стр. 16 Но у меня работает. Возможно, свежая ревизия чипов, уже исправили эту несправедливость. Потому что частота семплирования 24 кГц более логична, чем 44.1 кГц, и тем более 88.2. И вообще всё кратное 8 - это хорошо!

-

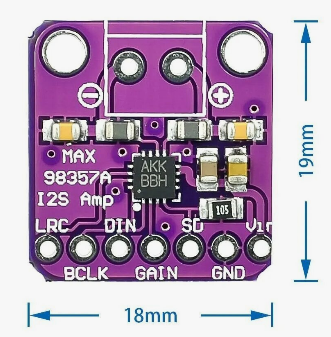

Проверил. Аудиотракт чистый, несмотря на наличие ВЧ излучения 1 Вт рядом с микросхемой. Аналог гениально запрятан в чип и защищён фильтрами, экранами... Штатный PAM8301 летит в помойку: не выдерживает никакой конкуренции с MAX98357

-

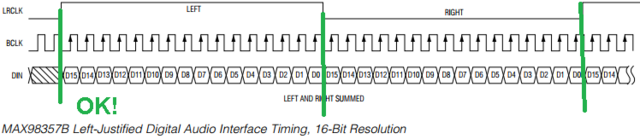

Варианты с выравниванием дадут более уродливый дизайн или потребуют больше вентилей? Даташит на микросхему говорит, что на частоте семплирования 24 кГц работать не будет. Проверил: работает. В обоих случаях: с одинаковым содержимым левого и правого канала, и с разным содержимым. Подвоха не заметил. Мне 24 кГц было нужно. Хотя I2S T113-s3 позволяет аппаратно сресемплировать с коэффициентом 1/8 до 7.5x. Интересно, в бОльшую сторону есть интерполяция или нет? Или тупо дублирование семплов в соседние места?

-

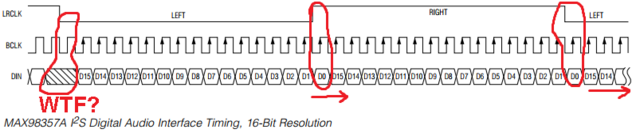

Да. Особенность кодека в том, что этот оффсет надо выставлять отдельно в нужном регистре, а не только в регистре выбора режима. Сам I2S мне кажется несколько дебильным не логичным: зачем этот бит впереди, из-за которого сдвигаются остальные биты в каналах, при этом, младший бит левого канала уходит в строб LRCLK правого канала: На этом фоне, Left- и Right- Justified форматы кажутся более логичными.

-

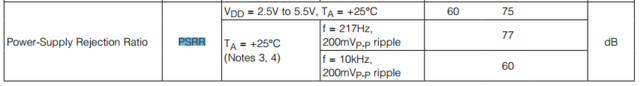

Пришли платы с MAX98357A (заказывал в "АмперКот"). Настроил I2S в режиме настоящего I2S (до этого был режим Right Justified для ЦАП UDA1334BTS). Из особенностей: нужно было добавить +1 offset (в битах 20..21 регистр I2S_PCM_TX0CHSEL), иначе на максимальных амплитудах звук хрипел. С оффсетом всё гладко. Плата по умолчанию с усилением +9 дБ (максимум до 15) и микширует оба канала в один (что мне и нужно!). Отличное подавление пульсаций питающего напряжения - ничего не слышу в наушниках кроме полезного звука. Так что на пульсации питающего напряжение можно забить Осталось проверить, как микросхема поведёт себя рядом с антенной передатчика 1 Вт. И если всё хорошо, то вопрос с "аналогом" можно закрыть.

-

Приведённая схема частотного детектора с DSPlib и выход фазы демодулятора - это разные вещи. Я ничего не делю. По отсчётам фазы нахожу мгновенную частоту. Можно ли по отсчётам фазы просуммировать сигналы?

-

Просто просуммировать два сигнала как комплексные числа? То, что в числителе на схеме.

-

Есть отсчёты мгновенных фаз: Ф1(t) и Ф2(t). Из которых можно получить квадратуры I1(t)=cos(Ф1(t)) Q1(t)=sin(Ф1(t)) I2(t)=cos(Ф2(t)) Q2(t)=sin(Ф2(t)). Или отсчёты частоты F1(t) F2(t). С них можно сделать EGC? О каком ограничении идёт речь? Если нельзя, тогда вторая часть вопроса: допустим есть две пары квадратур I1,I2, Q1, Q2. Для простоты считаем их комплексными отсчётами во времени. Что дальше с ними делать для EGC?

-

Итак... Настало время вернуться к вопросу о манипуляции с данными с двух приёмников, чтобы спастись от плоских замираний. Есть 2 приёмника с антеннами, которые разнесены на лямбда пополам или с взаимно-ортогональной ориентацией. Есть доступ к мгновенным фазам с фазового детектора: atan2 и знак +/-. Вопрос, как правильно "складывать" мощность сигналов чтобы убрать вредительство от замирания? Допустим, с одной антенны сигнал хороший, с другой плохой. Нужно постоянно с каждым отсчётом манипулировать данными отсчётов фазы. petrov что-то говорил пр EGC. Но точно не уверен. Интересует - какие операции нужно проделать над сигналами?

-

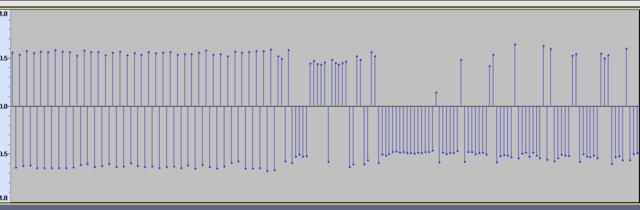

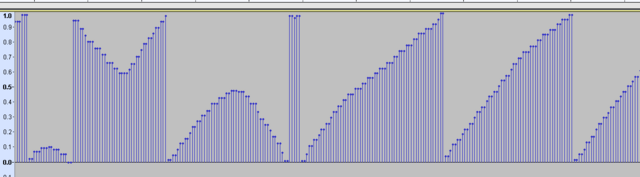

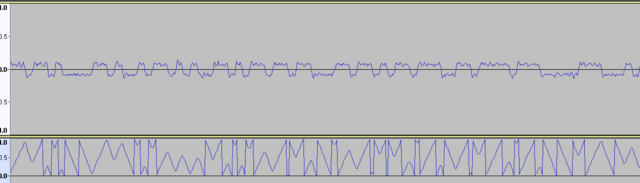

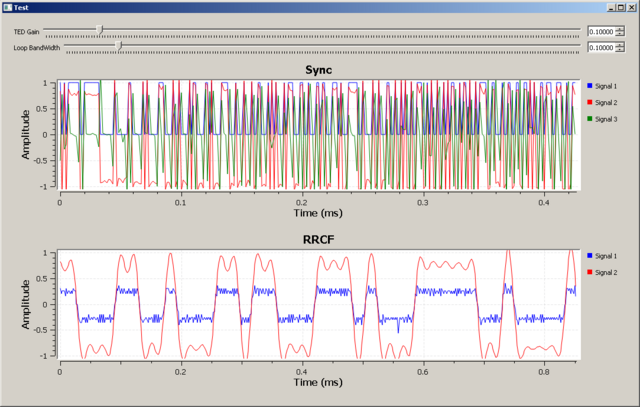

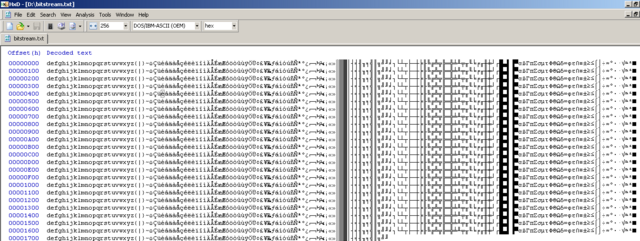

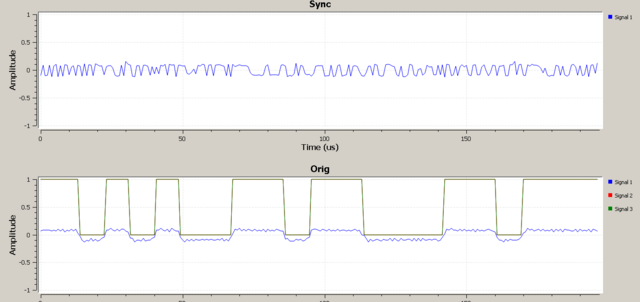

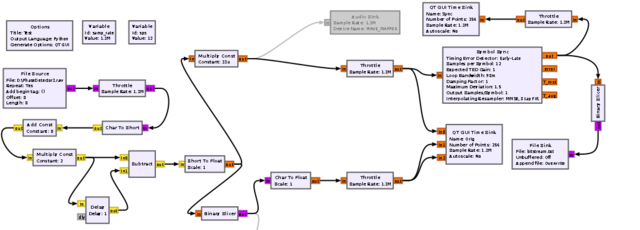

Проверил: выставлял разный Gain для PGA, DAC - результат одинаковый. Ибо AРУ ещё есть потому что. Ну если так, тогда вот мягкие отсчёты - на выходе синхронизатора (умноженные на 0.5, для приведения к [-1..+1] ) - слева преамбула, потом синхрослово 0x5A0FBE66 и потом данные: байты от 0 до 255 : Это 50 кбит/c, девиация +/- 25 кГц. 12 отсчётов на бит(среднее). Запустил на несколько минут симуляцию в GNU Radio (циклически одни и те же анные с файла сигнала). В итоге, протестил все пакеты - все без ошибки. И что самое интересное, мой "детский" алгоритм тоже декодирует пакеты правильно. Но там, где начинает падать отношение сигнал-шум, вариант с синхронизатором работает лучше (больше пакетов даёт валидных, чем "детский" способ). Для 2FSK индекс модуляции понятно как считается. А как он считается для 4FSK? берется inner или outer девиация? P.S. Усовершенствовал забор данных отсчётов фазы с Si4463: теперь данные можно забирать со скоростью 1.615 млн. отсчётов в секунду. Это соответствует заполнению одной половины кольцевого буфера 128 отсчётов за 0.079 мс. По-хорошему надо интерполировать, так как некоторые смежные отсчёты фазы одинаковые.

-

Такая возможность есть. Но частота опроса регистра должна быть высокой, боюсь что вход и выход из обработчика прерывания по таймеру снизят частоту опроса. Спасибо, помогло. Всё-же у Si4463 время выполнения команд ядра 8051 отличается от дефолтного i8051. Первоначально я брал данные о растактовках здесь: https://mp8051.narod.ru/commands.html Подытоживая: mov A,SFR ;2 movx @DPTR,A ;3 inc DPTR ;1 nop ;1 djnz R2,Label ;2/3 mov A,#0x15 ;2 movx @R1,A ;3 clr A ;1 mov R2,#0x18 ;2 sjmp Label ;3

-

Здесь пишу на ассемблере sdas8051. Си не использую.

-

Меня это не интересует. Меня интересует число машинных циклов для каждой инструкции. Проще говоря, во сколько раз одна инструкция быстрее-медленее другой. Нет такой возможности. Точнее - есть, но только в виде "память - SPI". А DMA типа "SFR - память" - нет. Да, он самый! Нужно выставлять ножку в 0 или 1 после заполнения буфера для SPI через DMA. Половина - буфер 128 байт. В буфер кладутся значения SFR-регистра фазы. Требуется очень равными интервалами читать регистр фазы и без джиттера дёргать ножку в 0 и 1 (для IRQ мастер-контроллера). То, что я сделал - работает, фаза дампится в кольцевой буфер для мастер-контроллера, но просмотр отсчётов показал, что есть небольшой джиттер в отсчётах фазы 1-2%. Я помню, умельцы делали на AVR-ках VGA-контроллеры и всякие ГИТС для ТВ с шахматными клетками и полосками - у них всё было ровно: по тактам расчитано. В 8051 такое возможно?

-

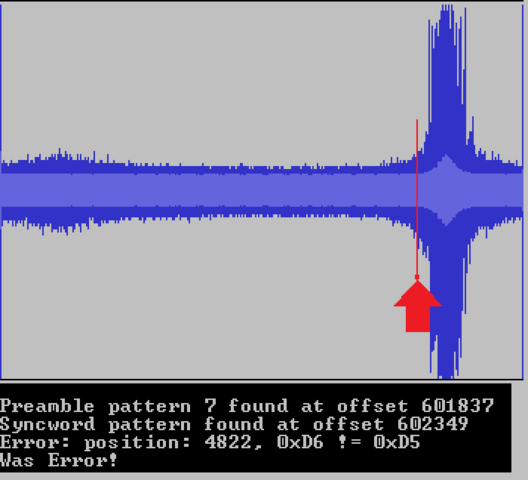

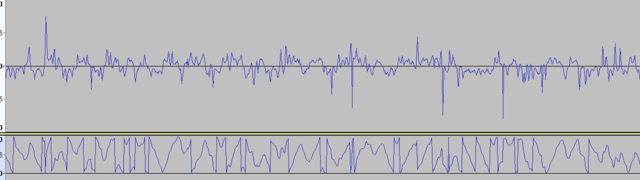

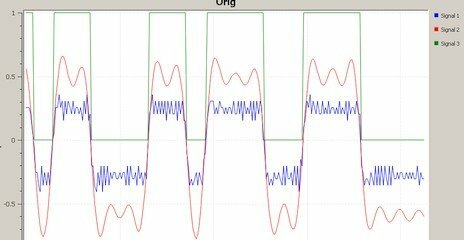

Добавил аттенюатор приёмнику -30 дБ. Мощность передатчика -10 дБм. Передатчик отдалялся от приёмника в пределах 3 комнат. Зафиксированы отсчёты бит с помехами. На рисунке ниже показан бит, начиная с которого пакет терпит неудачу при проверке (длина пакета 6080 байт): Мгновенная частота и фаза (отсчёты) в момент, когда данные не восстанавливаются: Чистый сигнал (для сравнения): Как я понял, что нельзя считать "плoщадь отсчётов" на 1 бит для получения мягкого решения. Есть ли способ восстановить эти биты?

-

8051 число циклов выполнения инструкции

repstosw опубликовал тема в В помощь начинающему

Нужно прецезионно(равными интервалами) организовать считывание из SFR регистра и вывести сигнал на ножку. Не могу найти достоверные растактовки для инструкций ядра 8051. Встречаются разночтения: в одних источниках пишут, что инструкция DJNZ занимает 2/4 цикла в зависимости от результата, а других - в обоих случаях 2 цикла. Интересуют именно число циклов, без привязки к конкретной частоте. У меня недоверие и вопросы: как может инструкция с условным переходом выполняться одинаковое число тактов? Там всегда будет 2 значения циклов - в случае если переход выполнен, и в случае если перехода не будет. В частности меня интересует число циклов выполнения следующих инструкций: mov A,SFR movx @DPTR,A inc DPTR nop ;1 цикл djnz R2,Label mov A,#0x15 movx @R1,A clr A ;1 цикл ? mov R2,#0x18 sjmp Label -

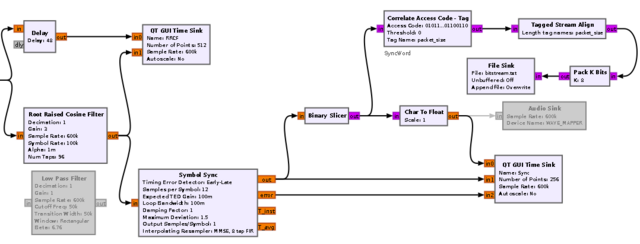

Перечитал посты. Не нашёл как нормировать отсчёты мгновенной частоты. Кроме как что их надо как-то нормировать: Пока сделал Rail-to-Rail Clipper: отсекаю значения всё что выше от 1/4 максимального размаха. Потому что при отсутсвии полезного сигнала, амплитуды шумов в 4 раза выше, чем полезный сигнал. Есть ещё возможность установить по-больше усиление в Si4463 - отсчёты фазы будут больше. Цепочка такая: Отсчёты фазы => отсчёты частоты => Клипирование => Масштабирование => Корень приподнятого косинуса => Блок синхронизации => Бинарный слайсер Декодирование пакета работает правильно. Можно ли улучшить? Второй вопрос: возвращаясь к мягким отсчётам битов. Сейчас слайсер режет сигнал на биты. Как теперь найти "мягкое значение" для каждого бита? Вернуться к отсчётам частоты и времени максимума символа, найденного фильтром косинуса? Или как?

-

OK, ещё раз перечитаю посты в теме. От 10 до 13 отсчётов на один информационный бит Да. Заметил. При больших значениях синхронизатор уходит в расколбас и комп повисает намертво, симуляция останавливается. Удалось заставить синхронизатор правильно работать. А также сдетектил синхро-слово и сформировал пакеты.

-

Попробовал фильтр корня приподнятого косинуса. После определённых настроек теперь число горбов с выхода этого фильтра показывает число смежных бит в сигнале. Красный - выход с фильтра косинуса Синий - исходные отсчёты, полученные как разность фаз (снятые с Si4463) Зелёный - слайсер Надеюсь, оно теперь будет являться хорошей пищей для Symbol Sync.

-

Поигрался в GNU Radio. Завёл свои отсчёты фазы в программу, привёл к нужному типу данных и нашёл мгновенную частоту как разность фаз. На этом лыжи дальше не едут: не получается восстановить частоту символов с помощью штатного блока Symbol Sync. У меня на каждый бит приходится 10...12 отсчётов, это и задаю в программе, но восстановленный поток битов вообще и близко не похож на исходный: Binary Slicer и то правильно работает, в отличие от Symbol Sync. Пробовал записать выходной поток бит после слайсера в файл: в момент преамбулы, запись бит "1" и "0" содержит по 10..12 отсчётов - по понятным причинам. Собственно 2 вопроса: 1) А точно Symbol Sync может работать именно на моих отсчётах сигнала? Может требуется какая-та предварительная обработка сигнала? 2) Возможно ли выровнять число отсчётов на бит уже после слайсера? Мне кажется, так даже будет логичнее - выровнять длительность каждого бита.

-

Хотел поставить себе MATLAB последней версии(2023) Trial, но к сожаелению под Win7 он не идёт. А Matlab 6.5 и 2011R - слишком стары, и они не тянут свежие примеры: отстутствует компонент comm.*. Попробовал запускать модели от petrov в своих матлабах, они открываются, но при симуляции валится много ворнингов. Проблема в кривости моих Matlab'ов или в отсутствии знаний как правильно запускать модели. Смотрел в сторону Octave. Разочаровался что под него примеров мало. Ищу примеры Symbol Clock Recovery. Принял решение остановиться на GNU Radio. Он бесплатен и не выёживается на моём ПК. Для Matlab (крякнутые версии) приходится переводить часы назад, иначе не запускается. А когда переводишь часы назад - интернет не работает (SSL-сертификаты). Поэтому остаётся либо GNU Radio, либо через Python фреймворк работать. Под них куча примеров. GNU Radio хорош ещё тем, что генерит сорцы на Си и сам открытый - можно на раздербан пустить - в плане вытащить алгоритм/фильтры... petrov, komah спасибо за ответы!

-

Требование к целому числу отсчётов - это для выходных данных, которые подаются на интерполятор? Или это интерполятор выдаёт целое число отсчётов? В приведённых последних картинках, у меня на 1 символ может приходиться 11...13 отсчётов. Что делать? Опять же - какое число отсчётов на символ имеется ввиду? До- или после- интерполятора? Прочтитал про TED Гарднера, увидел на картинках, что для его использования - последовательность данных должна иметь 2 отсчета на символ. Питается он этими отсчётами после интерполятора, исходя из структурной схемы, которая приведена в статье Чхоудхури. Получается мне нужен ресемплер в режиме дециматора что-ли? Чтобы свои 11..13 отсчётов превратить в 2 отсчёта для TED? Чё-то каша в голве у меня, пазл не складывается. И вообще, с какими отсчётами мне работать? С фазой или с мгновенной частотой? Если с фазой, то насколько критичны разрывы фазы? Надо ли делать unwrap перед входом на интерполятор. Проще говоря - у меня есть отсчёты фазы , будем пока считать matched Filter внутри микросхемы трансивера. Что подавать на интерполятор? Тоже непонятно. В статье ДВЕ структурные схемы: с одним интерполятором и с двумя. Какую надо использовать? И собственно, что мы этой схемой пытаемся достичь? Чтобы число отсчётов на каждый символ было одинаковым и постоянным? Зачем это нужно для 2FSK? Её можно декодировать даже на глаз, не применяя сложные схемы по стабилизации символьной скорости. При условии, если число отсчётов на символ достаточно большое - в моём случае 11..13 отсчётов. Такое даже ребёнок сдекодирует. Амплитуды там вообще по барабану, это же не КАМ-256 какой-нибудь, а всего лишь 2 FSK. Там только накапливать отсчёты с одинаковым знаком, резать их на биты, а остаток при смене полярности - решать: преобразовывать ли в бит или пропускать... Реализацию на Си я давал уже здесь. Алгоритм работает на моём сигнале. Что за БИХ фильтр? RC-цепочка интегратор? Какая у него реализация - функция выхода от входа описанная в алгоритмах - какая? Есть ли окно для эффекта памяти, какие коэффициенты? Откуда взялись 83 вх и 10 вых отсчётов? Почему именно столько надо? Опять же - зачем для 2FSK восстанавливать тактовую? Когда биты хорошо детектятся визуально перепадами и номинальным числом отсчётов 11..13 ? Всё что меньше - шум и мусор, всё что больше - режется на последовательности из одинаковых бит. И там он вообще 2 схемы привёл. И расписал в общих чертах алгоритм. И самого главного нет - где имплементация на каком-нибудь языке? На Си предпочтительнее. Я вот например - не понимаю как должен быть программно описан matching Filter p(-n*Ts). предполагаю что это приподнятый косинус с которого квадратный корень... Пока у меня в голове каша, если честно. И непонятно вообще - нужно ли в моём случае это делать с 2FSK с 10 отсчётами на бит.

-

1. Документации нет и не будет 2. В качестве донора - сорцы Линукса, у-бута и прочие вещи. 3. Мозговой штурм. Эксперименты. 4. Кое-что даже удаётся сделать по куцему даташиту (GPIO, PWM, I2S, LRADC) Но в основном - жёсткий секс с Линуксом 🐥