Поиск

Показаны результаты для тегов 'vitis'.

-

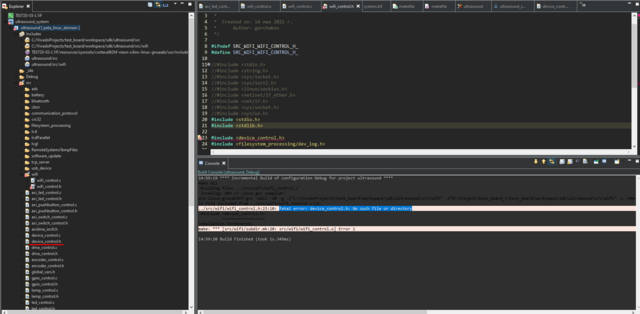

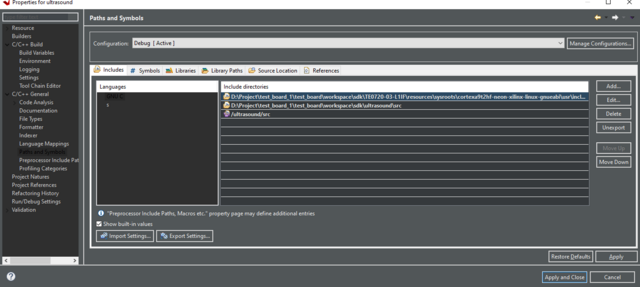

При сборке проекта возникает ошибка "fatal error: device_control.h: No such file or directory". В Includes указал путь к device_control.h, но почему то Includes не обновляется, остаются старые пути. Подскажите пожалуйста в чем может быть дело?

- 2 ответа

-

- fpga xilinx

- fpga

-

(и ещё 1 )

C тегом:

-

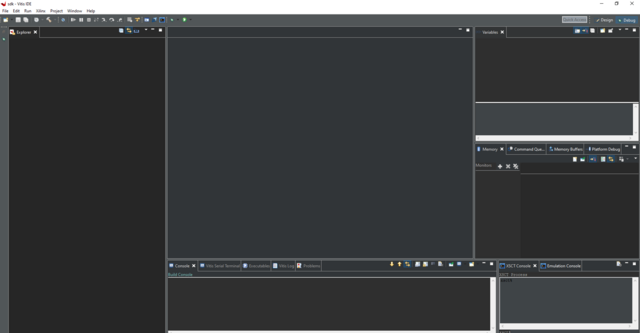

Xilinx Vitis 2019.2

Иван21 опубликовал тема в Программирование

Помогите чайнику. Открываю проект,он пустой, до этого все нормально было, не могу понять в чем дело, ничего не менял, не нажимал где не надо. Заранее спасибо.- 3 ответа

-

- fpga xilinx

- fpga

-

(и ещё 1 )

C тегом:

-

На вебинаре будут показаны новые функции продукта, включая модели, программные инструменты и блоки обработки данных для глубокого обучения. Подробнее

-

fpga xilinx Релиз Vitis Al 2.0 от Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Xilinx обновил свою среду разработки приложений искусственного интеллекта Vitis AI. Теперь разработчикам доступна версия 2.0, которую можно скачать совершенно свободно с репозитория Xilinx по ссылке https://github.com/Xilinx/Vitis-AI Подробнее -

Компания Xilinx сообщила о выходе нового релиза программного обеспечения Vivado ML и Vitis версии 2021.2. Подробнее

-

вебинар Знакомство с экосистемой Xilinx. Вебинар

МакроГрупп опубликовал тема в Объявления пользователей

На вебинаре Вы узнаете, какие готовые устройства и отладочные платы существуют, какие фреймворки и библиотеки можно использовать для ускорения приложений и где найти всю необходимую информацию. Подробнее -

Xilinx ADAPT EMEA. Онлайн конференция

МакроГрупп опубликовал тема в Объявления пользователей

Компания Xilinx c 9 ноября по 16 декабря 2021 года проведёт онлайн конференцию для регионов Европы, Ближнего Востока и Африки по адаптивным вычислительным технологиям Xilinx. Подробнее -

На данном бесплатном вебинаре Майкл Шварц, представитель PLC2, расскажет и покажет: чем является фреймворк Robot Operating System (ROS) какие ключевые этапы содержит процесс разработки ПО в Vitis пример интеграции в камеру дизайна на основе MPSoC Подробнее

-

Компания Xilinx официально представила фреймворк для создания и развёртывания приложений интеллектуальной видеоаналитики на целевых платформах Xilinx или на ваших собственных платформах Vitis ™ Video Analytics SDK (VVAS). Созданный на базе Xilinx Vitis ™ и Vitis ™ AI, он основан на популярном фреймворке Gstreamer и предоставляет возможность использовать плагины для разных задач, включая импорт видео, предварительную обработку, глубокое обучение и постобработку. Возможно писать код C/C++ или Python с VVAS для создания сквозных конвейеров IVA. Подробнее

-

Компания Xilinx объявила о приобретении Silexica – частной компании-разработчика инструментов для программирования и анализа на языках C/C ++. Набор инструментов Silexica SLX FPGA позволяет разработчикам получить полезный опыт разработки приложений на FPGA и адаптивных SoC. Данная технология будет интегрирована в унифицированную программную платформу Xilinx Vitis™, чтобы существенно сократить время обучения разработчиков программного обеспечения, создающих сложные приложения на основе технологии Xilinx. Подробнее

-

vitis Компания Xilinx представила релиз Vitis 2021.1

МакроГрупп опубликовал тема в Объявления пользователей

-

- xilinx

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

В данном вебинаре вы познакомитесь с основными особенностями нового поколения адаптивных систем Versal, с тем, какие среди них существуют вариации и в каких сферах их применение принесёт максимальную пользу. Подробнее

-

- плис

- fpga xilinx

- (и ещё 7 )

-

Компания Xilinx приглашает вас присоединиться к бесплатному двухдневному онлайн-тренингу, организованному совместно Xilinx Customer Training и авторизованными поставщиками обучения Xilinx. Онлайн-тренинг поможет вам быстро изучить Versal™ ACAP и приступить к проектированию устройств на его основе. Подробнее

-

Вебинар от компании PLC2 даст вам представление об основных структурах ПЛИС компании Xilinx, основываясь на реальных задачах машинного зрения и ИИ. Зарегистрироваться

-

Vitis HLS и вектор на входе функции

Strob опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день коллеги. Потратил уже кучу времени на пустяковую казалось бы проблему. Решения адекватного до сих пор не нашел. Был vivado hls, была в нем описана функция с вектором на входе. Чтобы грузить весь вектор сразу, параллельной шиной, использовалась директива array_reshape. Все логично, все просто. Берём vitis hls, и облом. Читаем доки, читаем варнинги. Array_reshape не поддерживается для входов. Витис упрямо лепит интерфейс памяти. Никакой альтернативы для получения того же результата найти не смог. Точнее альтернативы есть, но они скорее нагромождение костылей. Неужели теперь с этим жить? Или я что-то упускаю? -

На вебинаре вы познакомитесь с новой средой разработки Vitis, в которой реализована парадигма высокоуровневого проектирования, и с двумя новыми аппаратными платформами от Xilinx – Versal и Alveo, для которых разработка в среде Vitis наиболее эффективна. Вебинар предназначен как для разработчиков для ПЛИС и СнК, желающих повысить свою продуктивность с помощью средств высокоуровневого проектирования, так и для программистов, ищущих возможности повышения производительности своих компьютерных систем с помощью адаптируемых аппаратных ускорителей Xilinx Alveo. Вебинар состоится 31 марта в 14:00 (мск). Повтор вебинара 2 апреля в 10:00 (мск). Участие в вебинаре бесплатное, после предварительной регистрации. Регистрация на вебинар

-

vitis Vitis Git

Nick_K опубликовал тема в Среды разработки - обсуждаем САПРы

Итак новая платформа с новыми возможностями и отсутствием вменяемых гайдов. Всё как обычно, но работать то нужно, отсюда возникает задача создать проект и залить его на Гит. Для одного компа всё вроде бы работает, но создаётся впечатление, что в объективных файлах проекта (bare metal) прописывается абсолютный путь ибо на других машинах уже ничего не рабоатет. Возможно кто-то использовал Vitis с Git'ом или знает как это делать. Буду благодарен за любую информацию от ссылок где кто-то как-то делал гайды или конкретную документацию (ug1400 не помог никапли). Создаётся впечатление, что как в Vivado придётся создавать tcl скрипты с организацией проекта и последующей генерацией структуры, а этого очень не хочется.

Xilinx.jpg.283d2a22efee14c9d02c85da995a1fa2.jpg)