Поиск

Показаны результаты для тегов 'schematic'.

-

Масштаб Шрифта импортированной библиотеки

Troir опубликовал тема в Altium Designer, DXP, Protel

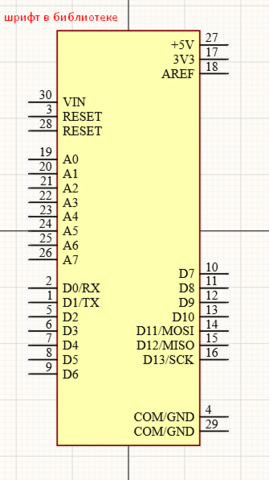

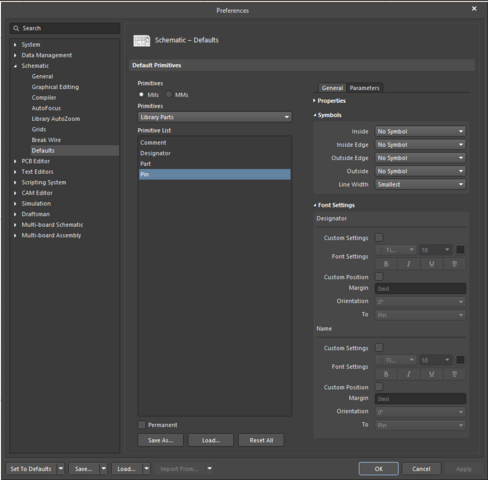

Здравствуйте, при работе с библиотечными файлами шрифт на схеме изменяется на гостовый из preferences, в результате текст подписей и нумерации пинов накладывается до едва читаемого состояния. При прохождении "Быстрого старта" я установил файл предпочтений, идущий с ним, и теперь часть текста, как на схемах, так и в дизайнере платы отображается слишком большим. Я уже поменял все поля связанные с текстом в "defaults" для схем, отключал и включал галочку "override library primitive", копался в панели "SCH List", ничего не помогает сохранить шрифт из файла библиотеки при импорте(там нормальный по размеру). Единственный способ который я нашел, чтобы исправить текст в документе - менять текст за 10 кликов для каждого пина в разделе свойств компонента. Наверняка должен быть какой-то способ добиться автоматического форматирования текста через предпочтения(preferences), но я не могу додуматься до него. Есть подозрения что предпочтения не распостраняются на документ, потому что настройки шрифта для десигнатора и имени в preferences->schematic->defaults-> primitives->library parts раздел Primitive List -> Pin-> font settings(Скриншот 3), не даёт результата, даже при создании нового документа. Помогите пожалуйста разобраться, если кто-то сталкивался с подобной проблемой или знает в чём дело. -

bus/harness в схематике

serg_Fry опубликовал тема в Altium Designer, DXP, Protel

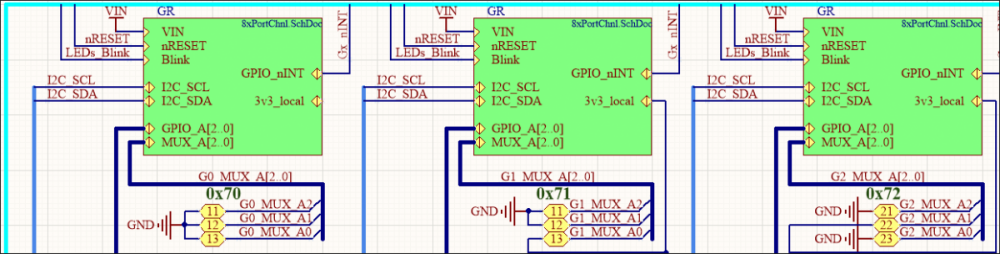

В проекте есть несколько одинаковых каналов. Канал в схематике оформлен, как отдельный лист. Несколько каналов в виде SheetSimbol'ов расположены на Top-уровне схемы (на картинке ниже). В состав канала входит микросхема с интерфейсом I2C. Адрес I2C конкретного экземпляра микросхемы выбирается соединением ее пинов MUX_A[2:0] с землей и питанием. Хочу вывести шину MUX_A[2:0] из каждого канала на верхний уровень иерархии чтобы там каждому каналу присвоить свой адрес: На картинке я уже попытался обойти проблему конфликта имен цепей с помощью портов. Ошибок при компиляции нет, но и цепи назвались не так, как нужно: например в PCB редакторе G0_MUX_A2 получила какое-то имя, хотя должно быть GND. Как это правильно сделать? Иначе говоря, как выборочно соединить какие-то разряды шины скажем с землей? В идеале было бы сделать это через NetLabel шины как-то так: [GND,VCC,GND]. Это, пожалуй, самый наглядный вариант. Вытаскивать из SheetSimbol'а отдельные биты (не в виде единой шины) очень бы не хотелось - некрасиво и займет очень много места. Возможно нужно использовать Harness, но я не понял как. Нашел решение с Net tie. Но оно неправильное, как мне кажется, в данном случае. Настройки иерархии проекта: -

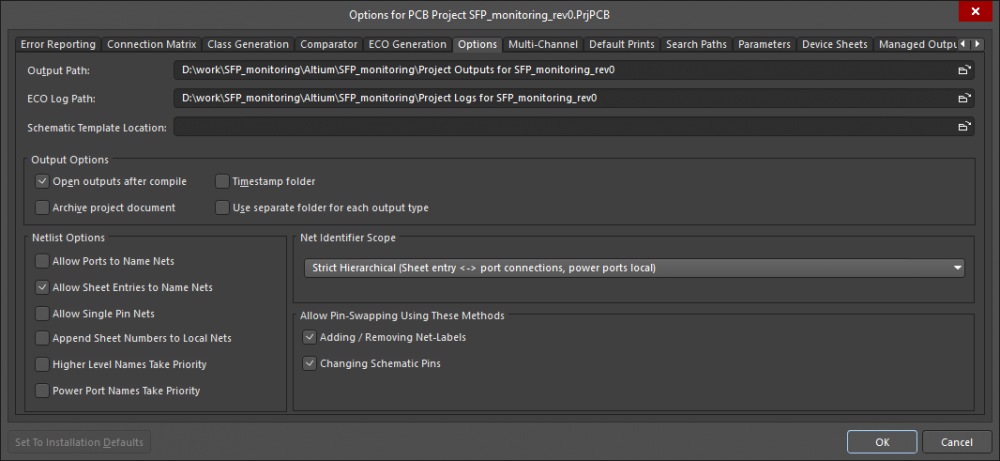

Не могу заставить Altium автоматически именовать компоненты, как мне нужно. Имеется схема в которой 48 портов SFP, объединенных в группы по 8 шт (SFP-cage на 8 модулей). Иерархия схематика проекта имеет 3 уровня: TOP - верхний уровень: все общее для платы Group - схема уровня группы из 8 портов SFP (некоторые компоненты обслуживают всю группу), на листе TOP расположено 6 экземпляров Group. Всего получается 6 экземпляров. Port - схема на уровне одного порта, на каждом листе Group расположено 8 экземпляров Port. Всего 6*8=48 экземпляров. Group и Port - SheetSimbol'ы. Repeat я не использую (как я понимаю, при работе с ним можно использовать сущность "Channel" в настройках среды). Я бы хотел чтобы на каждом уровне иерархии компоненты получили имена следующего вида (на примере конденсатора): TOP: C? (С3) Group: C?_GR? (C4_GR1) // GR - Designator листа "Group": GR1..GR6 Port: C?_PT?_GR? (C5_PT2_GR1) // PT - Designator листа "Port": PT1..PT8 Пробую разные вариации именования в разделе ProjectOptions->Multi-channel. Возможно, нужно использовать Rooms и SheetNumbers. Кажется вариантов много, но найти подходящий пока не получается. Возможно, моя постановка задачи неверная. В таком случае, подскажите, пожалуйста, как вы решаете вопрос с именованием компонент для проектов с иерархией на 2 и более уровней вложения.