Поиск

Показаны результаты для тегов 'parallel sum'.

-

Максимальная частота тактирования

Manvel опубликовал тема в Языки проектирования на ПЛИС (FPGA)

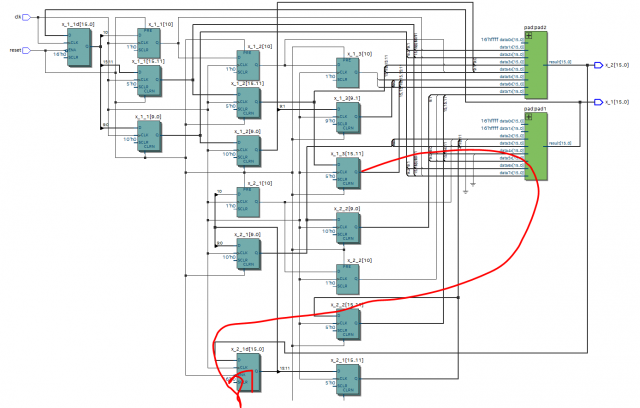

Здравствуйте, уважаемые товарищи! Эти вопросы я задавал на форуме интела но исчерпывающих для себя ответов не получил (https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/Parallel-sum-frequency/m-p/1286075#M19982), поэтому решил повторить вопросы на данном форуме. И так, у меня есть задача смоделировать хаотическую систему, которая по сути из себя представляет 2 цифровых БИХ фильтра с нелинейным элементом в обратной связи. В процессе ознакомления с Verilog и с Quartus я решил, что высокой скорости можно добиться при использовании для этой задачи мегафункции от Квартуса - Parallel sum. В целом, на том железе, что у меня сейчас есть в распоряжении (DE10-lite и ice40-dac) все нормально работает на частотах тактирования 100 МГц, но имеется необходимость поднять частоты. На форуме интела мне подсказали, что надо задавать временные ограничения. Я прочитал немножко литературы (в частности https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-timing-analyzer.pdf) и у меня возникли вопросы. 1. Нужно ли задавать дополнительные временные ограничения для синхронной логики, кроме ограничений на частоту клока, например "set_max_delay -from [get_registers {x_1_3*}] -to [get_registers x_2_1d*] X ns"? Когда я задаю эти дополнительные ограничения, это почти никак не влияет на скорость собранного проекта, может эти ограничения надо задавать по другому? 2. Второй вопрос относится к быстрой и медленной модели проекта в Таймквесте. Для медленной модели Таймквест оценивает максимальную частоту около 200 МГц при этом для быстрой модели частота достигается до 340 МГц, что как бы разница существенная. По их документам (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01139-timing-model.pdf) не понятно, скорость быстрой модели больше зависит от напряжения подаваемого на кристалл или от качества кристалла, эти два параметра занесены под одну модель, а железа на такие скорости пока не имеются для экспериментальной проверки, ну и покупка железа будет зависеть именно от возможных максимальных частот.- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом: