Manvel

Участник-

Постов

16 -

Зарегистрирован

-

Посещение

-

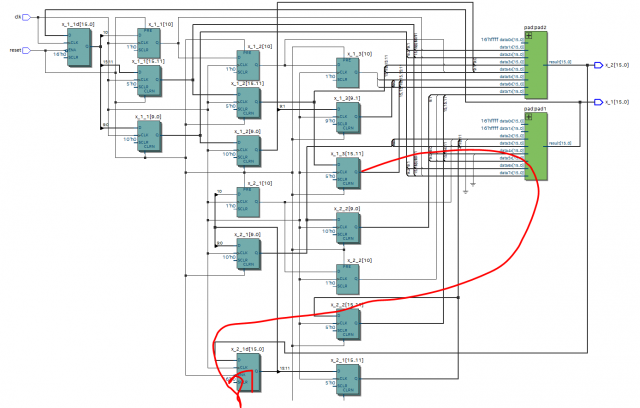

Прошу прощения за такое долгое отсутствие реакции. Нелинейный элемент просто функция без памяти, обратная связь в вне БИХ тоже есть те. выход БИХ1 подключен входу БИХ2, выход БИХ2 к нелинейному блоку, выход нелинейного блока к входу БИХ1. Ну в принципе, выход КИХ ДСП блока если подключить к его же входу через коэффициент получится БИХ. Только у меня сейчас под рукой MAX10 только, а тут нет ДСП полноценных блоков, только 9 битные блоки умножения.

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Спасибо, поищу.

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

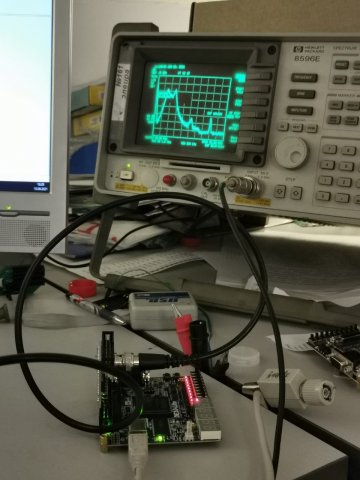

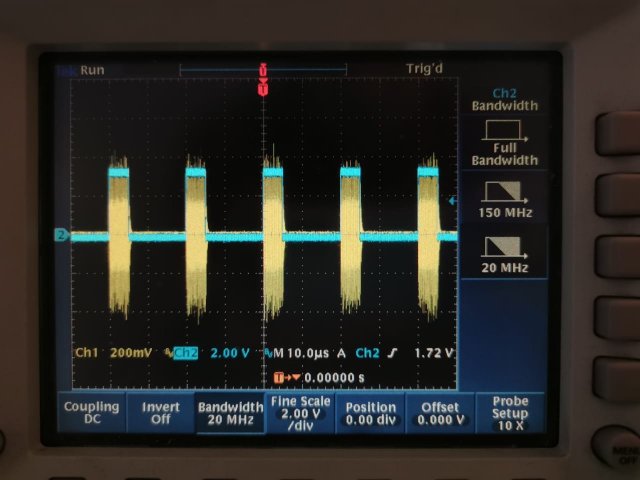

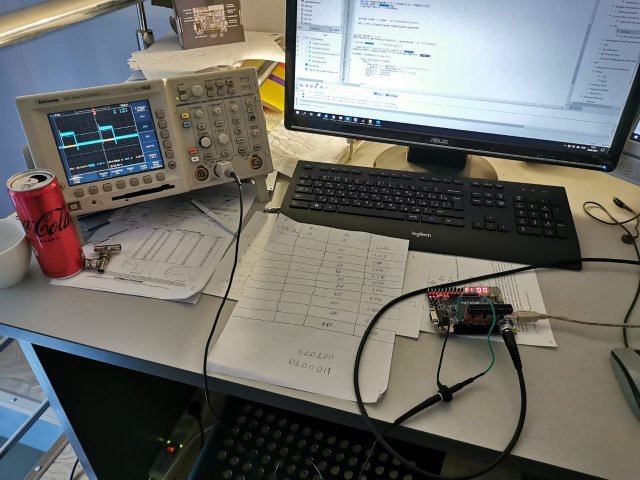

Тут вопрос не в солидности, а в том, что имеет ли все это смысл делать вообще. Схема цифрового генератора делается для системы связи и ширина полосы играет серьезную роль. Я уже запустил на полосу 20 МГц (полоса в данном случае ограничивалось полосовым фильтром после ЦАП, использовалось то, что на данный момент имелось под рукой на 10-30 МГц) на базе борд DE10 lite и АЦП/ЦАП olimex (Прикрепляю фото, полосы хаотического сигнала, импульсов во времени и импульсов после приема огибающей). По поводу конвейеризации, система, как я говорил с обратной связью, для подсчета N+1 точки надо знать N-ую. Допустим сделал я конвейер, и новые точки у меня получаются допустим за 10 тактов, задали начальные условия системы и запустили, через 10 тактов получили первое значение, и теперь чтобы получить второе значение мне надо засунуть первую точку в самое начало, те на следующий такт не получиться 2-ое, оно посчитается только через следующие 10 тактов, и все преимущество конвейера тут теряется. Даже если я заранее заполню все регистры конвейера так, чтобы на следующий такт от первого появится 2 число, все равно из-за обратной связи первый попадает обратно в начало и через 10 тактов будет опять 2-ое число. Но всем товарищам огромное спасибо за ваши советы и мысли, очень приятно удивлен активности и доброжелательности данного форума!!!!

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

О таком я читал, но пока до реализации не дошел

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Спасибо за подробный ответ!

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Ну, насколько я понял, когда я использовал умножение, квартус автоматом использовал эти DSP блоки при компиляции проекта, и скорость в таком случае был ниже, чем при замене умножения на суммирование.

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

ИРЭ им. В.А. Котельникова РАН, вот ссылка на дореволюционный сайт, но там в принципе все есть http://cplire.ru/rus/InformChaosLab/index.htm Можете порекомендовать какой-нибудь DSP борду для обучения, если такие существуют?

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

То что я делаю, по сути из себя представляет систему из двух диф уравнений 2 порядка (приближенно можно сказать, что 2 фильтра 2-го порядка ФНЧ и ФВЧ) с нелинейной обратной связью. Далее вместо того, чтобы решать методом Рунге Кутта эти уравнения я делаю билинейное преобразования и получаю цифровое представление этой системы. В приведенной выше статье все эти шаги достаточно подробно описаны. Я не использую Альтеровсике библиотеки цифровых фильтров, потому что они относительно медленные из-за использования блоков перемножения, в данном случае, чтобы максимально ускорить систему я даже перемножения не использую, а просто суммирование со смещением максимум по первым трем битам коэффициентов цифрового фильтра. Скоро я должен буду приготовить семинар по тому что я сделал, если вам интересно, скину презентацию. То что вы предлагаете я ранее обдумывал, но у меня не вышло это никак реализовать, но я еще подумаю над этим, спасибо за совет!

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Вопрос наверно слишком ламерский) Мне для генерации сигнала важна скорость базовых арифметических операций, чтобы вы лучше представили что мне надо, вот ссылка вопрос, где частично показан способ генерации (https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=162268).

-

Ну я пока только начал разбираться в теме FPGA и работал только с DE10-lite, поэтому чуть опасаюсь от неизвестных мне производителей кристаллов. Те неизвестных мне параметров будет больше, но с другой стороны уже имеется готовое программное обеспечение для тестировки ЦАП. А насколько сопоставимы по скорости пятый циклон и латтис LFE3-35E?

-

Конверизацию устроить не получится, так как система с обратной связью, пока n-ое значение не посчитаешь, нельзя посчитать n+1 -ое. Всем спасибо за ваши ответы, они, кончено, частично расходятся) но мне стало яснее) Это не совсем формула, и на картине проект неполный. Если вас заинтересовало явление динамического хаоса предлагаю прочитать книжку Кузнецов С. П. "Динамический хаос", ближе к тому, что я именно делаю, будет статья прикрепленная к ответу Kuznetsov-SP-Dinamicheskii-haos.djvu Ustanovlenie_haoticeskogo_sinhronnogo_otklika_pri_.pdf

- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Максимальная частота тактирования

Manvel опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, уважаемые товарищи! Эти вопросы я задавал на форуме интела но исчерпывающих для себя ответов не получил (https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/Parallel-sum-frequency/m-p/1286075#M19982), поэтому решил повторить вопросы на данном форуме. И так, у меня есть задача смоделировать хаотическую систему, которая по сути из себя представляет 2 цифровых БИХ фильтра с нелинейным элементом в обратной связи. В процессе ознакомления с Verilog и с Quartus я решил, что высокой скорости можно добиться при использовании для этой задачи мегафункции от Квартуса - Parallel sum. В целом, на том железе, что у меня сейчас есть в распоряжении (DE10-lite и ice40-dac) все нормально работает на частотах тактирования 100 МГц, но имеется необходимость поднять частоты. На форуме интела мне подсказали, что надо задавать временные ограничения. Я прочитал немножко литературы (в частности https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-timing-analyzer.pdf) и у меня возникли вопросы. 1. Нужно ли задавать дополнительные временные ограничения для синхронной логики, кроме ограничений на частоту клока, например "set_max_delay -from [get_registers {x_1_3*}] -to [get_registers x_2_1d*] X ns"? Когда я задаю эти дополнительные ограничения, это почти никак не влияет на скорость собранного проекта, может эти ограничения надо задавать по другому? 2. Второй вопрос относится к быстрой и медленной модели проекта в Таймквесте. Для медленной модели Таймквест оценивает максимальную частоту около 200 МГц при этом для быстрой модели частота достигается до 340 МГц, что как бы разница существенная. По их документам (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01139-timing-model.pdf) не понятно, скорость быстрой модели больше зависит от напряжения подаваемого на кристалл или от качества кристалла, эти два параметра занесены под одну модель, а железа на такие скорости пока не имеются для экспериментальной проверки, ну и покупка железа будет зависеть именно от возможных максимальных частот.- 73 ответа

-

- timequest

- timing constraints

-

(и ещё 1 )

C тегом:

-

Я его видел, но у меня сложилось впечатление, что это только тестовая плата для работы с ЦАП, насколько я понимаю, там стоит софт от ТИ и он не очень предназначен для перепрошивки. Я склоняюсь к DE10-Standart, там достаточно быстрый циклон 5 и разъем вроде подходящий, только надо внимательно разобраться, на что пока времени не нахожу. А так, спасибо за Вашу подсказку!

-

Спасибо за разъяснения!

-

Спасибо за ответ! Правильно ли я понимаю, что данный цап будет подходить ко всем бордам с HSMC разъемом? В частности меня интересовал более быстрый циклон terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=165&No=1081 , вроде и у цап и у этой борды LVDS 16 бит, но рассматривая документацию я так и не понял насколько они совместимы по распиновке