Поиск

Показаны результаты для тегов 'ip-ядро'.

-

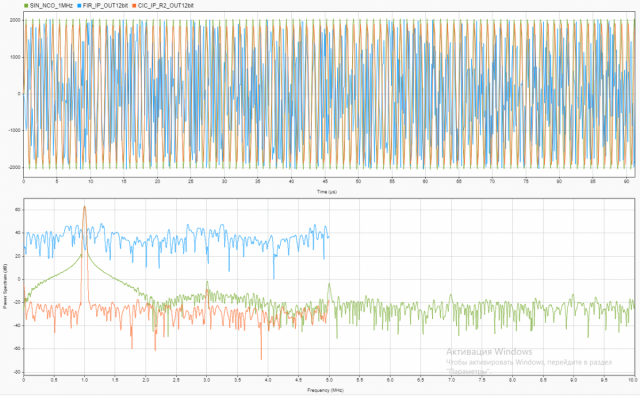

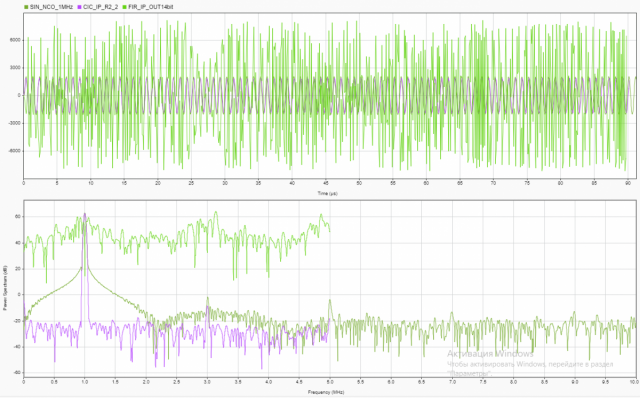

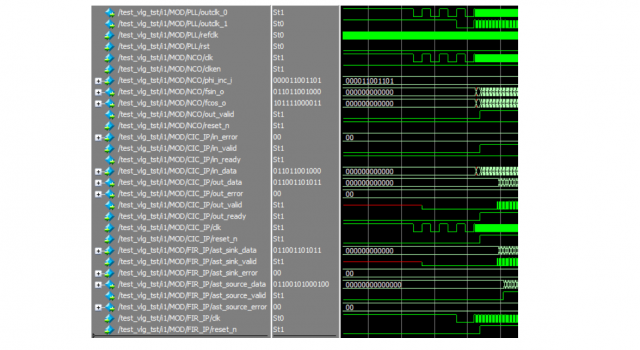

Всем доброго времени суток! Никогда ранее не обращался на форумы, но в данной ситуации ответа на свой вопрос в Сети не смог найти. Кратко введу в курс дела. Использую: 1) САПР для проектирования на ПЛИС - Quartus Prime Standart Edition 18.0.0 build 614 2) САПР для симуляции Verilog кода - ModelSim INTEL FPGA Starter Edition 10.5b Revision: 2016.10. (Данная версия поставляется вместе с Quartus на сайте https://fpgasoftware.intel.com/) 3) Для проверки результатов симуляции использую MATLAB 9.8 (2020a). В MATLAB на данный момент использую Signal Analyzer для просмотра спектра сигналов полученных в результате работы программного(-ых) модулей. Все программные модули пишу на Verilog (начал его изучать первым, на данный момент с VHDL знаком лишь отчасти). Опыт. Увлекся ПЛИС на 3 курсе университета. Специальных предметов по тематике ПЛИС на моем направлении не было, поэтому изучал все по видео/статьям/книгам/форумам. Увлечение переросло в желание написать диплом по ПЛИС. Таким образом, знаком с ПЛИС в районе 1,5 лет, из которых в учебное время не было слишком серьезных задач, а если и были, то решались они для моего уровня так, как мог их решить (костыли и тд). Вторым увлечением была ЦОС, в которой знания и опыт черпал из тех же источников, что и по тематике ПЛИС. Сейчас же появилась задача следующего плана. Занимаюсь QPSK демодуляцией. Разделим данный процесс на 3 этапа 1) Использование гетеродина для переноса на более низкую частоту. Тут все как обычно. Гетеродин и два умножителя для двух каналов (синфазного и квадратурного). 2) Децимация. Перед непосредственно реализацией дециматора окунулся в эту тематику. Знаком с статьей Hogenauer'a, а также с другой информацией на эту тему (ru.dsplib.org, dspguru.com), а также информацией с других сайтов. Имея начальное представление решил попробовать сделать, в итоге все получилось и CIC-фильтр работает так, как и ему положено. 3) Фильтрация. Компенсация искажений АЧХ после CIC-фильтра и последующая низкочастотная фильтрация. Так как в качестве САПР для проектирования на ПЛИС я использую Quartus, то было решено не использовать MATLAB без необходимости и решить задачу децимации и фильтрации с помощью встроенных в Quartus IP-ядер, а именно CIC и FIR II. В процессе работы с ядром проектирования CIC фильтра, есть возможность (ядро само сделает все необходимые файлы) сделать примерный вариант CIC фильтра, учитывая имеющиеся параметры. Одним из файлов является код MATLAB, который позволяет рассчитать коэффициенты компенсирующего FIR фильтра. В процессе выполнения скрипта задается количество и "битность" коэффициентов фильтра, а также - "FIR filter sample rate in Hz before decimation (80e6 as default): 20e6 (я указал 20 МГц)", что говорит нам о частоте дискретизации входного сигнала ПЕРЕД децимируюшим фильтром; - "FIR filter cutoff frequency in Hz (4e6 as default): 1.2 МГц". Частота среза компенсирующего FIR фильтра (в моем случае 1.2 МГц). После чего скрипт формирует текстовый файл с коэффициентами корректирующего FIR фильтра, которые загружаются позже в ядре FIR II. Исходя из коэффициентов ядро автоматически строит АЧХ,ФЧХ и ИХ получившегося фильтра. И вот мы дошли до самой сути моей проблемы. Все идет хорошо ровно до момента с компенсирующим FIR фильтром. По временным диаграммам в ModelSim (скриншот прикрепил) работа NCO, CIC и FIR фильтра прекрасна, то есть они работают и никто из них не простаивает и т.д. Ввиду того, что очень долго ковыряюсь с этой проблемой была сделана простая схема (скриншот из RTL Viewer из Quartus'а прикрепил), которая подает синусоиду с частотой 1 МГц и частотой дискретизации 20 МГц на вход CIC фильтра. Настройки CIC ядра: - Filter type - Decimator; - Number of Stages - 5; - Differential Delay - 1 cycles - Rate change factor - 2; - Input data width - 12 bit - Output Rounding Method - Hogenauer Pruning; - Output data width - 12 bit. Имея такие настройки CIC фильтр отлично отрабатывает и не искажает спектр в требуемом 1 МГц (скриншот прикрепил). Далее исходя из этих настроек был сделан скрипт, в котором задавал следующее: - Number of filter coefficients (31 as default): *оставил default значение*; - FIR filter sample rate in Hz before decimation (80e6 as default): 20e6; - FIR filter cutoff frequency in Hz (4e6 as default): 1.2e6 - Number of bits to represent the filter coefficients (16 as default): *оставил default значение*. После этого были сформированы коэффициенты и теперь надо настроить ядро FIR II. Настройки в нем задавал следующие: - Filter Type - Single Rate; - Interpolation / Decimation Factor - 1; - Clock Rate - 10 MHz; - Input Sample Rate (MSPS) - 10; - Coefficient Width - 16 bits; - Input Width - 12 bit; - Output Width - 14 bit; - Specifies whether to truncate or saturate the MSB - Truncation (аналогично для такого же параметра, но для LSB); - MSB Bits to Remove - 10; - LSB Bits to Remove - 9. Если не обрезать MSB и LSB, то на выходе ядро рекомендует ширину в 33 бита, что много и существенной разницы между 14 и 33 битами я не увидел (при увеличении доли MSB в сигнале растет мощность в дБ на спектре и все). Да, я пробовал 33 бита, однако желательно уходит от такой большой разрядности. Имея такие настройки, мы имеем следующую картину в спектроанализаторе Signal Analyzer (скриншот прикрепил). Как видно из рисунков спектр после FIR фильтра больше похож на шум, чем на что-то осмысленное. Промучавшись долго с этим ядром я решил, что необходимо попробовать сделать CIC и FIR в MATLAB и сравнить результат. При даже меньшей разрядности FIR фильтр выдал необходимый мне спектр и отработал так, как я и хотел (аналогично и CIC) (скриншот сравнения MATLAB'овского компенсирующего FIR и генерируемого ядром не смог прикрепить, однако и видно даже на первый взгляд, что разница имеется). Таким образом, вопрос. Знает ли кто-то в чем заключается проблема с FIR II ядром и почему (вроде бы нигде не ошибаясь) я получаю такой отрицательный результат? Заранее благодарю за уделенное время и оказанную помощь Что получилось загрузить

-

Приглашаем специалистов, работающих с ПЛИС и системами на кристалле, на бесплатный технический вебинар «Создание кастомного контроллера в среде Vivado». При разработке систем на кристалле на платформе Xilinx не всегда удается собрать систему только из «стандартных», то есть входящих в IP-каталог модулей. В таких случаях приходится разрабатывать собственный (кастомный) контроллер. Как организовать такую разработку наиболее эффективным способом будет рассказано и показано на вебинаре на примере контроллера PWM. Программа вебинара: создание проекта с использованием стандартного шаблона структура каталогов и файлов проекта кастомизация автоматически сгенерированных файлов добавление в проект собственных исходных файлов автономная отладка контроллера с использованием эмулятора шины обеспечение совместимости для различных серий ПЛИС задание параметров для контроллера упаковка контроллера и создание кастомного IP-ядра создание собственного репозитория и размещение в нем упакованного IP-ядра кастомного контроллера подключение IP-ядра к проекту действия при модернизации контроллера демонстрация работы IP-ядра контроллера PWM Ведущий вебинара – инженер технической поддержки (FAE) по продукции Xilinx Владимир Викулин. Вебинар состоится 11 августа в 14:00 (мск). Повтор вебинара 12 августа в 10:00 (мск). Участие в вебинаре бесплатное, после предварительной регистрации. Зарегистрироваться на вебинар Компания Макро Групп является официальным партнером Xilinx в России и странах СНГ.