Поиск

Показаны результаты для тегов 'generate'.

-

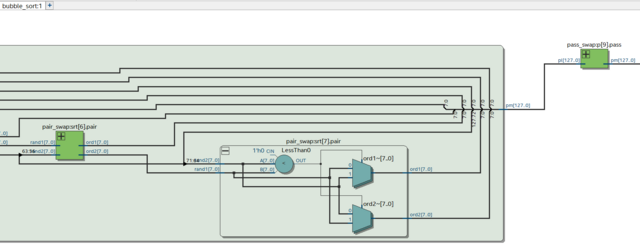

Всем привет! Тут, просто, ради интереса, довелось ответить на такой вопрос: Пузырьковая сортировка в ПЛИС "за один такт". Другими словами, только в виде комбинаторной логики, без синхросигнала и регистров. Verilog (не System). На входе и на выходе - массивы. На выходе - отсортированный. Чтобы было в общем виде, через параметры и циклы generate. Оказалось довольно интересно. Первое что поразило. Это слишком большая ошибка в оценке времени на разработку. Задача казалась очень простой. Сразу было ясно, что это будет многократное повторение простейшего модуля с перестановкой двух элементов. Сначала воспроизвёл алгоритм в perl, чтобы со стороны взглянуть на проблему. На это ушёл вечер - не считаем его вообще. Далее, накидал структуру модулей (перестановка, один проход, собственно сортировка и тестбенчи для всех) и решил что вся разработка с этого момента займёт пару вечеров... В первый вечер стало ясно, что знания по циклу generate не в один момент загружаются в голову... Пришлось поменять тактику: раскидать модули по файлам, прикрутить контроль версий. Долго-ли коротко-ли, ушло раз в 5-6 больше времени. И это довольно характерный коэффициент для меня. Просто до смешного стабильный показатель )) Это один результат, который надо ещё осмыслить )) Ну и оказалось, что этот проект интересно разглядывать через утилиты Квартуса. Особенно в процессе знакомства с generate + цикл. Очень наглядно: 1. RTL Viewer (см. скрин) 2. Timing Analyzer - путь с максимальной задержкой как меняется от размерностей массива 3. Technology Map Viewer (тут можно увидеть как всё конвертируется в таблицы истинности*) * если я правильно понимаю м.б. кому-нибудь пригодится И конечно интересны комментарии и соображения по всем задетым темам, если у кого они есть. bubble_sort.7z

-

Имеется 4 компонента сгенеренных в цикле genvar i ; // Pad out the input data bus with 0's to 8 bits to avoid errors generate for (i = 0 ; i < (CH_NUMBERS) ; i = i + 1) begin : loop_data_chanel input_channel i_channel( .clk_fabric (clock_x1), .clk_fabric_x2 (clock_x2), .clk_input (clock_x12), .serdes_strobe (serdes_strobe), .tmds_p (LVDS_p[i]), .tmds_n (LVDS_n[i]), .data_out (data_out[11+i*12 : i*12]), .frame (frame) ); end endgenerate Пытаюсь в тестбенче "вывести на картинку" сигнал wire every_other = HG_KG.dvi_decoder.i_channel.i_gearbox.every_other; Modelsim требует указать порядковый номер i_channel. Пробовал квадратные скобки - не пропускает. Почитал документацию на Modelsim. Написано что для VHDL нужно кругные скобки. Попробовал - все равно не подходит.