Поиск

Показаны результаты для тегов 'fir'.

-

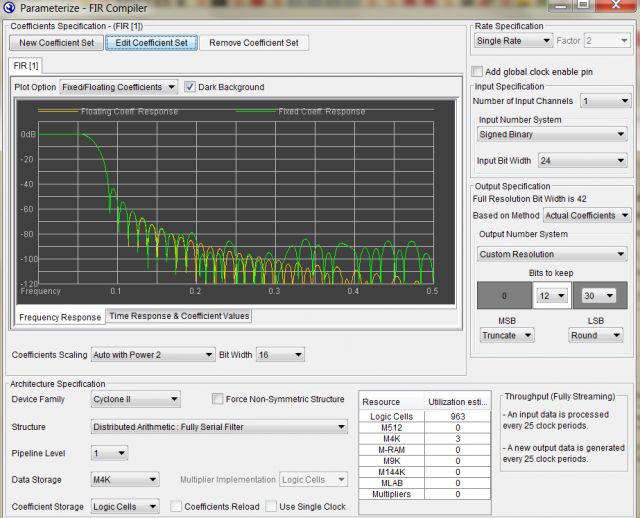

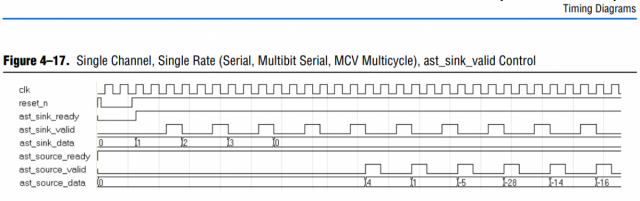

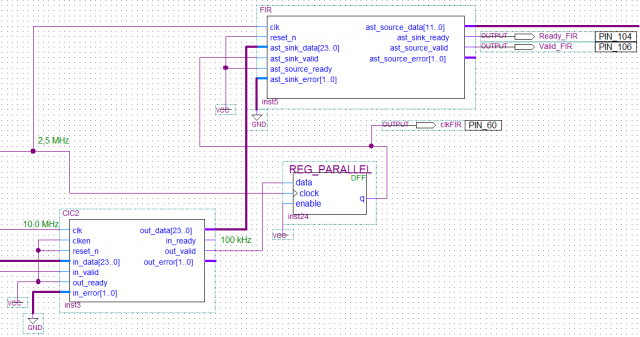

Добрый день уважаемые коллеги. В процессе разработки устройства (цифровой приёмник средневолнового диапазона) возникла проблема в конфигурации тайминга цифрового фильтра, при использовании соответствующей Мегафункции в Quartus 9.1. ПЛИС EP2C8Q208 (Cyclone II), КИХ фильтр 80 порядка, архитектура - Fully serial filter, single rate, входные данные - 24 бита (signed) с частотой 100 кГц. В FIR Compiler получаю 25 циклов CLK на один отсчёт. Согласно документа Fir Compiler User Guide устанавливаю CLK - 2,5 МГц, сигналы Reset и ast sink ready - лог."1", шина ast sink error - на земле, и ast sink valid сформировал через триггер - каждый 25-й отсчет CLK c длительностью в 1 период CLK (скважность 1/25 = 0,04) по сигналу valid от источника (CIC фильтр). Однако эти меры никак "не заводят" фильтр. При single cycle (вычисление отсчета за 1 CLK - c бешенным расходом LE) ast sink valid достаточно подтянуть к "1" и все работает... Может я что то неправильно понимаю в User Guide..? Заранее благодарен за любую помощь/пинок.

-

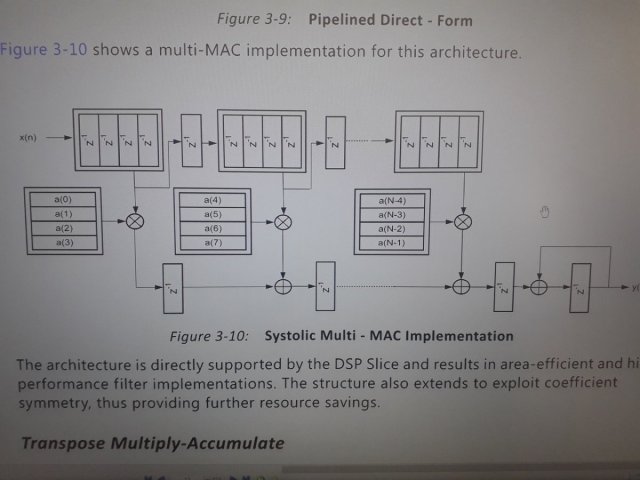

Добрый вечер! подскажите мне, начинающему инженеру-програмисту на systemVerilog. начальник дал задание: попробовать реализовать каскадную схему децимирующего, симметричного КИХ фильтра(в англ. литературе что то типа symmetric systolic multiply-accumulate filter). схема по типу той что на картинке, только с использованием предсумматора, чтобы уменьшить кол-во умножилок. это решаемая задача?? не могу даже найти схему. заранее всем спасибки!!!

- 3 ответа

-

- ких

- симметричнй

- (и ещё 4 )

-

Пытаюсь использовать в своём проекте готовый IP блок от Xilinx, а именно Fir Compiler 7.2 Пытаюсь реализовать несколько симметричных КИХ фильтров. Частота работы фильтра в 24 раза больше частоты дискретизации. Пока коэффициентов было мало - логика имплеминтации была понятна: 48 коэффициентов - 1 DSP блок 96 коэффициентов - 2 DSP блока Захотел использовать фильтр на 20 DSP блоков - 960 коэффициентов не лезет, только 912 сейчас изменил значения этих 912 коэффициентов - требует 41 DSP. Я бы хотел иметь возможность задавать разные АЧХ одному фильтру, но не понятно для чего ему дополнительные DSP.