Поиск

Показаны результаты для тегов 'clock gating'.

-

Обработка асинхронного сигнала

dips11 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

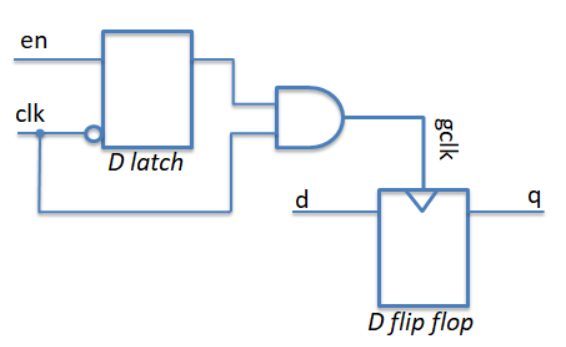

Доброго времени суток. В даташитах на микросхемы иногда встречается момент, где говорится примерно следующее: если сигнал ST придёт до 5 сигнала CLK, то микросхема перейдёт в такое-то состояние, а если после 5 и до 10 CLK то в такое-то. Причём не сказано за какое минимальное время до 5 CLK должен прийти сигнал ST. То есть сигнал полностью асинхронный. И мне интересно как может происходить обработка этого сигнала в микросхеме, ведь так как сигнал асинхронный нельзя просто использовать условие: always@(posedge CLK ) if(cnt==4 && !ST) reg0<=1; И возможности синхронизировать его нет. По сути задача может звучать как "надо определить какой сигнал приходит раньше ST или 5 CLK". Вот основные варианты, которые удалось найти. 1) Использовать сигнал ST как асинхронный сброс триггера. Если сигнал ST придет раньше то он сбросит триггер и не даст ему установиться, но как не достаток решения, если сначала придет 5 CLK то триггер установиться в 1, но потом все равно сброситься по сигналу ST и не сохранит свое состояние. always@(posedge CLK or posedge ST) if(ST) reg0<=0; else if(cnt==4) reg0<=1; 2) Использовать clock gating, то есть по сигналу ST отключить тактовую частоту. Если сигнал ST придет раньше 5 CLK то он заблокирует тактовую частоту для триггера, и он не установиться в 1, если позже пропустит. Где то встречал, что такое решение может вызвать метастабильное состояние. Это правда? Просто я вижу здесь либо наличие сигнала clk_gate для триггера либо его отсутствие. Элемент "И" ведь не должен выдавать шумов. assign clk_gate = CLK & !ST; always@(posedge clk_gate ) if(cnt==4) reg0<=1; Еще встречается реализация с защелкой. И говориться,что защелка добавляется для устранения glitch, так как такая схема будет пропускать сигнал ST только при низком значении CLK и его изменение не вызовет переключение выхода "И". Другие варианты являются производными от этих. Я был бы благодарен за советы, по тому как возможно правильно решить такую задачу. Возможно я вообще не там ищу. Спасибо.- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом: