R2R

Участник-

Постов

43 -

Зарегистрирован

-

Посещение

Весь контент R2R

-

QUARTUS, MODELSIM

R2R ответил aosp тема в Среды разработки - обсуждаем САПРы

Приветствую! Не получается корректно подключить мегафункцию в Quartus Prime 18.1 Lite Edition. Создаю проект в Quartus. Добавляю корневой verilog файл, тестбенч, настраиваю пины. Компилирую с Icarus-verilog, моделирую в GTKWave, синтезирую схему в Quartus - все ок. Далее пытаюсь подключить мегафункцию altsqrt из IP catalog - все настройки по умолчанию, на выходе получаю sqrt.v, sqrt_bb.v, sqrt.qip, graybox_tmp/. Использую мегафункцию в корневом модуле - схема синтезируется. Правлю тестбенч, компилирую - "error: Unknown module type: sqrt". Прописываю в корневом модуле `include "sqrt.v", компилирую - "error: Unknown module type: altsqrt". Копирую в папку проекта altsqrt.v из C:\intelFPGA_lite\18.1\quartus\eda\fv_lib\verilog, в sqrt.v прописываю `include "altsqrt.v". Симуляция запускается, но результат некорректный - у altsqrt модуля при 25 на входе z на выходах. Схема перестает синтезироваться в Quartus - "Warning (12090): Entity "altsqrt" obtained from "altsqrt.v" instead of from Quartus Prime megafunction library", "Error (10228): Verilog HDL error at altsqrt.v(14): module "altsqrt" cannot be declared more than once". -

Цепь ОС в автогенераторном инверторе

R2R опубликовал тема в Индукционный Нагрев - Induction Heating

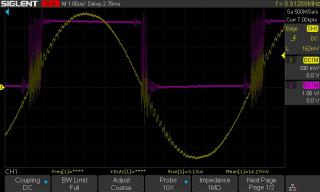

Приветствую! Собрал полумостовой индукционный нагреватель с задающим генератором на триггере Шмитта. Решил переделать его в автогенераторный, спаял новую плату контроллера и, чтобы проверить ее работоспособность, подключил к инвертору через токовый трансформатор в первичке согласующего трансформатора. Обнаружил, что сигнал обратной связи с трансформатора тока получается слишком шумным (канал 1 на осциллограмме) и вызывает ложные срабатывания компаратора (канал 2). Как в данном случае избавить сигнал от помех? НЧ фильтр не подходит, т.к. вызывает изменение фазы сигнала в рабочем частотном диапазоне, что недопустимо для автогенератора. Замена компаратора на триггер Шмитта также не годится, потому что потребуются бОльшие токи, чтобы запустить генерацию (хотелось бы, чтобы схема могла работать в диапазоне от 2 до 200 А на входе ТТ). -

Подключение нагрузки к CPLD

R2R опубликовал тема в В помощь начинающему

Приветствую. Использую в своем проекте EPM240T100C5N. Для увеличения нагрузочной способности объединил выходные пины в 4 группы по 3 шт., формирующие дифференциальные сигналы (300 кГц), которые подаются через дроссели ACT45B на трансформаторы B78421A1720A003. На выходе ненагруженных трансформаторов получил сигналы ± 0,5 В. Выпаял дроссели, посмотрел сигналы - амплитуды те же. Перепрошил CPLD (код не менял) - сигналы ± 3,3 В. Соединил пины с трансформаторами перемычками - амплитуды снова просели до ± 0,5 В. В чем может быть проблема? -

Покритикуйте трассировку

R2R ответил R2R тема в Примеры плат

Что касается тепловыделения, тут закралась ошибка - рассчитал не на то входное напряжение. При 23 В будет перегрев 100 град - надо ставить импульсник. Футпринт испытан в деле - запаивал туда D2PAK и даже TO-220, подготовленный соответствующим образом. Как я понимаю, размещение переходных отверстий в контактных площадках чревато технологическими трудностями - банально может затянуть припой в отверстие и будет непропай. Есть методы, позволяющие обойти эту проблему, но проще сделать несколько отверстий по краям площадки. В моем случае плата изготавливается в домашних условиях, а межслойные соединения обеспечиваются проволочными перемычками, поэтому любой вариант размещения может быть использован. Впрочем, исправлю на рекомендованный. Перемычка R14 типоразмера 0805. Зазоры там не менее 0,15 мм - они держат 25 В, согласно ГОСТ 23751-86, если Вы про это. Входные и выходные сигналы ПЛИС имеют частоту не более 500 кГц (клок 100 МГц). Ну заработает оно однозначно, однако для меня сложность этого проекта в том, чтобы ограничить шумы на входах компаратора до 5 мВ. Полигоны земли соединяются на контакте GND выходного конденсатора AMS1117. 100 мкФ на выходе диодного моста это даже перебор - на входе же постоянное напряжение, а не 50 Гц с трансформатора. Здесь гораздо важнее то, что это обычные (не "Ceramic Stable LDO") линейные стабилизаторы, которым требуются выходные конденсаторы с большим ESR для устойчивой работы. ДШ на AMS1117 рекомендует использовать тантал минимум на 22 мкФ, однако керамика с большой емкостью (и, соответственно, с большим ESR) также может быть применена. Если не прав, поправьте (по крайней мере, для этих стабилизаторов 100 мкФ дает хороший результат). Если не затруднит, перечислите, пожалуйста, (без пояснений) те вещи, на которые также стоит обратить внимание. -

Покритикуйте трассировку

R2R ответил R2R тема в Примеры плат

Где-то 1,6 Вт выходит - около половины от максимальной мощности, рассеиваемой D2PAK. Не разделяю Ваших опасений по поводу потребляемой мощности - для данной задачи это требование не в приоритете. -

Покритикуйте трассировку

R2R ответил R2R тема в Примеры плат

Два стабилизаторы включены последовательно только потому, что у меня в запасах горы L78XX и AMS1117-3.3. Последняя имеет максимальное входное напряжение 15 В, поэтому не может быть использована здесь самостоятельно. Также L78XX в D2PAK рассеивает все потери мощности, чего не сможет AMS1117-3.3. То, что вариант с одним стабилизатором на нужные характеристики лучше, думаю, ни у кого сомнений не вызывает. Хочу сразу прояснить один момент - на схеме не все номиналы правильные (что-то проверенное взял с предыдущих проектов, а что-то добавил, но не успел посчитать). Это на тот случай, если у кого-то возникнут замечания по функционированию. С запуском МК никаких проблем нет - ранее я делал макетку для этого же проекта, которая отличается отсутствием аналоговой части и супервизора, и наличием измерительных контактов. -

Покритикуйте трассировку

R2R ответил R2R тема в Примеры плат

Ага, первая плата и сразу с МК и ПЛИС. А схема чем не угодила? Я даже не выкладывал ее описание, а Вы уже решили, что она не годится. :rolleyes: Вии с термопадами здесь реально вредны, я упустил этот момент. А чем плохи вии в падах капов, минимальный импеданс же получается, нет? Тирдропы плохо вышли (их совсем недавно начал применять) - надо менять настройки. С разделением земель я как раз хочу разобраться. Без аналогового узла все было бы предельно просто - один сплошной земляной полигон. Но здесь есть аналоговые сигналы (в качестве ИОНов компаратора), подверженные помехам от цифровых цепей. При трассировке придерживался двух правил: 1) соединять земли звездой, чтобы устранить помеху через общий импеданс; 2) прокладывать возвратные проводники рядом с прямыми (вести оба проводника в одном слое рядом параллельно или один в верхнем слое, а другой в нижнем - прямо под ним), чтобы минимизировать восприимчивость и эмиссию помехи. К сожалению, без проблем не обошлось - пришлось разделить цифровой полигон, чтобы добраться до силовой земли. Получается, что проводник аналоговой земли проходит под шиной SPI, заставляя ее возвратные сигналы проходить по периметру прорези в цифровом полигоне - явное нарушение 2-го правила. Ничего лучше я не придумал, надеюсь на ваши советы. А что еще можно поправить? -

Покритикуйте трассировку

R2R опубликовал тема в Примеры плат

Приветствую! Вот один из моих проектов - покритикуйте трассировку, пожалуйста. Особый интерес представляет аналоговый узел с компаратором DA3 - возвратные (земляные) проводники контуров входных сигналов (FB, OCD) и полигон аналоговой земли соединены звездой на пине GND компаратора. Полигоны аналоговой и цифровой земель соединены звездой на GND выходного конденсатора стабилизатора напряжения. В архиве проект в Altium Designer 15, а также схема и печатка в pdf. SRHBIC_v.1.0.rar -

Спасибо за пояснение. Фазокорректор для автогенераторного инвертора - компенсирует задержку распространения сигнала ОС.

-

А откуда берется еще 40 нс дребезга, когда сигнал проходит основную часть схемы?

-

-

Вариант с == проверял - то же самое. Насчет логики работы модуля - он измеряет полупериод и по фронту сигнала загружает измеренное значение, уменьшенное на phase, в счетчик нового полупериода. Увеличивая phase, можно сдвигать сигнал влево, т.е. модуль формирует сдвиг T - phi. Как мне казалось, это самая очевидная реализация такой функции.

-

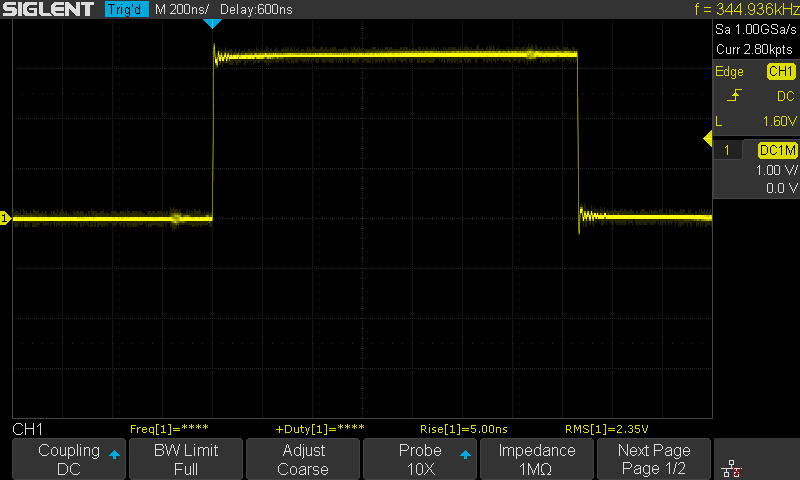

Осциллограмма внешнего сигнала в сообщении #3.

-

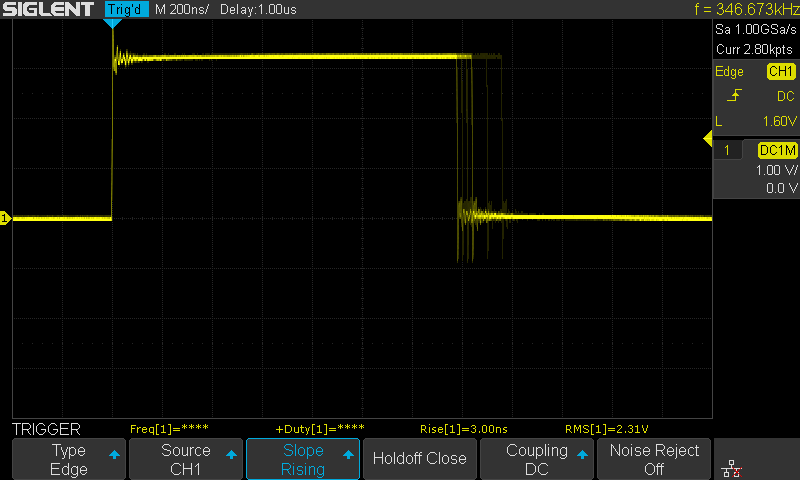

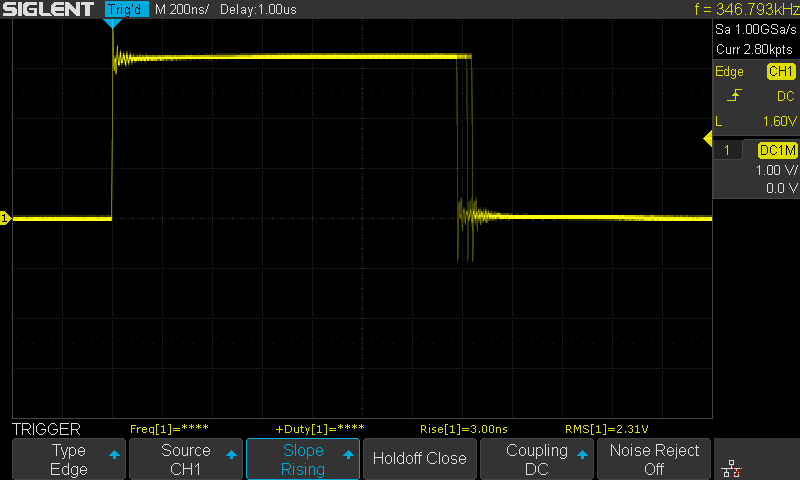

Поспешил с выводами - дребезг сигнала уменьшился, но не исчез (логический анализатор не позволяет это оценить в полной мере в отличие от осциллографа). Выходной сигнал без синхронизатора С одним триггером С двумя триггерами Как видно, между синхронизаторами с одним и двумя триггерами нет разницы - дребезг ощутимо большой и составляет около 60 нс (3 такта клока).

-

1. Сигнал достаточно чистый - фронты около 5 нс с минимальным звоном. 2. Внешний сигнал не сихронен с тактовым генератором ПЛИС. Действительно, проблема была в метастабильности и оказалась решена двумя триггерами на входе. Благодарю.

-

Приветствую! Написал на верилоге модуль, осуществляющий задержку входного сигнала. Для его проверки в той же ПЛИС (EPM240T100C5) сделал модуль генератора меандра, посмотрел сигналы - все работало правильно и стабильно. Потом взял сигнал от внешнего генератора - появились баги. После нескольких попыток оптимизации кода добиться корректной работы схемы так и не удалось. module delay ( input wire clk, input wire sgn, output reg out ); localparam phase = 10; reg[7:0] pos_cnt = 0, neg_cnt = 0; always @ (posedge clk) begin if (sgn) begin pos_cnt <= pos_cnt + 1; if (neg_cnt > phase) neg_cnt <= neg_cnt - 1; else begin neg_cnt <= 0; out <= 1; end end else begin neg_cnt <= neg_cnt + 1; if (pos_cnt > phase) pos_cnt <= pos_cnt - 1; else begin pos_cnt <= 0; out <= 0; end end end endmodule

-

Совсем забыл про настройку неиспользованных пинов :) . Указал Float в Generate Programming File - Process Properties - Configuration Options - Unused IOB pins и все получилось. Спасибо.

-

Приветствую! Начал осваивать ПЛИС: приобрел отладочную плату с XC6SLX9, установил ISE 14.7. Сначала проверил исправность программатора и камня, использовав готовые прошивки (из архива с материалами по ссылке) - все работало. Потом сделал проект с нуля (переключение светодиода кнопкой), но в ПЛИС записался какой-то мусор - горели все светодиоды, звенела пищалка, слегка светились семисегментники. Попробовал собрать проект, используя исходники одного из проверенных проектов в архиве - результат тот же. Снова загрузил готовую прошивку - работает. Похоже, что у меня неправильно генерируется прошивка. Но из-за чего это происходит? Использую следующий алгоритм: 1. Создание проекта; 2. Создание описания на Verilog; 3. Создание файла описания выводов с помощью PlanAhead (pre-synthesis); 4. Создание прошивки опцией "Generate programming file".

-

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

Вернулся к первоначальному варианту схемы за исключением дополнительных конденсаторов по питанию микросхемы и резисторной цепочки, перекинутой на выход. Корректор запускается где-то спустя полсекунды после включения в сеть, термистор не вылетает, провалов напряжения по питанию микросхемы нет. Всем спасибо. -

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

C7 был. В силовом контуре меня только термистор смущает. -

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

Попробовал после запуска генерации сделать разрыв между R11 и C9, C10 - сигнал по питанию микросхемы перестал проваливаться. Фазировки обмоток правильные. На конце силовой обмотки T1 положительные полуволны, а на началах дополнительных обмоток - отрицательные полуволны. Т.е. эти обмотки работают как в обратноходовом преобразователе. Вообще похоже, что когда на выходе моста ноль, ток с обмотки самозапитки течет на вход через R5, R10, R11. В таком случае диод в резисторной цепочке должен помочь. Как можно объяснить сгорание BYG23M, который я поставил перед R5? -

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

10 мс - 100 Гц - выпрямленный синус. По осциллограмме видно, что он промодулирован ШИМ сигналом. Если бы генерации не было, то на этой обмотке наблюдались лишь короткие всплески от попыток контроллера эту самую генерацию запустить. -

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

Ну если бы оно не работало, то на обмотке питания микросхемы не было этих модулированных полуволн :). Хотя 300 мкФ для контроллера - мягко говоря, многовато. Завтра попробую взять контроллер в другом магазине. -

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

-

ККМ на MC33262

R2R ответил R2R тема в Силовая Преобразовательная Техника

В дежурном режиме микросхема потребляет менее 1 мА. При работе наблюдаются короткие провалы напряжения до нуля. Сигнал на C10 Сигнал на аноде VD6