go2winner

Участник-

Постов

77 -

Зарегистрирован

-

Посещение

Весь контент go2winner

-

SOVA Алгоритм Витерби с мягким решением

go2winner опубликовал тема в Алгоритмы ЦОС (DSP)

Доброго времени суток, Прошу Вас скинуть книги/статьи по принципу алгоритма Витерби с мягким решением. Не могу ни как найти. Если есть хорошие статьи с способом реализации тоже буду признателен. Алгоритм Витерби реализовал с жестким решением. Считает конечно не шустро. Поэтому если есть примеры буду им рад, но это второстепенно -

Вопросы про PCI

go2winner ответил go2winner тема в ISA/PCI/PCI-X/PCI Express

Спасибо. Учел. Скоро платы приедут начну тогда пробовать работать с pci -

Немного не то. Я имею в виду следующее. Пример. Пусть схема уже работает. Через некоторое время по опр. условию мне надо привести счетчик в начальное состояние. Я могу сигнал это сделать двумя путями. Через сигнал ресет, общий ресет и ресет счетчика от управления через логику пропустить и подать на сброс счетчика. Могу добавить сигнал Load. И путем его использования приводить счетчик в исх. состояние. Тоже самое с крупными модулями ( к примеру приемник и т.п.). Вопрос такой. Является ли корректно на вход ресета подавать сигал пропущенный через логику.

-

Первоначальное состояние

go2winner опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Как лучше дизайн строить. Есть ситуации когда модуль нужно приводить в первоначальное состояние ( иногда счетчики, иногда модули ). Считается ли правильным решением пустить reset и управляющий сигнал через "или" и подать выходной сигнал на вход сброса модуля / счетчика/ ect.? Или есть более красивые варианты? -

Вопросы про PCI

go2winner ответил go2winner тема в ISA/PCI/PCI-X/PCI Express

Про длину понятно, это уточнял в спец. все понятно. А длина трассы общая учитывается КОННЕКТОР->БУФЕР->ПЛИС и она 2.5? С адресными так же? Или все ограничения до первой микросхемы?(буфера)? Я пока пытаюсь подогнать под то, чтобы вся трасса ( КОННЕКТОР->БУФЕР->ПЛИС ) попадала под ограничения.. -

Вопросы про PCI

go2winner опубликовал тема в ISA/PCI/PCI-X/PCI Express

Доброго времени суток, имеется вопрос. У PCI есть ограничения на длину трассы клоковой и сигналов. Вопрос, как ведется отсчет длины трассы? От верхней кромки коннектора? У меня стоят буферы(QS3861 подобные) между коннектором и ПЛИС. Длина PCI на сигналы имеется в виду до от коннектора до ПЛИС или от коннектора до буфера? 2. Ограничения на количество слоев ПП есть? Очень часто вижу упоминания в 4 слоя, это связано с удобствами разводки или есть ограничения? -

PCI

go2winner опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток, Есть задача, необходимо обмениваться с пк с целью передачи управляющей информации на устройство сопряжения и получения ответной посылки. И управляющие посылки и ответные по объему не большие и содержат служебную информацию. Ядром устройства сопряжения FPGA от xilinx. Конструктивно удобно выполнить данное устройство, как плату расширения, которая помещается в пк. Предварительно решили для этого использовать PCI слот. Сей час хочется заложить возможность для того, чтобы в будущем обмен вести по этой шине, а уже потом по мере изучения переключиться на нее. Отсюда вопросы, что необходимо и достаточно для того чтобы проводить обмен пк-плата сопряжения по PCI. 1) Схемотехника. Т.к. нужно заложить в плату, т.е. сей час схематехника кретина. Что и себя представляет на данном уровне абстрации? Я так понимаю достаточно самого плис с коркой pci? или отдельно ставить phy? Есть ли примеры проектов? ЧТо необходимо учесть в схемном решении, чтобы не пришлось глобально переделывать? Можно в приципе ссылки на статьи и литературу кидать.. 2) Хватит ли спартана 3 с 400к вентилями ? 2) Обмен на позльзовательском уровне. Как я смогу получать и передовать данные плате? Через порты ввода/вывода пк? или ? В основном интересует сей час схемотехника плис - pci. Т.к. с самим обменом pci буду работать по мере его изучения. -

Спасибо всем за ответы. !

-

Доброго времени суток, я пока использую ISE, т.к. под рукой плата есть с спартаном 6. Но в сторону вивадо тоже смотрю, уже начинаю с ним знакомиться. Для тестирования буду использовать modelSim. Ну как синтезатор - саму среду ISE/ViVado. Вчера ночью я исправил свои ошибки. Полазив по форуму нашел схожую ошибку/ошибки: 1) Иногда вычитаю/ прибавляю и т.п. целые числа, без указания размерности, что интерпретируется как целое число. Синтезатор приводит правую часть к 32 разрядам, потом грозиться обрезать их под левую часть 2) При написании параметрических модулей опять параметр использую в правой части без указания размерности, что приводит к предупрежденям, к примеру: parameter devider = 4; output reg [ $clog2( devider * 3/2 ) - 1 : 0 ] loadValue; always@(*) begin // какое-то описание loadValue = devider*3/2; end Тут я правильно понимаю, что или разрядность всего выражения правой части необходимо указать явно или его операндов? Без указания возникают предупреждения. loadValue = devider*(3'd3)/(2'd2); 3) Глупые ошибки из серии в одном месте сделал ресет по другому фронту. Кстати, катируется ли локально на некоторых модулях управлять ресетом? К примеру счетчик. Хочу чтобы он был сброшен в определенные моменты. Не страшно ли управлять ресетом, пропустить через логику? Я понял про доступ к переменной/сети в тестбенчах, которые находяться в нижних уровнях иерархии. Но как получить доступ в синтезируемой схеме. Вдруг мне понадобиться использовать сигнал, который на нижнем уровне и вывести его на котрольную точку, для синхронизации или т.п. мало ли. Тут только переписывать все интерфейсы до высокого? Но вот с начальным значением в среде попробую уже сам. В доках синтезатора указано, что или при объявлении или через блок init. Просто я схематехнически не представляю, во что выливается начальная установка? Reset я использую однозначно. Пока что синхронный, т.к. ассинхронный следует более внимательней вести. А так пойду на новую иттерацию обучения. Скачал еще пару книжек и примеров.

-

Трудности перехода на verilog

go2winner опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Перешел на verilog. Прочитав пару книг, цикл статей Иосифа К. и т.п., решил написать для проверки UART. Во- первых, постоянно warning`и выдаются, то разрядность операции больше и ее значение будет обрезано до разрядности левой части, то другие мелочи..раздражает. На VHDL все warning мне были понятны и отностительно быстро устранялись, так чтобы проект компилировался с минимумом или без них. А тут на простых вещах выдается. То сигналы с целью оптимизации вырезаны. Описание проекта и предупреждения синтезатора выложу завтра. Сей час хочу обсудить общие вопросы. 1) Как инициализировать все биты единицами или нулями? 2) Где можно найти парамтрические описания или примеры устройств с хорошим стилем написания? ( вот сей час опенкорс открыл) 3) Жуткие проблемы с тестбенчами, пишу деревянно. Буду очень признателен за ссылку на литературу/паттерны/статьи с хорошими примерами тесбенчей на этом языке. 4) Пишу под xilinx. Там есть синтезатор XST. Как я понимаю я могу задать начальное значение регистров( из доков самого синтезатора и кристалла). Вопрос, как граммотно это делается и во что синтезируется схема с начальным значением, к примеру сдвигового регистра. 5) ОБЩИЙ. порой нужно выводить контрольные точки из нижних уровней иеархии. Как на verilog/vhdl проделывают данный трюк не мучаясь, добавляя в интерфейс сигналы. В данный момент я в замешательстве. Хотелось овладеть данным языком, т.к. очень удобен, да и в общем.. Но уже второй день совсем не идут дела. Поэтому приму толковые советы. -

Добрый день. Есть сигнал с возможным периодом от 2,5 мс и длительностью импульса от 0,5 мс ( последовательность прямоугольных импульсов ) Нужно выяснить уровень сигнала( значение напряжения импульса ). С какой частотой дискретизации нужно брать отсчеты ( мне кажется можно где - то с 20 - 25 кГц будет нормально )? Есть ли отечественные ацп, подходящие под данный случай (на сайте миландра видел два ацп, один высокоскоростной, второй под 8 Мгц максимальная частота )? Как должна выглядеть входная цепь( имею в виду фильтр) для такого измерения? Или можно без него?

-

ФАПЧ

go2winner опубликовал тема в Алгоритмы ЦОС (DSP)

Нужна литература/реализация/модель ФАПЧ. Она должна иметь астатическую ошибку по фазе. Мне пока не удалось найти толковую литературу по цифровым фапч с астатизмом по фазе. Мне нужен квадратурный фапч( сигнал на входе представлен в виде комплексной огибающей) Есть ли типовая схема? Стать? и т.п.? Больше всего интересует астатизм и условия устойчивости.. Из толковых книг под рукой, Шахгильдян, Незами, пару стетей.. -

Не работает проект

go2winner ответил go2winner тема в Языки проектирования на ПЛИС (FPGA)

Может быть....но не уверен...я защелки по крайней мере не описывал..и в синтезаторе на схеме пост синтез не наблюдал( на память) Но сей час еще раз гляну. Глянул. Нету . Только д-тригеры -

Не работает проект

go2winner ответил go2winner тема в Языки проектирования на ПЛИС (FPGA)

Проблема не в этом..... Проблема в том, что я описал блок,а он непонятно( для меня) почему не работает. Я осциллографом смотрел , ничего не увидел на выходе , даже тактовых для SPI. Начал выводить сигналы и дошел до этого куска. Думаю отправка хосту убьет лишь время, т.к. если модуль не работает( основной автомат вообще не работает/прием/передача/инийиализация ), то и отправлять нечего. Вот пример выше приводил модуля управляющего (подает SPI флаги начало передачи и выборку из памяти байтов для SPI на передачу). Он не работает, причины не понятны мне, в какую сторону смотреть тоже. ЗЫ. сам SPI еще не проверял, только автоматы для работы с микросхемой(иниц/чтени и т.п.)...боюсь , что он тоже наверное не работает. -

Не работает проект

go2winner ответил go2winner тема в Языки проектирования на ПЛИС (FPGA)

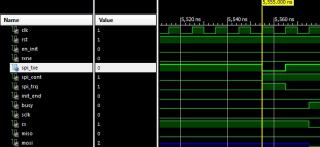

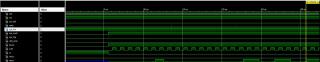

Затрудняюсь..данный автомат (spi_init, который тут выложил), он синтезировался бюез единого замечания, но если часть ног повешу на пост уровень( см.код rxne => '1',), начинает часть схемы резать, якобы все константное( счетчики/память и т.п. ). Взял тогда входы( busy, rxne . . ) вывел на ружу, на переключатели( код не приведу ибо он такой же). Без ошибок синтезируется и предупреждений. Он же опять таки проходит поведенческое симулирование, заваливает пост мап и в жизни не ловиться осцилограффом те сигналы которые должны( spi_txe, spi_txrq). Из констрейнов задал только на глобальный клок, его частоту и заполнение. Все это сей час проделал на отладочной при клоке 50 МГц. Для этого создал топ модуль...в иделале ...он хотябы один раз должен флаг spi_txe, spi_trq дернуть.а на выходе, что в пост мап, что в жизни постоянный уровень...только поведенеское симулирование сработало: entity state_init_debug is port( clk : in std_logic; rst : in std_logic; spi_txe : out std_logic; spi_cont : out std_logic; spi_trq : out std_logic; init_end : out std_logic; tx_data : out std_logic_vector( 8 -1 downto 0 ) ); end state_init_debug; architecture Behavioral of state_init_debug is COMPONENT state_init is generic( cnt_max : integer := 48; -- количество байт памяти cnt_max_delay : integer := 512; -- задержка data_width : integer := 8; g_cmp0 : integer := 16; -- пороги сравнения для начало новой порции передачи g_cmp1 : integer := 30; -- пороги сравнения для начало новой порции передачи g_cmp2 : integer := 48; -- пороги сравнения для передачи последнего пакета rst_active_lvl : std_logic := '0' ); port ( clk : in std_logic; rst : in std_logic; en_init : in std_logic; rxne : in std_logic; busy : in std_logic; spi_txe : out std_logic; spi_cont : out std_logic; spi_trq : out std_logic; init_end : out std_logic; tx_data : out std_logic_vector( data_width -1 downto 0 ) ); End component; begin unit1: state_init port map ( clk => clk, rst => rst, en_init => '1', rxne => '1', busy => '0', spi_txe => spi_txe, spi_cont => spi_cont, spi_trq => spi_trq, init_end => init_end, tx_data => tx_data ); end Behavioral; Подаю rst. нет изменений, репрограю , нет имзенений, щелкаю switch кнопки(флаги) не работает.....беда. На отладочной rst от кнопки завел, чтобы проверять. Просто не представляю что творится. Работают только делители и пару еще простых вещел. Автомат лежит -

Не работает проект

go2winner опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго времени суток. Я описал проект, который управляет контроллером CAN. В итоге после симуляции я его вставил в схемный проект и загрузил его на ПЛИС. По логике работы, в начале модуль должен был по SPI сконфигурировать контроллер. Этого не произошло. Модуль работает совершенно не верно. Тогда я создал на отладочной плате верхнего уровня проект и вывел контрольные точки. Все равно не работает. Симуляцию поведенческую прошел. Пост мап уже нет. Ошибки находил, но не помогло (rom описал через сигнал , а не константу.) Ну и вопрос. Как найти ошибки? Как исправить? и почему симуляция поведенческая прошла, а модуль даже близко не заработал , как в симуляции??? Исх. данные: Клок 50 Мгц на отладочной( на основной плате 100 ) Взял из этого модуля автомат для инициализации, отдельно начал тестить. Пост мап симуляцию не проходит. Кидаю сюда сам конечный автомат + обвязка. Может быть я что - то не то делаю. У меня вообще по нулям, по идеям и вообще со всем.. Логика автомата такая: после сброса автомат получает сигнал en_init и включает счетчик, который выбирает из памяти байты для отправки по SPI. Так же выдает управляющие сигналы для SPI( spi_txe -данные на входе есть, один такт, spi_trq - запрос на передачу.). После того , как spi отправил байт он возвращает флаг rxne( один такт, флаг завершения принятия посылки и готовности к следующей транзакации ). Входы cmp - означают конец первого приема/передачи ( это нужно чтобы запись следующая с нового адреса началась ). CMP_END - конец передачи. Тест бенч не прилагаю( удалил видимо, приложу симуляцию модуля по выше, если надо заново напишу тб) Этот автомат - часть большего автомата. Он работает в самом начале , после снятия rst. Топ модуль state_init. Остальные - компоненты. ( есть слабые коменты, то по смысле большая часть понятная( счетчки/сравнение)) Еще раз ..симуляцию проходит, но после загрузки не работает ничего( пост мап тоже не прошел симуляцию). В основном управляющая логика не работает, в частности данный модуь... В чем может быть причина? state_init.vhd rom_init.vhd counter_simple.vhd counter.vhd control_init.vhd compare.vhd -

Я еще все ваши сообщения не прочитал. Но разъясню, что нужно. Stm и т.п. это прекрасно. На входе относительно медленного ацп сигнал, типо ШИМ. В самом худшем случае у него длительность импульса около пол мкс, а скважность около 100. Информационный параметр для меня - уровень импульса ( ампилитуда ). Параметры ШИМ резко сами не изменяются. Т.е. задача такая, каким уже проверенным схемотехническим приемом можно узнать апилтуду, при медленном АПЦ( ацп считаем уже выбран ). ( у меня есть идеи , но хочется послушать чужие.)

-

Но есть же, так сказать, щаблоны/паттерны , контсрукции... ? Как можно с ними ознакомиться( есть ли литература) мне интересно посмотреть и прочитать про реализации модуляторов.... К примеру, вот взять модулятор сигнала MSK на основе FPGA. Какую роль выполняет FPGA? Как происходит повышение частоты? Как тракт выглядит от fpga до передающего устройства? К примеру, я так понимаю, fpga на выходе формирует НЧ огибающую сигнала, потом происходит перенос сигнала на несущую. Но Я все это представляю на сбтрактном уровне. А хочется понять хотя бы на увроень ниже.

-

Способы передачи информации на ПК

go2winner опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток уважаемые форумчане. До сегодняшнего дня для связи с ПК я использую преобразователи интерфейсов( всем известные FTDI и т.п. ). У меня вопрос. Каким образом в промышленной среде или около промышленной( в плане не дома на коленке ) связывают данные с FPGA и ПК? 2) Можете посоветовать способ связи с пк, который можно попробовать реализовать( начнем с менее сложных вариантов ) PS. Конечно хорошо уметь пользоваться микросхемами от ftdi и т.п., но я хочу расширить свои знания. -

Добрый день. Меня интересует общая информация о том, каким образом сей час формируют сигналы с помощью FPGA. Возьмем , к примеру, MSK, GMSK и т.п. более интересные способы модуляции Какую роль берет на себя FPGA при формировании сигналов (скремблер/кодер/модулятор)? и в чем выигрыш от FPGA модулятора против процессора при использовании DDS? Как происходит ЦАП( преоразование ). ? Есть ли литература по данным вопросам( реализация модемов / демодуляторов ) практическая, включая схемные решения? Используются ли DDS при этом и как активно? На сколько сложным будет реализация модулятора плане схемотехники?

-

Имеется сигнал шим, с коротким импульсом( порядка нескольких микросекунд ) и большой скважностью ( 100). Измеряемый параметр - уровень импульса( амплитуда ). Какое схемное решение наилучшим образом может проинтегрировать данный сигнал( получение постоянной состовляющей(медленно изменяющейся), равной уровню сигнала), для дальнейшей оцифровки?

-

Схемотехнический проект VHDL

go2winner опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго времени суток. Вопрос такой. Если есть схемотехнический проект, можно ли в него вставить VHDL модуль? Если да, то подскажите примерные шаги. Можно ли редактиворвать модуль при этом? Кстати, возможно ли симуляция схемотехнического проекта? И комбинированного? Если не сложно , объясните в двух словах ( можно более подробно ) Среда ISE. Вопрос в догонку. Есть много опенсорс открытых контроллеров. Какой больше подойдет для управления контроллером шины кан? На спартан 3 . Спасибо за внимание -

SAF-XE167F

go2winner опубликовал тема в Все остальные микроконтроллеры

Доброго времени суток. Вот сел за МК от фирмы infineon. До этого сидел на stm arm. Ни как не пойму с чего начать. Документацию скачал, но после stm arm она очень туго идет (в стм документация очнь легко читалась и нужная информация быстро находилась,). В какой среде IDE работь? Я так понял есть DAVE и keil. Dave- генерирует код (инициализация и шаблон, чем то на генераторы stm похожи)....ну а в Keil уже пишем.. Есть ли примеры программ подобных мк? Есть ли библиотеки? В общем нужная помощь в начале работы ..пока сижу среду и документацию разбираю...некоторые примеры имеются -

Модель ФАПЧ matlab

go2winner опубликовал тема в Алгоритмы ЦОС (DSP)

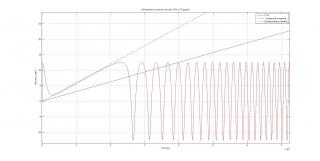

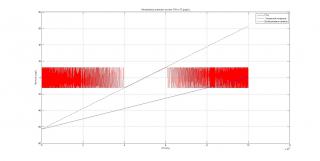

Доброго времени суток. На основе литературы я составил для начало простую модель ФАПЧ на нулевой частоте, зависающую только от расстройки ( разности частот генераторов ) Написал простую модель на matlab для закрепления теории и дальнейшего усложнения (см. приложение). Коротко о модели: модель построена на нулевой частоте и зависит только от разности частот и полосы удержания (входные параметры). При исследовании полос удержания и захвата появляется ошибка следующего вида. Исследую полосу удержания. Начальные условия - частоты генераторов равны (ГУН и эталонного т.е. расстройка по частоте 0 ). Меняю расстройку от малых значений до больших , пока система не выйдет из синхронизма. На графике 1 проиллюстрированы мгновенные значения частоты. Видно, что есть ошибка. Система вошла в синхроннизм, но графики частот не совпадают. и отличаются на некий коэффициент (наклон прямой на 2 ). Аналогичная картина, при исследовании полосы захвата. Меняя расстройку от больших к малым значениям , ищу точку входа системы в синхронизм. По графикам (см. прил. 2) частоты опять различны...и снова та же ошибка..если построить кривую с другим наклоном, то все хорошо . Откуда берется эта другая кривая....в идеале , как я думаю, около отсчета 8*10^4 частоты станут равными (синий график и красный) и после переходного процесса система в этой точке должна войти в синхронизм, а она входит в непонятной мне точке и выходит , хотя я моделирую до расстройки 0 , т.е. еще в полосе удержания. Мне не понятно, где я так косячу...может кто-то заметит ошибку? код .....Комменты есть... %> @brief ФАПЧ с передаточной характеристикой фильтра равной 1 %> @param [in] - inputArray, разность частот в герцах, вектор %> @param [in] - pass , полоса удержания системы ФАПЧ в герцах %> @details тестовая программная модель исследования ФАПЧ первого %> порядка. Допущены следующие упрощения. Коэффициент передачи %> фильтра равен 1, ФД реализован без перемножения %> @return frq - частота круговая в радианах %> @return nco - фаза ГУН %> @return control - выход с управляющего элемента %> @return filter - вместо фильтра усилитель компенсирующий 1/2 ФД %> @note Пример вызова %> [frq,nco, control, filter, match] = test_frst (ones( 1 , 80000) * 502, 7); function [frq,control, filter, match] = test_frst_p ( inputArray, pass) Fs = 1E4; % частота дискретизации Ts = 1/Fs; % период дискретизации Fnco= 0; % Частота Генератора % коэффициенты Kf = 2; % Коэффициент передачи ФД Scu = ( pass )*2*pi % Коэфициент передачи управляющего элемента F = Ts/2; % Коэфф.интегратора % Начальные условия phaseDetector(1) = 0; filter(1) = 0; control(1) = 0; match(1) = 0; % for n = 2 : length( inputArray ) phaseDetector(n) = Kf* 1/2 * cos ( 2*pi*inputArray(n)*(n)*Ts - control( n -1 ) ); %фазовый детектор filter(n) = phaseDetector(n); %фильтр control(n) = F*Scu*2*( filter(n) )+control(n-1); % интегратор (управляющий элемент) %------------ для графиков переменные match(n) = 2*pi*inputArray(n)*(n)*Ts - control(n -1); % разность частот %эталонного и частоты генератора + управляющего расстройка frq(n) = Fnco*2*pi + Scu*filter (n); %частота ГУН end вызов функции в командной строке: [frq, control, filter, match] = test_frst_p ( -10:0.0001:0, 2 ); % -10:0.0001:0 - вектор частот в герцах %2 полоса в герцах т.е. ошибка такая. Система входит синхронизм не в тех точках и так же выходит .....