vitus_strom

Свой-

Постов

611 -

Зарегистрирован

-

Посещение

Весь контент vitus_strom

-

ресеты на ресет контроллере и ресет на микроблейзе ну и не забудте обконстрейнить сам микроблейз

-

ну тогда могу порекомендовать повесить ILA на все управляющие сигналы на блейзе чтобы посмотреть кто гадит, имею ввиду внутри

-

ну и качество клока проверьте чтобы длл лок выставил

-

Полярность ресетов проверьте, и aux_reset лучше к основному прикрутить. В остальном вроде все нормально

-

У Вас наверняка блейз в ресете сидит по какой то причине. Было такое тоже... Возможно длл/плл не залочилась которая кормит блейз клоками, ну или вы ее не подключили. Покажите верхний уровень куда блейз включен и блок схему проц системы с блейзом

-

возможно общая скорость как то лимитирована я уже к сожалению деталей не помню было больше 5 лет назад

-

Насколько помню у данного свича не все порты могут быть гигабитовыми и медными, то есть какие то могут быть гигабитными медными какие то оптическими. Это как примечание. Могу так же быть не прав, давно было. Также можете попробовать поставить зеркалирование входного потока на другой порт Сам я не работал с этим чипом, но на плате стоял поэтому кое какая информация до меня доходила...

-

Я работаю с мипи на фпга - кака еще та, с удовольствием бы взялся однако не имею свободных рессурсов.

-

на спартане у меня тоже работает а вот на кинтексе что то сопротивляется на интерфейсе между этернетом и дма чипскопом вижу что с мака пакеты валятся а после буфера уже нет, софт часть видит прерывание но в статусе дма дескриптора нет флага комплит...

-

а точно у Вас корка AXI_Ethernet а не trimode_ethernet?

-

Удалось кому то поднять AXI_Ethernet <-> AXI_DMA (в режиме scatter-gather)?

-

ModelSim вредина!?

vitus_strom ответил RobFPGA тема в Среды разработки - обсуждаем САПРы

ага, понял задумку -

ModelSim вредина!?

vitus_strom ответил RobFPGA тема в Среды разработки - обсуждаем САПРы

я то понял вопрос был в том что Вы действительно хотите присвоить или все же сравнить? :) -

ModelSim вредина!?

vitus_strom ответил RobFPGA тема в Среды разработки - обсуждаем САПРы

rd_hit=rd_en или rd_hit==rd_en? -

10GBase-KR core от Альтера

vitus_strom опубликовал тема в Работаем с ПЛИС, области применения, выбор

Удалось ли кому то поднять, может есть какие то подводные камни? -

вопрос по DSI интерфейсу

vitus_strom опубликовал тема в Работаем с ПЛИС, области применения, выбор

Привет всем! Использую ядро DSI TX от латтиса: не могу объяснить по стандарту следующую ситуацию: на HSYNC (start) ядро посылает следующий поток данных: 21 00 00 09 08 0F 0F 0F FF FF FF FF честно говоря на HSYNC(start) я бы ожидал 21 00 а все остальное это что не смог найти объяснения этому в стандарте, может быть кто то меня просветит? да LP линии в 00 состоянии - High Speed transmission Заранее благодарю за помощь -

Держите кому надо MIPI_DSI_Specification_v1b_8320061508.pdf

-

стандарт DSI

vitus_strom опубликовал тема в Работаем с ПЛИС, области применения, выбор

Привет всем! Не найдется ли у кого страндарта DSI во временное пользование :)? Заранее благодарен нашел, если кому надо пишите, скину -

как описать MAXSKEW в XDC

vitus_strom опубликовал тема в Среды разработки - обсуждаем САПРы

Доброго дня! Никому не приходилось описывать MAXSKEW в Vivado XDC? пробовал через set_max_delay/set_min_delay но ругается критическими варнингами на сегментацию пути - может у кого есть более действенный метод, поделитесь пожалуйстаю Заранее благодарен всем отозвавшимся -

ISO11784/85 135 KHz это не UHF диапазон... и получить на нем дальность в метр вряд ли получится, разве что зажарите на шашлык того кто будет рядом с антеной )))

-

А какая разница кто производитель чипа? Там все по стандарту, вы бы лучше диапазон хотябы указали вашей метки ну или даташит хотябы на нее....

-

Ридеры RFID 915МГц в России

vitus_strom ответил RFTech тема в RF & Microwave Design

Забавно но первый раз вижу 916-921 МГц для европы... -

Ридеры RFID 915МГц в России

vitus_strom ответил RFTech тема в RF & Microwave Design

ну европейский стандарт РФИД Г2 это 868 МГц. Для 100 мВт не надо никаких разрешений а вот выше начнутся проблемы с разрешениямию А что Вас интересует по ридерам? -

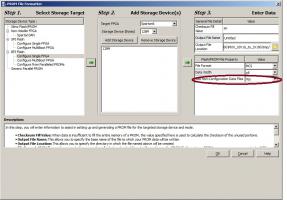

Вот на картинке нарисовал где это поставить потом только файл добавить надо будет - вроде для bpi flash нужно байты свапить и потом читайте их на здоровье микроблейзом (только надо добавить флеш контроллер)

-

Загрузите в область данных флеши и читайте оттуда - кто мешает - если тем более не надо менять их