Pitonbl4

Участник-

Постов

39 -

Зарегистрирован

-

Посещение

Весь контент Pitonbl4

-

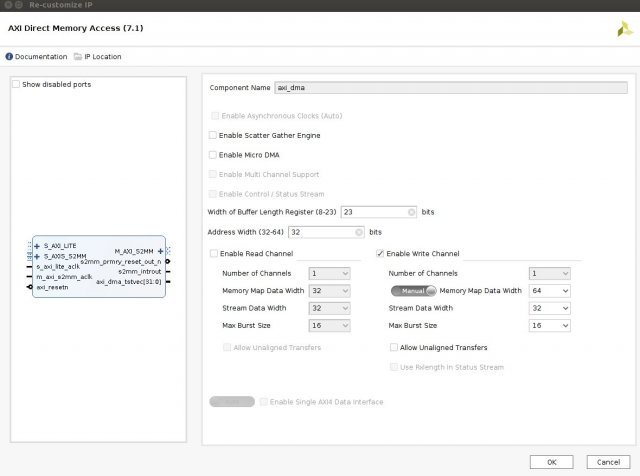

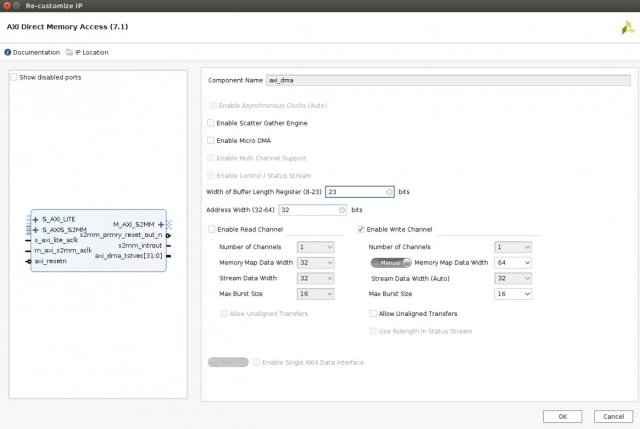

Еще раз попробовал удалить блок дма, перезапустить вивадо, создать блок дма, нажать validate design. Все сработало. Автоматом выставило правильную ширину

-

Перезапустил vivado. В итоге вроде бы могу менять stream data width Если выставляю 64, то в tcl set_property -dict [list CONFIG.c_s_axis_s2mm_tdata_width {64}] [get_bd_cells axi_dma] Нажимаю validate WARNING: [BD 41-702] Propagation TCL tries to overwrite USER strength parameter C_M_AXI_S2MM_DATA_WIDTH(64) on '/axi_dma' with propagated value(32). Command ignored

-

Выдает startgroup set_property -dict [list CONFIG.c_s_axis_s2mm_tdata_width {64}] [get_bd_cells axi_dma] CRITICAL WARNING: [BD 41-737] Cannot set the parameter c_s_axis_s2mm_tdata_width on /axi_dma. It is read-only. endgroup WARNING: [BD 41-702] Propagation TCL tries to overwrite USER strength parameter C_M_AXI_S2MM_DATA_WIDTH(64) on '/axi_dma' with propagated value(32). Command ignored

-

bd dma. Не меняется stream data width

Pitonbl4 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

В block design вставляю блок AXI DMA. Пытаюсь его конфигурировать. s_axis_s2mm_tdata_width должно быть 64. Но оно упорно отображает 32 бита. Как это изменить не могу понять. 1. tcl пробовал startgroup set_property -dict [list CONFIG.c_s_axis_s2mm_tdata_width.VALUE_SRC USER] [get_bd_cells axi_dma] set_property -dict [list CONFIG.c_s_axis_s2mm_tdata_width {64}] [get_bd_cells axi_dma] endgroup Но вылетает CRITICAL WARNING: [BD 41-737] Cannot set the parameter c_s_axis_s2mm_tdata_width on /axi_dma_tus. It is read-only. 2. На форуме xilinx вроде бы говорят, что необходимо все соединить в bd и нажать validate design. Ничего не изменилось. Естественно приходит сообщение: Ничего удивительного, ведь на блок дма приходит 64 бита. 3. Пытался удалить блок дма и заново создать. Не помогло. 32 бита на входе не меняются. Vivado 2017.1 Помогите пожалуйста решить проблему -

Всем спасибо!

-

Можно подробнее или ссылку

-

массивы, потребление ресурсов fpga

Pitonbl4 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Есть два массива, скорее даже вектора размером 1024 * 16 signal arrayData : std_logic_vector((1024 * 16) - 1 downto 0) := (others => '0'); signal arrayC : std_logic_vector((length * 16) - 1 downto 0) := (others => '0'); По сути, происходит заполнение массивов 16-битными числами, а затем происходит свертка. Ничего особенного. В результате "задействованных" ресурсов fpga ~45000 LUT и 9 DSP. Деление делал через обратное умножение. Возведение в квадраты, тоже через умножение. Это столько ресурсов выжирают массивы? Сейчас хочу понять куда копать, чтобы ресурсы раза в 2 уменьшить. Спасибо) -

Меня особо не удивляло, что в PL должен быть статический набор переферии Так и думал. Надеялся что может есть более изящный вариант

-

Добрый день! Есть код вида library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; use IEEE.std_logic_unsigned.all; use IEEE.std_logic_arith.all; library UNISIM; use UNISIM.vcomponents.all; entity top_trigger is generic( NumOfChannel : integer := 6 --! ); port( clk_100MHz : in STD_LOGIC; --! start : in STD_LOGIC; --! data : in STD_LOGIC_VECTOR(255 downto 0); --! sig : out STD_LOGIC --! ); end top_trigger; architecture Behavioral of top_trigger is COMPONENT trigger is generic( n : integer := 64; --! param param : integer := 1; --! param length : integer := 1024 --! param ); port( clk_100MHz : in STD_LOGIC; start : in STD_LOGIC; dataIn : in STD_LOGIC_VECTOR(15 downto 0); sig : out STD_LOGIC ); END COMPONENT; signal dataOut : std_logic_vector(31 downto 0) := (others => '0'); signal start_d1 : std_logic := '0'; signal start_d2 : std_logic := '0'; begin inst_fd0: fd port map(start_d1, clk_100MHz, start); inst_fd1: fd port map(start_d2, clk_100MHz, start_d1); inst_channels_gen : for i in NumOfChannel to NumOfChannel generate inst_trigger : trigger generic map( n => 64, param => 1, length => 1024 ) port map( clk_100MHz => clk_100MHz, start => start_d2, dataIn => data(((i + 1) * 16) - 1 downto i * 16), sig => sig ); end generate; end Behavioral; Это PL часть. Сейчас хочу это все прокинуть в PS часть. В будущем, хотелось бы менять NumOfChannel из PS части. Для этого необходимо NumOfChannel убрать из generic и сделать портом. Пытаюсь так сделать, но появляются ошибки вида: actual for formal port is neither a static name nor a globally static expression; range for generate must be a static vhdl. Подскажите как это можно сделать?

-

Да, действительно. Благодарю!

-

Чтение из файла в vhdl

Pitonbl4 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Не нашел решение такой проблемы. При чтении из файла in.txt вылетает ошибка: Error: STD_LOGIC_1164.READ(STD_ULOGIC_VECTOR) Error: Character '1' read, expected STD_ULOGIC literal. Error: STD_LOGIC_1164.READ(STD_ULOGIC_VECTOR) Error: Character '2' read, expected STD_ULOGIC literal. и т.д. Файл in.txt: 1 2 3 read.vhd use IEEE.std_logic_textio.all; use STD.textio.all; ... file in_file : text; ... read_file : process variable v_ILINE : line; variable v_data : std_logic_vector(15 downto 0); --variable v_data : integer; variable v_SPACE : character; begin file_open(in_file, "in.txt", read_mode); while(not endfile(in_file)) loop readline(in_file, v_ILINE); read(v_ILINE, v_data); --dataIn <= CONV_STD_LOGIC_VECTOR(v_data, 16); dataIn <= v_data; wait for 1 us; end loop; file_close(in_file); wait; end process; ... Если вместо variable v_data : std_logic_vector(15 downto 0); использовать variable v_data : integer; , то все работает. Хотя даже на этом форуме упоминали, что при включении use IEEE.std_logic_textio.all; все должно нормально работать. Пример брал здесь: https://www.nandland.com/vhdl/examples/example-file-io.html -

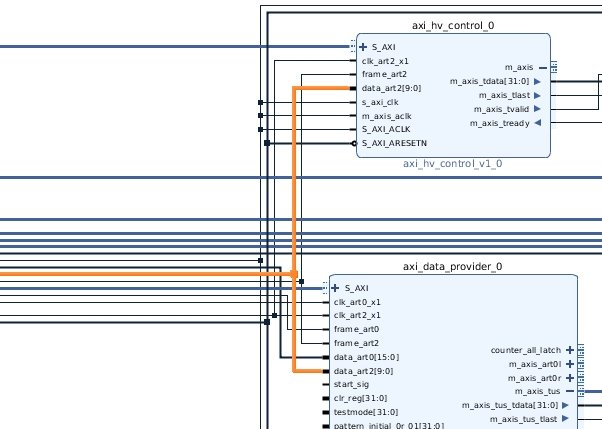

Оранжевым выделена линия, по которой приходят данные с pad. В самих модулях есть IDDR вида: IDDR_inst_data_hv_control : IDDR generic map ( DDR_CLK_EDGE => "OPPOSITE_EDGE", --! "OPPOSITE_EDGE", "SAME_EDGE" or "SAME_EDGE_PIPELINED" INIT_Q1 => '0', --! Initial value of Q1: '0' or '1' INIT_Q2 => '0', --! Initial value of Q2: '0' or '1' SRTYPE => "SYNC") --! Set/Reset type: "SYNC" or "ASYNC" port map ( Q1 => data_art2_odd(i), --! 1-bit output for positive edge of clock Q2 => data_art2_even(i), --! 1-bit output for negative edge of clock C => clk_art2_x1, --! 1-bit clock input CE => '1', --! 1-bit clock enable input D => data_art2(i), --! 1-bit DDR data input R => '0', --! 1-bit reset S => '0' --! 1-bit set ); Если все использовать в таком виде, то вылетит ошибка вида: [Place 30-457] The instance 'data_art2[5]_IBUF_inst' part of an IOB is driving multiple IDDR instances. One IOB can drive only one IDDR which can be packed into ILOGIC. The IDDR instances involved are: design_1_i/axi_data_provider_0/U0/Inst_data_provider/IDDR_inst_data_gen[5].IDDR_inst_data_art2 design_1_i/axi_hv_control_0/U0/Inst_form_hv/IDDR_inst_data_gen_hv_control[5].IDDR_inst_data_hv_control Думал поставить перед IDDR буфер IBUF, но это тоже не помогает. Понял, спасибо

-

Столкнулся с такой штукой. Есть два модуля, которые на вход получают одни и те же данные и дальше их пакуют соответствующим образом. Вся система работает на 100 МГц, а данные надо принимать на 200 МГц => необходимо ставить IDDR. Т.к. один IOB может управлять одним IDDR, то решил для этого внутри каждого модуля поставить IBUF. Но проблема не решается. Все это реализовано в ZYNQ. Подскажите как можно избавиться от этой проблемы. Свести все в один модуль не вариант.

-

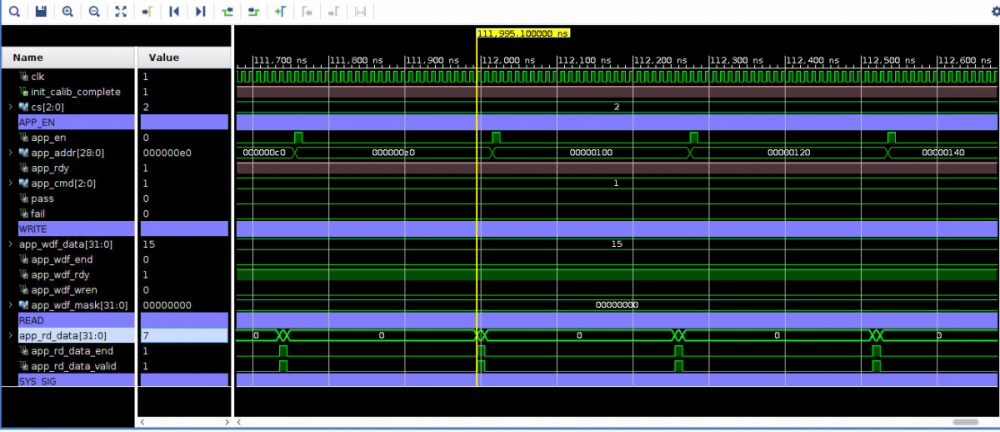

Тестирование MIG_7 и DDR3(SDRAM)

Pitonbl4 опубликовал тема в Работаем с ПЛИС, области применения, выбор

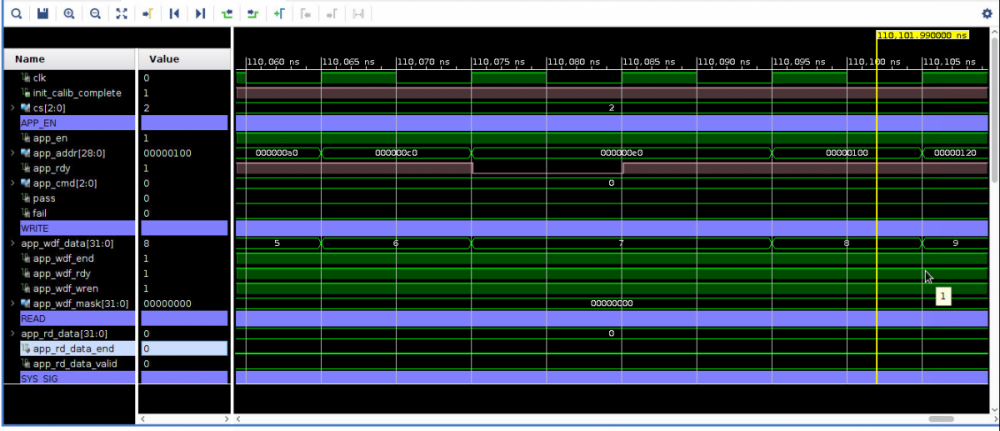

Добрый день! Начал тестить mig7 c ddr3 (sdram) и получаю бред. ddr3 контроллер написан xilinx. Запись и чтение в burst режиме. Софт Vivado 2017.2 Параметры mig: PHY to Controller clock ratio: 4:1 Number of Bank machines: 4 Memory Type: components memory part: MT41j256m16xx - 107 Ordering: normal Memory address maping selection: bak-row-column ------------------------------------------------------------ Собственно по картинкам. Запись Видно, что по адресу 0x000..c0 пишется 6, по адресу 0x000..e0 - 7, по адресу 0x000..100 - 8 Чтение 0x000..c0 - 6, 0x000..e0 - 7, 0x000..100 - 7, 0x000..120 - 8 ------------------------------------------------------------- Кто сталкивался и как без костылей обходится такая проблема? -

Если я нигде не ошибся, то iowrite32(data, base_addr + 1) сдвигает на 32 бита!!! P.S. Завтра точно скажу.

-

Добрый день! Как можно писать со сдвигом. Есть dts: myled: myled@43c00000 { compatible = "xlnx,myled-1.0"; reg = <0x43c00000 0x10000>; }; По сути на ZedBоard это 8 лампочек Написал драйвер и могу включать лампочки таким образом: echo 0x1 > /proc/myled Теперь хочу записывать со сдвигом, т.е. например единицу в 3 лампочку. Т.е. в моем случае я отремапил лампочки в base_addr. Если делать типа iowrite32(data, base_addr + addr_offset), то не помогает. Вот попробовал: [ 25.093368] myled probed at VA 0xe0970000 zynq> echo 0x1 > /proc/myled [ 31.906246] res->start 0x43c00000 [ 31.909543] remap_size 0x00010000 [ 31.912899] base_addr 0xe0970000 [ 31.916054] base_addr + ADDR_OFFSET 0xe0970400 В итоге загорается 0 лампочка. Как например зажечь 3 лампочку именно с помощью сдвига? Как рассчитать addr_offset? Ответы типа записать 0x8 в base_addr не принимаются. Спасибо!

-

Вопросы по написанию драйвера под Linux

Pitonbl4 ответил Pitonbl4 тема в Программирование

1. Почитал методу на ibm. Давайте напишем модуль под /dev; /sys; /proc. Этот модуль вы можете допилить до драйвера. В таком духе. Поэтому то, что вы написали далее я и не знал. 2. Да, сейчас сам описыал в device tree устройство и поэтому не доходило про platform device. Зачем описывать структуру устройства в platform device, если еcть device tree. 3. Platform devices сами по себе не поддаются обнаружению. Т.е. устройство не может сказать "Эй! Я присутствую!" программному обеспечению. Что делать? Для это была введена виртуальная шина (platform bus). С одной стороны устройства подключаются к такой шине, а с другой - к шине присоединяются драйвера, которые запрашивают устройства с необходимым именем. Т.е. за это как раз и отвечают эти строки: // Из device tree static const struct of_device_id myled_of_match[] = { {.compatible = "xlnx,myled-1.0"}, {}, }; static struct platform_driver myled_driver = { .driver = { .name = DRIVER_NAME, .owner = THIS_MODULE, .of_match_table = myled_of_match}, .probe = myled_probe, // Обязательно .remove = myled_remove, .shutdown = myled_shutdown }; Но для PCI и USB там другая картина. Как вы и написали. 4. Т.е. /proc это не профессионально, но советуете книгу чтобы подробней изучить этот метод. А как тогда делают проффесионалы? Изучать примеры реальных драйверов? На данный момент успел поковыряться с /proc. Действительно, довольно просто. Книгу пока быстро полистал, там есть и про /dev и /proc, а дальше пока не смотрел. Из-за тогоч то нет переносимости? Ведь драйвер это прослойка между железом и, в конечном счете, пользователем. Т.е. что надо пользователю? Знать какие есть методы, структуры и т.д. в драйвере, чтобы можно легко было взаимодействовать с железом через свою прогу. P.S Про размещение топика учту. Толком не мог определить, куда можно задать свой вопрос. -

Вопросы по написанию драйвера под Linux

Pitonbl4 ответил Pitonbl4 тема в Программирование

Спасибо! От себя только добавлю, что тема про Platform device и Platform driver хорошо раскрыта здесь. -

Вопросы по написанию драйвера под Linux

Pitonbl4 опубликовал тема в Программирование

Добрый день. Начал переходить с Bare metal на Linux. Пытаюсь разобраться как написать простенький драйвер для моей ip core. Пока это просто 8 лампочек. Борда: zedboard. Сейчас читаю литературу, т.к. до этого не было опыта написания драйверов. 1) Не рекомендуется писать драйвер под файловую систему /dev. Раньше конечно так делали. Сейчас, якобы актуально писать под файловую систему /proc или /sys. Верно ли это? Хочется сразу научиться праивльным вещам. :maniac: Т.е. может при написании драйвера под какую-нибудь фс скрываются ккаие-то подводные камни. И есть резон писать под другую фс. 2) Почитал https://linuxseekernel.blogspot.com/2014/05...-practical.html и, честно говоря, так и не понял какое различие между: Platform Driver Platform Device Т.е. это два независимых варианта? Или есть определенные случаи когда стоит что-то конкретное из этого использовать? 3) Как я понял. Написание дравера состоит из двух больших шагов. а) Создать виртуальный файл в файловой системе. Чтобы в него можно было писать/читать и т.д. б) Связать этот виртуальный файл с физическим устройством. Верно? 4) Пока нашел такой код. Все нормально работает. myled.txt Как можно реализовать чтение и запись в регистры с определенным сдвигом? Действовать через base_addr (он определен в коде)? -

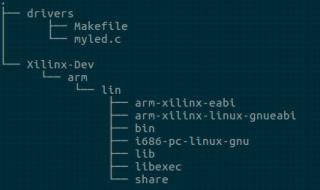

Makefile для компиляции модуля ядра

Pitonbl4 опубликовал тема в Операционные системы

Добрый день! Пытаюсь скомпилировать модуль ядра *.ko. Делаю это впервые. Прошу сильно не ругать. Сейчас проект выглядит как на картинке в прикрепленном файле. Make файл выглядит так obj-m := myled.o all: make -C ../Xilinx-Dev/ M=$(PWD) modules clean: make -c ../Xilinx-Dev/ M=$(PWD) clean В терминале прописываю следующее: drivers$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- make -C ../Xilinx-Dev/ M=/home/yan/git/zedboard/boot_files/drivers modules make[1]: вход в каталог «<path to Xilinx-Dev>/Xilinx-Dev» make[1]: *** Нет правила для сборки цели «modules». Останов. make[1]: выход из каталога «<path to Xilinx-Dev>/Xilinx-Dev» Makefile:4: ошибка выполнения рецепта для цели «all» make: *** [all] Ошибка 2 Подскажите пожалуйста как правильно необходимо делать! Все, кажется осознал. В Makefile ищутся modules. Т.е. мне надо к ним указывать путь. -

Извиняюсь. Банальная ошибка. Не тот адрес юзал.

-

Настройка ethernet

Pitonbl4 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Пытаюсь настроить u-boot для своей платы (Zynq). На плате несколько ethernet. Проблема в том, что, как я понял, u-boot доходит до первого (первого по адресу) ethernet. Т.к. я его пока не использую, то мне в терминал приходит сообщение: ethernet@e000b000 Waiting for PHY auto negotiation to complete......... TIMEOUT ! И все, до следующего ethernet уже не идет. А я его как раз использую. Собственно вопрос, как заставить u-boot использовать нужный мне ethernet? Инфа с терминала по u-boot U-Boot 2018.01-06474-g1c81b42-dirty (Jun 29 2018 - 16:41:07 +0300) Board: Xilinx Zynq Silicon: v3.1 DRAM: ECC disabled 1 GiB MMC: sdhci@e0100000: 0 (SD) Invalid bus 0 (err=-19) *** Warning - spi_flash_probe_bus_cs() failed, using default environment In: serial@e0000000 Out: serial@e0000000 Err: serial@e0000000 Net: ZYNQ GEM: e000b000, phyaddr 0, interface rgmii-id eth0: ethernet@e000b000 reading uEnv.txt 166 bytes read in 11 ms (14.6 KiB/s) Importing environment from SD ... Hit any key to stop autoboot: 0 настройка dts (все что касается ethernet) aliases { ethernet0 = &gem0; ... ... }; &gem0 { phy-mode = "rgmii-id"; status = "okay"; xlnx,ptp-enet-clock = <0x7f28150>; phy-handle = <ðernet_phy>; ethernet_phy: ethernet-phy@0 { reg = <0>; device_type = "ethernet-phy"; }; }; В ReadMe по U-boot нашел такую вещь как: ethrotate - When set to "no" U-Boot does not go through all available network interfaces. It just stays at the currently selected interface. Попробовал выставить его в "yes", что бы пробежаться по всем ethernet, но это ни к чему не привело. mii info PHY 0x05: OUI = 0x0885, Model = 0x22, Rev = 0x02, 100baseT, FDX PHY 0x07: OUI = 0x0885, Model = 0x22, Rev = 0x02, 10baseT, HDX Тоже интересный момент. Ethernet должен быть 1000baseX. Если есть какие-то идеи подкиньте плиз. -

Вы переведите ошибку. У вас на вход будут приходить данные откуда-то там. А вы ему такую конструкцию dwt_b <= dwt_v;

-

Делал. Я писал (значение state проверил, когда назначил его signal) Это не так важно. Т.к. когда state сигнал, то его просто можно отследить при симуляции data_tmp - массив векторов по 16 бит. Загоняю в for, т.к. заводить 64 переменных или вектор(64х16 downto 0) не очень. read просто читает значение из строки. 10 read - 10 значений из строки, если столько там имеется. break нет в vhdl. Есть exit; что-то там еще. Но что это даст?