lkg47

Участник-

Постов

41 -

Зарегистрирован

-

Посещение

Весь контент lkg47

-

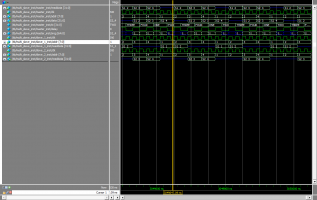

не соглашусь с утверждением относительно quartus 15, проверил результаты компиляции для разных значений set_net_delay - видно , что подстраивается под заданные значения

-

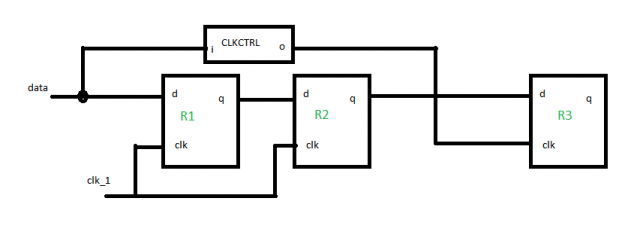

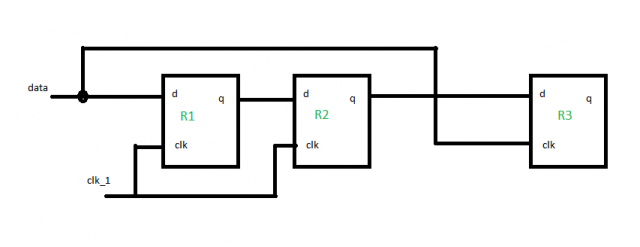

всем спасибо за комментарии, решил проблему с помощью set_net_delay, добавил CLKCTRL блок и прописал минимальные и максимальные задержки для 1. data --> R1|d 2.1 data --> CLKCTRL|o 2.2 CLKCTRL|o -->reg R3 проверка на исполнение через TQ report_net_delay и все-таки, существует ли вообще возможность задать разницу во времени между R1|d и R3|clk?

-

data - асинхронный сигнал clk_1 - выход ФАПЧ буфер перед R3 ставить нельзя

-

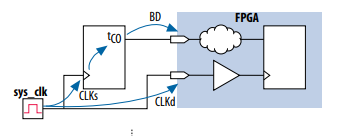

т.е. вы предлагаете сделать на подобие этого: ? вот только внешний регистр этого примера у меня внутри ПЛИС, а set_input_delay назначается только на порты, как быть?

-

констрейн на относительные задержки

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, подскажите пожалуйста, проблема: есть асинхронный вход - data, тактовая - clk_1 как задать ограничение для Quartus такое, чтобы максимальная и минимальная разница в задержках между data --> R1|d и data --> R3|clk задавалась и фиттер мог под нее подстраивать пути? -

SV modport иерархия

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, прошу помощи: Возможно ли протаскивать сигналы через интерфейс с modport output в подмодуль, а после с modport input в подподмодуль? или другими словами - нужно чтоб в подмодуле возможно было изменять сигналы шины, при этом доходили до ПодПодмодуля. Причина использования modport - когда перешли на design partition quartus начал ругаться на неоднозначность направления портов Квартус дает ошибку: Error (10978): SystemVerilog error at test.sv(32): unknown type and interface type are not equivalent - equivalent types must have same number of bits пример: `timescale 1ns / 1ps interface bus( input logic clk, input int x ); int y; modport io( input clk, input x, output y ); modport ii( input clk, input y, input x ); endinterface /////////////////////SECOND_SUB module second_sub( bus.ii bus_second, output int z ); always_ff@(posedge bus.clk) z <= z + bus_second.x + bus_second.y; endmodule /////////////////////FIRST_SUB module first_sub( bus.io bus_first ); second_sub second_sub_inst( .bus_second(bus_first.ii), .z(z) ); always_ff@(posedge bus_first.clk) bus_first.y <= z + bus_first.y; endmodule /////////////////////TOP module top ( input logic clk, output logic out, input int x ); bus bus_top( .clk(clk), .x(x) ); first_sub( .bus_first(bus_top.io) ); always_ff@(posedge clk) begin out <= bus_top.y[0]; end endmodule -

LVDS Смещение на источнике

lkg47 опубликовал тема в от ТТЛ до LVDS здесь

Здравствуйте, Источник сигнала с логикой CML, имеющий емкостную развязку (SFP модуль), подключен к плате, от которой проложена линия ~ 40см экранированной витой пары до приемника - LVDS CycloneV с включенным терминатором (не XCVR вход). Частоты ~ 400МГц На стороне приемника нет возможности установить смещение резисторами. Планирую выполнить подтягивание линии P через 16,9k к 3.3V и 10к к GND на стороне источника (рядом с разъемом SFP модуля). Имеет ли данный подход какие-либо недостатки? -

Нет, не работает: `timescale 1ns / 1ps module top ( ); //===========================================/ //GEN //===========================================/ logic clk = 'b0; always #10 clk = ~clk; //===========================================/ //TEST UNIT //===========================================/ logic [7:0] out; m1 m1_inst( .clk(clk), .out(out) ); endmodule //===========================================/ //PACKAGE //===========================================/ package pck; typedef enum int unsigned { a, b, c } state_t; endpackage //===========================================/ //TEST_MODULE //===========================================/ module m1 import // pck:: state_t, pck:: state_t::*; /* pck:: a, //как исключить эту запись? pck:: b, //как исключить эту запись? pck:: c; //как исключить эту запись? */ ( input logic clk, output logic [7:0] out = 'b0 ); state_t state; always_ff@(posedge clk) begin case (state) a: begin state <= b; out <= "A"; end b: begin state <= c; out <= "B"; end c: begin state <= a; out <= "C"; end default: begin state <= a; out <= "D"; end endcase end endmodule

-

видимо это сделать не возможно, решил пойти путем создания нескольких независимых package с полным импортом через "import package_name::*;"

-

импорт списка состояний из package

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, подскажите пожалуйста: Возможно ли импортировать из package(Systemverilog) список состояний enum одним разом? package pck; enum int unsigned { a, b, c } state_t; endpackage module m1 import pck:: state_t, pck:: a, //как исключить эту запись? pck:: b, //как исключить эту запись? pck:: c; //как исключить эту запись? ( input logic clk ); state_t state; always_ff@(posedge clk) begin case (state) a:out <= "A"; b:out <= "B"; c:out <= "C"; default: out <= "D"; endcase end endmodule Причина: можно использовать запись в виде "import:*;" но в этом случае если модуль большой то не сразу понятно какие параметры задействованы, поэтому хотелось бы импортировать поименно, но с enum выходит вышеуказанная проблема. -

мультиплексор шины в SV

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, Прошу помочь: Правильно ли утверждение: если создать одну шину данных,направленную в сторону мастера, и адресную шину, далее соединить шину данных слейвов с мастером напрямую (без применения явного описания мультиплексора по адресам), то компилятор сам формирует мультиплексор? допустим: создаем модуль мастера, перебирающий адреса,создаем слейв, комбинационной логикой мультиплексируем по адресу выходную шину, но если реализовывать слейв следующими способами результаты получаются разными: реализация слейва через интерфейс: 1.мультиплексирование данных по адресу: modelsim - ошибка quartus - полная компиляция выполненяется 2.с отдельным процессом мультиплексирования шины по адресу внутри слейва: modelsim - ошибка quartus - полная компиляция выполненяется реализация слева без интерфейса - портами: 1.мультиплексирование данных по адресу: modelsim - моделирование выполняется с ошибкой передачи шины по одному адресу из четырех quartus - полная компиляция выполненяется 2.с отдельным процессом мультиплексирования шины по адресу внутри слейва: modelsim - моделирование выполняется без ошибок quartus - полная компиляция выполненяется С чем связаны различные варианты результатов? Как правильно реализовать чтение из множества ведомых модулей по адресу? `timescale 1ns / 1ps `define COMB;//COMB or REG module tb(); //===========================================/ //GEN //===========================================/ logic clk = 'b0; logic [31:0] data; always #10 clk <= ~clk; multi_slave multi_slave_inst( .* ); endmodule module multi_slave ( input logic clk, output logic [31:0] data ); logic [31:0] readdata; logic [7:0] addr; master master_inst( .* ); slave_1 slave_1_inst( .* ); slave_2 slave_2_inst( .* ); endmodule module master ( input logic [31:0] readdata, input logic clk, output logic [7:0] addr, output logic [31:0] data ); enum int unsigned { ONE, TWO, THREE, FOUR } st; logic delay = 'b0; always_ff@(posedge clk) begin case (st) ONE: begin addr <= 1; st <= TWO; end TWO: begin addr <= 2; st <= THREE; end THREE: begin addr <= 3; st <= FOUR; end FOUR: begin addr <= 4; st <= ONE; end default: begin st <= ONE; delay <= 1'b0; addr <= 1; end endcase end logic [64:0] sreg = 'b0; always_ff@(posedge clk) sreg <= {sreg[31:0],readdata}; assign data[31:0] = sreg[63:32]; endmodule /*****************COMB*******************/ `ifdef COMB module slave_1 ( input logic clk, input logic [7:0] addr, output logic [31:0] readdata ); logic [31:0] readdata_s1; always_comb begin case(addr) 8'd1: readdata = readdata_s1; 8'd2: readdata = readdata_s1; default: readdata = 'bZ; endcase end always_comb begin case(addr) 8'd1: readdata_s1 = "S1_1"; 8'd2: readdata_s1 = "S1_2"; default: readdata_s1 = 'bZ; endcase end endmodule module slave_2 ( input logic clk, input logic [7:0] addr, output logic [31:0] readdata ); logic [31:0] readdata_s2; always_comb begin case(addr) 8'd3: readdata = readdata_s2; 8'd4: readdata = readdata_s2; default: readdata = 'bZ; endcase end always_comb begin case(addr) 8'd3: readdata_s2 = "S2_3"; 8'd4: readdata_s2 = "S2_4"; default: readdata_s2 = 'bZ; endcase end endmodule -

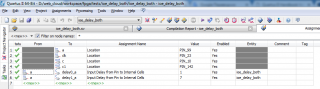

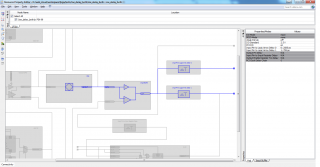

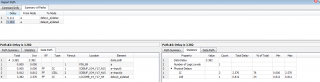

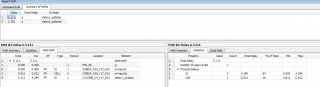

получилось использовать две задержки с одного IOE(на железе не проверял, но полагаю должно работать): 1. задаю в assigment editor разные задержки для входного пина: 2. получаю в chip planner задействованных два блока задержки: 3. в TimeQuest проверяю пути: при изменении параметра задержки в assigment editor -е задержки пути соответственно изменяются `timescale 1ns / 1ps module ioe_delay_both ( input logic a, input logic clk, output logic c, output logic c1 ); //===========================================/ // //===========================================/ logic a0; lcell delay0_a( .in(a), .out(a0) ); logic a1; lcell delay1_a( .in(a), .out(a1) ); logic [3:0] cnt = 'b0; always_ff@(posedge clk) begin if(a0) cnt <= cnt + 1'b1; c <= cnt[3]; end logic [3:0] cnt1 = 'b0; always_ff@(posedge clk) begin if(a1) cnt1 <= cnt1 + 1'b1; c1 <= cnt1[3]; end endmodule

-

более одного выхода IOE в ПЛИС

lkg47 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Возможно ли на Cyclone IV E реализовать входной элемент IOE так, чтобы забирать с него например и задержанный и прямой и с регистра сигналы? -

overflow параметра

lkg47 ответил lkg47 тема в Языки проектирования на ПЛИС (FPGA)

получается вот так, но слишком громоздко: parameter m = 640; parameter WIDTH = $clog2(m); parameter a = WIDTH'(192); parameter b = WIDTH'(320); parameter c_sub = (WIDTH + 1)'(a + b); parameter c = c_sub[WIDTH - 1:0]; -

overflow параметра

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте! подскажите пожалуйста: каким образом правильно сказать квартусу о том, что у меня не будет превышения значения параметра после суммирования? systemverilog -

при попытке синтезировать код описанный выше Quartus выдает следующее сообщение: в литературе по SV не нашел примеров с объявлением интерфейса внутри модуля. пока вижу только один выход: -описывать интерфейсы в каждом из топ модулей, при этом выполнять проверку директивы для исключения повторного чтения `ifndef def_interface_bus_a `define def_interface_bus_a interface bus_a (input logic reset); logic clk; endinterface `endif -отличающиеся порты подключать отдельно наткнулся здесь на форуме на перевод стандарта по интерфейсам, может кому-нибудь пригодится : IEEE Standard for SystemVerilog—Unified Hardware Design,Specification, and Verification Language(Неофициальный перевод)IEEE SV Interface (неофициальный перевод)

-

Такая же проблема, может нынче кто-нибудь решил этот вопрос? у меня, при тех же настройках что у ТС, byte-ordering работает только с обычными данными (без "comma symbols"), возможно так и должно быть судя по тому где расположен блок byte-ordering, однако это неудобно, т.к. приходится посылать перед byte-ordering символом comma symbol для его предварительного запуска. настройки native Cyclone V PHY: manual byte ordering, управление по линии rx_std_byteorder_ena_port

-

я ошибочно полагал, что интерфейс может быть только за модулями, видимо по причине привычки называть инстанс одноименно модулю(в этом случае компилятор ругается созданный экземпляр) в пример добавил общий для всех модуль в итоге: ////////////TB////////////// module tb(); logic reset = 'b0; top1 m1( .reset(reset) ); top2 m2( .reset(reset) ); endmodule ////////////TOP1//////////////////// module top1(input logic reset); interface bus_a(input logic reset); logic clk; logic clk_b; endinterface bus_a bus_a_instance(.reset(reset)); m1_1 m1_1(.bus_a(bus_a_instance)); gen gen_instance(.bus_a(bus_a_instance)); endmodule /////////////TOP2///////////////// module top2(input logic reset); interface bus_a(input logic reset); logic clk; logic clk_a; endinterface bus_a bus_a_instance(.reset(reset)); m2_1 m2_1(.bus_a(bus_a_instance)); gen gen_instance(.bus_a(bus_a_instance)); endmodule ////////////подмодуль TOP1//////////// module m1_1(bus_a bus_a); logic m1_1_clk = 'b0; assign bus_a.clk = m1_1_clk; assign bus_a.clk_b = ~ m1_1_clk; always #10 m1_1_clk <= ~m1_1_clk; endmodule ////////////подмодуль TOP2//////////// module m2_1 (bus_a bus_a); logic m2_1_clk = 'b0; assign bus_a.clk = m2_1_clk; assign bus_a.clk_a = ~ m2_1_clk; always #20 m2_1_clk <= ~m2_1_clk; endmodule //////////общий модуль///////////// module gen(bus_a bus_a); endmodule Спасибо за помощь!

-

экземпляр: bus_a bus_a(.reset(reset)); есть два проекта которых необходимо объединить в тестбенче. В Топ модулях проектов используются одинаковые подмодули, в которых используются одинаковые интерфейсы, если я задам в одном из Топ модулей имя интерфейса другим то он не будет стыковаться с его внутренним подмодулем использующим стандартный интерфейс. например так: создаю экземпляр: bus_a bus_X(.reset(reset)); подключаю подмодуль: m2_1 m2_1(.bus_a(bus_X)); в подмодуле имею объявление порта: module m2_1(bus_a bus_a) получаю ошибку о не соответствии интерфейсов: Сейчас попробовал использовать объявление интерфейса в подмодуле таким путем: module m2_1(interface bus_a) ошибок нет, все работает; Но теперь, судя по Вашей реакции создается впечатление, что я как то неверно использую интерфейсы. Подскажите, как Вы используете интерфейсы в этих случаях, т.е. когда надо объединять несколько топ модулей в тестбенче? или одинаковые интерфейсы Вы не применяете? Подскажите пожалуйста, как определять в интерфейсы в разных областях видимости?

-

одинаковые interface в модулях тестбенча

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, Прошу помочь с такой проблемой: Имеется два toplvl модуля, с некоторыми одинаковыми подмодулями связываемыми интерфейсами. Интерфейсы в основном имеют одинаковые порты, но есть и отличающиеся. ////////////TB////////////// module tb(); logic reset = 'b0; m1 m1( .reset(reset) ); m2 m2( .reset(reset) ); endmodule ////////////TOP1//////////////////// interface bus_a(input logic reset); logic clk; logic clk_b; endinterface module m1(input logic reset); bus_a bus_a(.reset(reset)); m1_1 m1_1(.bus_a(bus_a)); endmodule module m1_1(bus_a bus_a); logic m1_1_clk = 'b0; assign bus_a.clk = m1_1_clk; assign bus_a.clk_b = ~ m1_1_clk; always #10 m1_1_clk <= ~m1_1_clk; endmodule /////////////TOP2///////////////// interface bus_a(input logic reset); logic clk; logic clk_a; endinterface module m2(input logic reset); bus_a bus_a(.reset(reset)); m2_1 m2_1(.bus_a(bus_a)); endmodule module m2_1(bus_a bus_a); logic m2_1_clk = 'b0; assign bus_a.clk = m2_1_clk; assign bus_a.clk_a = ~ m2_1_clk; always #20 m2_1_clk <= ~m2_1_clk; endmodule //////////////////////////////// ошибка в modelsim: Можно создать одинаковые интерфейсы, где порты будут одинаковыми для TOP1 и для TOP2, но разве это правильное решение? -

Добрый день! Использую плату Terasic C5G с ПЛИС 5GXFC5C6F27C7, QuartusII_15.0, В ходе проверки работы встроенных трансиверов столкнулся с следующей проблемой: Triple-speed ethernet Altera не проходит проверку тестовой записи в MAC контроллер(в Modelsim все работает), решил проверить тактовый вход: Имеются счетчики для мигания светодиодом, которые тактируются подключенными к тактовому входу трансивера частотами 125МГц(LVDS) и 156.25МГц(LVDS), результат: не мигает. Вставляю в проект модуль PLL, подключаю refclk к другому источнику (50МГц) не связанному с трансиверами, выход (333МГц) не подключаю результат: мигает. В чем может быть причина?

-

Спасибо!, помогло

-

как исключить несколько выводов из шины?

lkg47 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

всем привет! есть шина типа x[a], но используется не полный массив, т.е. от x[0][0] до x[a][b-n], как отключить автоматическое назначение оставшимся "n" выводам? (Quartus 15.0, SV) -

да - `timescale 1ns / 1ps

-

Здравствуйте! столкнулся с следующей проблемой: PLL (Cyclone V) Fin = 50МГц M-Counter = 8 Multiply Factor(K) = 2748778984 N-Counter = 1 C-Counter = 6 Fractional carry out = 32 Fout = 72 МГц при моделировании в Modelsim 10.3d каскадного PLL (Upstream) значение выходной частоты не соответствует выставленной частоте в мегафункции PLL и равна 68.53МГц (время моделирования 1мс) 72МГц на выходе получаю в следующих случаях: -При моделировании Fractional-N PLL с каскадированием в режиме gate-level -При моделировании Fractional-N PLL без каскадирования -При моделировании Integer-N PLL c каскадированием -При моделировании Fractional-N PLL с каскадированием и изменении разрядности дельта-сигма модулятора "fractional carry out" = 8 В чем может быть проблема?