RamZoom

Участник-

Постов

67 -

Зарегистрирован

-

Посещение

Весь контент RamZoom

-

Наткнулся на GitHub на майнера криптовалют. Заинтересовал вопрос что там вообще за алгоритм вычислений. В архивах лежат исходники под DE2-115 и как часто это бывает не получилось собрать проект и отсимить. Если кто в курсе что там делается подскажите. Может кто знает где готовые исходники посмотреть можно

-

Nios II IDE + Qt

RamZoom опубликовал тема в Среды разработки - обсуждаем САПРы

Может кто занимался сборкой из eclipce Nios II IDE? Какие используются компилятор, отладчик и может что-то еще альтеровское, а главное как все это дело собрать. Все чаще на форумах встечается описание переход разработчиков ARM на фреймворк Qt. Есть-ли возможность у любителей NIOSII писать и отлаживать проекты не в eclipce, а в Qt? Если кто в курсе подскажите -

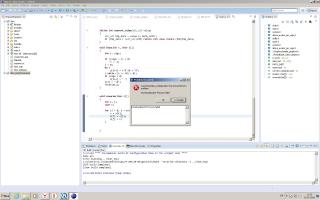

Подскажите как лечить проблемку. Собираю проект, заливаю нормально работает. Вношу изменения и перезаливаю все в норме. Непонятно по какой причине при очередной заливке в Eclipce вылетает ошибка Problem Occurred 'Launching name_configuration' has encontered a problem. Download ELF Process failed. и больше проект не отрабатывает. Перезаливка *.sof, Generate BSP, создание новой RUN Configurations... не помогают. Что делать?

-

Друзья подскажите как Как залить Nios через AS? Суть вопроса до этого на платах был JTAG, но так вышло, что на одной оказался только прямой доступ к EPCS. Если я правильно понял один из способов конвертировать из sof в pof с добавлением файла с расширением *.hex. Память для ядра располагается в on-chip. Также в проект был добавлен EPCS_FLESH контроллер. После компиляции в папке с проектом оказалось несколько файлов с расширением *.hex. Среди них был один для памяти и один для EPCS. При попытке добавить каждого из них при конвертировании были ошибки о том, что адрес должен содержать 0 и 1 для одного и 0 и 8 для другого. Что делать?

-

Проблемы с SOPC Builder

RamZoom опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Привет всем! Подскажите как корректно перенести проект Quartus с NiosII на другой компьютер. Столкнулся с такой бедой при переносе Eclipce указал туже рабочую папку, что и на своем компе при создании проекта. Eclipce файлы увидел, но компилить отказался. Но это не самое страшное. Проект был написан в 11.0 а на другом компе был только 10.1. И вроде-бы ничего страшного. Sopc Builder нормально увидел свой файл, позволял вностить изменения, собирал ядро, работал, но переферия не корректно работала. Оказалось что он хоть и показывал что внесенные в PLL изменения применены, но на выходе частота не изменялась. Проекты переносил в двух вариантах : создавал архив и отдельно папку целиком архивировал. Результат одинаков. Так собственно вопросы: - как корректно переносить проекты (в т.ч файлы Eclipce), с чем еще возникают проблемы кроме PLL и может еще какие проблемы из-за разных версий Quartus? -

Linux на CycloneV

RamZoom опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Уважаемые форумчане подскажите возможно-ли собрать на базе платы DE1 SoC c 5CSEMA5F31C6 Linux (или какую-то другую операционку) с графическим интерфейсом??? Консоль конечно хорошо, но хочется графики. Может кто сам делал (если это возможно) или знает где посмотреть можно киньте ссылку. -

hex редактор sys_cpt.dll

RamZoom ответил RamZoom тема в Среды разработки - обсуждаем САПРы

Всем большое спасибо -

hex редактор sys_cpt.dll

RamZoom опубликовал тема в Среды разработки - обсуждаем САПРы

Подскажите каким именно редактором можно отредактировать sys_cpt.dll. Все пишут любым. Скачал pe-explorer чет ничего не понял как там и что. Если кому не трудно скиньте скриншоты как редактировали данный файл и какие значения меняли. Заранее спасибо. -

К сожалению у меня нет нескольких тысяч $, чтобы купить стратикс или арию с армом на борту, а есть демобордик с циклончиком. Насколько я понял еще никто не юзал данную область. Ну чтож попробую сам запустить

-

Спасибо за предложение, но если бы планировал запустить какую-нибудь платформу из РТОС я так и задал бы вопрос. А кнопочки/окошечки только первый шаг....

-

Поработав некоторое время с Sopc пришла идея : можно-ли работать на ПЛИС без управления извне (комп, переключатели и т.д.), а ведущим. И здесь поднялся вопрос визуализации. Консоль конечно хорошо, но хотелось бы еще лучше. Запустив проект работающий с VGA (только передача на монитор) понял тоже маловато не хватает окошек, кнопок и т.д. Покопался наткнулся на uLinux на платформе Sopc. Вот как-то так

-

Уважаемые форумчане если кто уже умудрился запустить операционную систему Linux на базе альтеры поделитесь пожалуйста информацией. Если не жалко не только ссылками на ресурсы, но и скриншотами, описаниями и т.д. Насколько я понял для минимального набора нужно собрать Nios fast с кешем, задействовать внутреннюю или внешнюю память, jtag, epcs, sysid. Собрать и загрузить например на SD карту Linux. И начинаются вопросы: как запустить загрузку операционки и вывести на монитор .....

-

Загрузка в epcs

RamZoom опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Уважаемые помогите разобраться с проблемкой!!! Собрал проект с участием NiosII, jtag, epcs_flash_controller, pio(для светодидов) и разместил все в SSRAM. Использую Quartus 10.1, SOPC Builder, NiosII IDE. Залил проект в альтеру, запустил отладку с устройством все заработало, светодиоды загораются. Решил оставить проект на постоянку в памяти зашел в NiosII IDE все размещено в SSRAM. Выбираю Program memory(.text) и Read_only data memory -- вместо SSRAM – epcs_flash_controller пытаюсь пересобрать и получаю 2 ошибки: ld: address 0x104348 of blank_project_0.elf section .epcs_flash_controller is not within region epcs_flash_controller ld: region epcs_flash_controller is full (blank_project_0.elf section .text). Region needs to be 6852 bytes larger. Как можно победить данную беду? -

Если можно поподробнее о инициализации памяти

-

Дело в том, что я использую не Nios II 10.1 Software Build Tools for Eclipse, а Nios II 10.1 IDE. Прописываю тестбенч в топ левеле, имитурую тактовый сигнал, выставляю reset_n в 1, запускаю моделирование (ModelSim 10.2c) и на выходе вижу только свои сигналы (которые сам сформировал), а реакция процессора 0. Хотя sof или jjc если заливаю, то полноценно работает

-

Да хотелось бы смоделировать работу процессора

-

Sopс + ModelSim

RamZoom опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Уважаемые подскажите как запустить тестбенч в ModelSim, который создается при компиляции в Eclipce? Можно-ли прописать и запустить процессор на свеом тестбенче? Пробовал запустить по описанию из an351 при прописывании "run 2 ms" выдает ошибку загрузки файла. Заранее спасибо -

SDC-файл

RamZoom ответил RamZoom тема в Языки проектирования на ПЛИС (FPGA)

Спасибо всем откликнувшимся!!! Разобрался. Кстати до этого в ModelSim на некоторые проекты не удавалось запустит GateLevel моделирование. Выдачи конкретной ошибки не было, только сслылка на неудачную загрузку проекта. Разобравшись с времянками проекты моделируются -

SDC-файл

RamZoom опубликовал тема в Языки проектирования на ПЛИС (FPGA)

В одной из предыдущих тем было обсуждение временных задержек и было описание "set_output_delay констрейнт в SDC-файле". Если кто в курсе поясните: это синтезируемо или только для тестбенча? Что за SDC файл, где находится и чем редактируется. До этого не сталкивался, а сейчас попробовал поработать на частоте 100МГц и на выходной параллельной восьмиразрядной шине обнаружил разбежку, причем данные не всегда достоверны (джиттер и на одной из линий не попадает под фронт сигнала). В частности интересует под QuartusII verilog. И вообще какие есть способы управления времянками? пробовал useioff не помогло -

На сайте есть интересующее ВАС описание с поясненииями под разные форматы http://we.easyelectronics.ru/plis/generato...os-na-fpga.html

-

Программатор для Xilinx

RamZoom опубликовал тема в Работаем с ПЛИС, области применения, выбор

Уважаемые форумчане подскажите реально реализовать USB программатор для Xilinx на FT232 или подобных? Если кто делал скиньте пожалуйста описание с конфигурацией микросхемы. -

Пробовал. Пересобрал Nios, Eclipse, откомпилировал заново проект в Quartus, прошил sof файлом, а изменений нет. Прошивается то, что было до подключения в проект Nios_овских файлов

-

Уважаемые форумчане подскажите пожалуйста где взять лицензию для QuarusII с Nios, которая компилирует полноценный sof файл, а не time_limited.sof

-

Формулы в цифровой обработке

RamZoom ответил RamZoom тема в Алгоритмы ЦОС (DSP)

Всем спасибо. Разобрался. Тему можно закрывать -

Формулы в цифровой обработке

RamZoom ответил RamZoom тема в Алгоритмы ЦОС (DSP)

Повторюсь, что необходимо определить сколько было сигналов с какой частотой, амплитудой и фазой во входном сигнале. Через каждые 20 микросекунд будет импульс, информирующий о начале измерений, относительно него и нужно определить фазу. Не могли бы Вы указать формулы по которым получаете значение амплитуды, частоты и фазы?