-

Постов

130 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные pavlovconst

-

-

Используйте клок, которым защелкиваете триггеры CCLK* и D*. Пусть вас не смущает, что CCLK* - это тактовый сигнал для приемной стороны. Для прошивающей ПЛИС - это сигнал данных.

Относительно клока определите set_output_delay для всех сигналов CCLK* и D*. Вот подсказка https://www.xilinx.com/video/hardware/setting-output-delay.html

-

4 hours ago, dxp said:

Время что-то очень коротким вышло

Ну, у тебя топовое железо, результат предсказуемо хороший 🙂 Добавлю в статистику.

Если в коде увеличить значения параметров WIDTH и LENGTH, то можно получить проект любого необходимого объёма. Только статистику придется набирать с нуля.

-

On 4/24/2024 at 4:48 AM, dxp said:

Показать: конфигурация РС, время сборки

Всем привет! Я когда-то делал сравнение времени сборки одного и того же RTL проекта на разном оборудовании, код на гитхабе. Результаты экспериментов тут.

Тестовый проект небольшой, чтобы была возможность консистентно протестировать мелкие ПЛИСки типа iCE40.

Если интересно, присылайте результаты прогона на вашем железе 🙂

-

2 minutes ago, Worldmaster said:

В этом модуле 50 МГц нигде нет

Не спорьте с компьютером 😆 В тайминг репорте красным по белому написано имя 50MHz-ового сигнала, который влияет на 160MHz сигнал

-

Расшифрую немного. Сейчас вы видите в отчете что-то, чего сами не задумывали в дизайне. Значит, IDE собирает какой-то другой проект, НЕ ВАШ. И собирает его неправильно. Вам нужно детально проанализировать каждую строчку репорта - посмотреть код, посмотреть схему, проверить тактирование всех участвующих сигналов. Если IDE говорит, что есть пересечение клоков - то так оно и есть. По крайней мере, в "её" проекте. Вопрос только "где?" и "как это исправить?".

В одной и предыдущих ваших тем на форуме мы уже обсуждали этот момент. С помощью констрейнов можно легко заглушить все нарушения. Но вам-то, наверное, не отчеты нужны, а работающий дизайн. Поэтому, скорее всего, каждая красная строчка отчета потребует некоторых доработок по коду. Где-то нужно будет добавить синхронизаторы, а где-то - констрейны. Каждый случай потребуется разбирать отдельно, и на форуме это сделать сложно. Почитайте книжки, которые я прикрепил, это самая лучшая литература по теме.

-

1

1

-

-

Тут не пример нужен, а стремление разобраться в теме.

Вот страничка с хорошими ссылками на литературу https://support.xilinx.com/s/question/0D52E00006hpUmcSAE/clock-crossing-guide?language=en_US

"Лучше день потерять, потом за 5 минут долететь" 😊

-

Привет! Вручную расставлять логику на кристалле можно, но в вашем случае никак не решит проблему. Любая IDE (даже Gowin 😆) сделает это эффективнее и быстрее.

Обратите внимание на первопричину, почему появляются красные отчеты? Потому что клоки From и To разные. Решайте ЭТУ задачу, она хрестоматийная!

-

Среда вам подсказывает, что в этих путях есть переход между тактовыми доменами. В тракт сигнала необходимо добавить синхронизаторы. Когда вы, как разработчик, будете уверены, что CDC сделаны корректно, можно будет написать констрейнт set_false_path.

Если просто написать констрейнты, ничего не меняя в коде - вы только замаскируете проблему. Так лучше не делать )

-

Всем привет!

У меня ПЛИС GW2AN-UV9XUG400C7/I6. Сделал проект с OSER10 + IDES10 + IODELAY. Используются дифференциальные буфера True LVDS с внешним согласованием.

При скоростях 100Mbps (на линии) и ниже проект работает, а на 1000Mbps - гарантированно НЕ работает. Периодически с сердеса поступают последовательности в 10 и более нулей или единиц, что в принципе невозможно при использовании 8b10b кодирования, как у меня.

Поделитесь пожста опытом, кто-то вообще запускал ПЛИС этой серии на скоростях под 1Gbps. Они в принципе могут в таком режиме работать?

А если кто-то запускал - требовались ли для этого жесткие констрейны типа LOC-ов или прибитых гвоздями тактовых линий? От GOWIN конкретных рекомендаций я не видел, в логах тоже ничего страшного не вижу. Но по опыту реализации подобных проектов на Cyclone V я помню, что там требований было много (например использовать строго определенную PLL, ближайшую к IO банку, и специализированный тактовый буфер)

-

Привет! Я немного опоздал, но все же дополню 😃

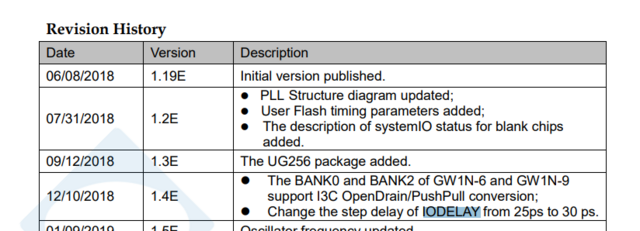

В даташите на GW1N нашел такую запись

Видимо, 25ps было задокументировано изначально, затем документация была поправлена, а модели - нет.

Почему написали новые значения? Я предположу, потому что задержки IODELAY некалиброваннные (в отличие от Xilinx-а) и в разных PVT условиях могут отличаться. Возможно, перестраховались и вписали самый плохой случай...

-

Первый вариант - перед UART_TX поставить FIFO для того чтобы временно хранить отправляемые данные. А для записи в FIFO написать арбитр, который будет собирать с N модулей данные. Поскольку N модулей могут захотеть писать в UART одновременно - можно предложить второй вариант - в каждом из N модулей по небольшому FIFO, а затем самописный модуль-арбитр, который последовательно или по приоритету забирает данные из FIFOшек и скармливает блоку UART_TX

Основная идея - UART_TX нужно переделать, чтобы он получал данные побайтно, потоком

-

Не выдумывайте велосипед. Всё уже сделано за вас, в стандартном IP-ядре от Xilinx. Называется IBERT

Указываете необходимые лейны для проверки, генерируете example design, зашиваете. Прямо в интерфейсе Vivado будет показано количество ошибок, BER, и даже глазковая диаграмма (если нужно)

-

-

@1891ВМ12Я Может показаться, что все идеи на поверхности - читай мануал, настраивай трансиверы - и получи синхронную работу устройств. Но, в действительности, GTH-ы и телекоммуникационное оптическое оборудование никогда не создавалось для синхронизации времени. В типичной задаче нужно лишь достоверно передать поток данных, а с каким фазовым набегом он будет получен - неважно.

Производители не гарантируют характеристики, на которые такая система будет опираться. Весь путь проб и ошибок придется пройти самому. Поэтому, отладка такой системы может легко стоить десяток-другой человеко-лет.

-

Цена 24 999р + доставка

-

Terasic DE10-Nano вот такая

ПЛИС FPGA Intel Altera Cyclone V SoC

Система на кристалле с аппаратными ARM ядрами

Встроенный программатор отладчик USB Blaster

Arduino shield разъемыВ комплекте

- отладочная плата с дополнительным радиатором

- оригинальный блок питанияПлата в работе не была.

Включалась пару раз для проверки.Цена 29 999 р., Санкт-Петербург

-

Говорят http://course.ece.cmu.edu/~ece545/F10/resources/Virtex5/xapp918.pdf, что в ISE есть инкрементальная компиляция. Она позволит вам зафиксировать разводку "ядра" проекта. Но проблема подсовывания различных ucf остается. Тут подсказать не могу, я мало работал с ISE.

-

1

1

-

-

Конечно, ваша задача решается с помощью скриптов. Компиляцию в ISE можно запускать из командной строки. Например, вот - https://github.com/duskwuff/Xilinx-ISE-Makefile

Значит, берем любой скриптовый язык, и пишем "запустить ISE 20 раз в параллель".

Я бы делал не один проект с разными настройками, а создал бы 20 проектов, ссылающихся на одни и те же файлы исходников.

-

1

1

-

-

44 minutes ago, maxics said:

вы на линуксовой машине собирали?

Да, но только пытался 🙂. Без старой Вивады ничего не получится

-

Попробовал собрать у себя на машине. Падает с ошибкой

ERROR: This script was generated using Vivado <2015.4> and is being run in <2021.2> of Vivado. Please run the script in Vivado <2015.4> then open the design in Vivado <2021.2>. Upgrade the design by running "Tools => Report => Report IP Status...", then run write_bd_tcl to create an updated script.Придется вам еще и древнюю Виваду ставить 😬

-

Надо написать ./build.sh prj v1

prj - выбор имени проета Vivado

v1 - версия. Писать нужно именно так, потому что в инструкции автор их так называет

Что возвращает команда?

Команда должна запустить Виваду, в логе должна быть подробная информация, что происходит

-

Открываете папку проета. Прямо в адресной строке проводника, там где обычно путь к папке - набираете mintty[Enter]. Откроется командная строка линукс. Набираете команду ./build.sh <Project Name> <Version>, подставляя аргументы в соответствии с инструкцией...

-

Да, с помощью Cygwin

-

Надо начать с чтения README. Там есть раздел как собрать проект. Нужно запускать build.sh скрипт, это предполагает наличие ОС линукс и минимальных знаний по использованию командной строки. Действуйте строго по инструкции.

Где посмотреть максимальную рассеиваемую мощность для Ultrascale?

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Дело же не только в заполненности, но и в среднем Toggle rate вашего дизайна.

Тепловыделение большинства проектов ПЛИС очень далеко от максимального, которое будет при TR 100%.

Можно написать тестовый проект, который будет иметь требуемый объем, и TR 100%, но, скорее всего, перегрузит он систему питания на плате, а не корпус ПЛИС.