Balabes

Участник-

Постов

66 -

Зарегистрирован

-

Посещение

Весь контент Balabes

-

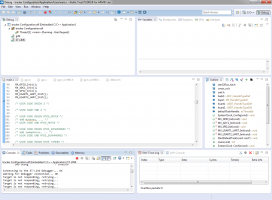

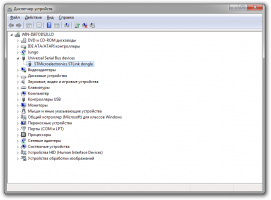

здравствуйте. Проблему локализовал, требуется помощь в устранении. как видно на скрине сверху что мой таймер зарегистрирован как прерывание номер 61, но мне нужно прерывание №61 в GIC а не в системе. Как я понял до какой-то версии ядра, это было одно и тоже. Теперь нет. Как найти нужный номер прерывания, я не могу понять. Люди писали что через res = platform_get_resource(ofdev, IORESOURCE_IRQ, 0); или platform_get_irq(pdev, 0); но у меня почему то не получилось. Подскажите, кто что сможет

-

Снова здравствуйте! Модуль собрал, через insmod запускаю, таймер настраивается, тикает, судя по регистру состояния прерывание срабатывает (8 бит равен 1), но вот обработчик не вызывается. Есть у знающих идеи что я делаю не так? #include <linux/kernel.h> #include <linux/module.h> #include <linux/interrupt.h> #include <linux/irq.h> #include <linux/platform_device.h> #include <linux/slab.h> #include <asm/io.h> MODULE_LICENSE("GPL"); #define DEVICE_NAME "xilaxitimer" #define IRQ_NUM 61 #define XIL_AXI_TIMER_BASEADDR 0x42800000 #define XIL_AXI_TIMER_HIGHADDR 0x4280FFFF #define XIL_AXI_TIMER_TCSR_OFFSET 0x0 #define XIL_AXI_TIMER_TLR_OFFSET 0x4 #define XIL_AXI_TIMER_TCR_OFFSET 0x8 #define XIL_AXI_TIMER_CSR_INT_OCCURED_MASK 0x00000100 #define XIL_AXI_TIMER_CSR_CASC_MASK 0x00000800 #define XIL_AXI_TIMER_CSR_ENABLE_ALL_MASK 0x00000400 #define XIL_AXI_TIMER_CSR_ENABLE_PWM_MASK 0x00000200 #define XIL_AXI_TIMER_CSR_INT_OCCURED_MASK 0x00000100 #define XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK 0x00000080 #define XIL_AXI_TIMER_CSR_ENABLE_INT_MASK 0x00000040 #define XIL_AXI_TIMER_CSR_LOAD_MASK 0x00000020 #define XIL_AXI_TIMER_CSR_AUTO_RELOAD_MASK 0x00000010 #define XIL_AXI_TIMER_CSR_EXT_CAPTURE_MASK 0x00000008 #define XIL_AXI_TIMER_CSR_EXT_GENERATE_MASK 0x00000004 #define XIL_AXI_TIMER_CSR_DOWN_COUNT_MASK 0x00000002 #define XIL_AXI_TIMER_CSR_CAPTURE_MODE_MASK 0x00000001 #define TIMER_CNT 0x0000FFFF static struct platform_device *pdev; void *dev_virtaddr; static int int_cnt; static irqreturn_t xilaxitimer_isr(int irq,void*dev_id) { unsigned int data; /* * Check Timer Counter Value */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCR_OFFSET); printk("xilaxitimer_isr: Interrupt Occurred ! Timer Count = 0x%08X\n",data); /* * Clear Interrupt */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data | XIL_AXI_TIMER_CSR_INT_OCCURED_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); /* * Disable Timer after 100 Interrupts */ int_cnt++; if (int_cnt>=100) { printk("xilaxitimer_isr: 100 interrupts have been occurred. Disabling timer"); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data & ~(XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK), dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); } return IRQ_HANDLED; } static int __init xilaxitimer_init(void) { unsigned int data; int_cnt = 0; printk(KERN_INFO "xilaxitimer_init: Initialize Module \"%s\"\n", DEVICE_NAME); /* * Register ISR */ if (request_irq(IRQ_NUM, xilaxitimer_isr, 0, DEVICE_NAME, NULL)) { printk(KERN_ERR "xilaxitimer_init: Cannot register IRQ %d\n", IRQ_NUM); return -EIO; } else { printk(KERN_INFO "xilaxitimer_init: Registered IRQ %d\n", IRQ_NUM); } /* * Map Physical address to Virtual address */ dev_virtaddr = ioremap_nocache(XIL_AXI_TIMER_BASEADDR, XIL_AXI_TIMER_HIGHADDR - XIL_AXI_TIMER_BASEADDR + 1); /* * Set Timer Counter */ iowrite32(TIMER_CNT, dev_virtaddr + XIL_AXI_TIMER_TLR_OFFSET); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TLR_OFFSET); printk("xilaxitimer_init: TLR 0x%08X\n",data); /* * Set Timer mode and enable interrupt */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data | XIL_AXI_TIMER_CSR_INT_OCCURED_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); printk("xilaxitimer_init: empty TCSR 0x%08X\n",data); iowrite32(XIL_AXI_TIMER_CSR_LOAD_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(XIL_AXI_TIMER_CSR_ENABLE_INT_MASK | XIL_AXI_TIMER_CSR_AUTO_RELOAD_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(XIL_AXI_TIMER_CSR_DOWN_COUNT_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); printk("xilaxitimer_init: full TCSR 0x%08X\n",data); /* * Register Device Module */ pdev = platform_device_register_simple(DEVICE_NAME, 0, NULL, 0); if (pdev == NULL) { printk(KERN_WARNING "xilaxitimer_init: Adding platform device \"%s\" failed\n", DEVICE_NAME); kfree(pdev); return -ENODEV; } /* * Start Timer */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data | XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); printk("xilaxitimer_init: TCSR 0x%08X\n",data); printk("xilaxitimer_init: timer started\n"); /*int i = 0; for (i; i < 50; i++) { data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCR_OFFSET); printk("xilaxitimer_init: XIL_AXI_TIMER_TCR_OFFSET 0x%08X\n",data); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); printk("xilaxitimer_init: XIL_AXI_TIMER_TCSR_OFFSET 0x%08X\n",data); }*/ return 0; } static void __exit xilaxitimer_edit(void) { /* * Exit Device Module */ iounmap(dev_virtaddr); free_irq(IRQ_NUM, NULL); platform_device_unregister(pdev); printk(KERN_INFO "xilaxitimer_edit: Exit Device Module \"%s\".\n", DEVICE_NAME); } module_init(xilaxitimer_init); module_exit(xilaxitimer_edit); MODULE_AUTHOR ("Xilinx"); MODULE_DESCRIPTION("Test Driver for Zynq PL AXI Timer."); MODULE_LICENSE("GPL v2"); MODULE_ALIAS("custom:xilaxitimer");

-

Чисто теоретически да, по уарту мк должен прошиваться. Только надо смотреть какие ноги мк для этого дергать надо: ресет и может быть ещё что-то

-

Вы скорее всего встречали этот гайд, но вдруг нет. Файловую систему можно взять и ту что петалинукс сделает, но в убунте и gcc есть и даже apt ссыль

-

sheynmanyu использую последний петалинукс, долго искал указание на то из какой ветки исходники, вот лучшее что нашел [core] repositoryformatversion = 0 filemode = true bare = true [remote "origin"] url = https://github.com/Xilinx/linux-xlnx.git fetch = +refs/*:refs/* mirror = true надеюсь будет полезна эта ссылка, если такой же дурачок как и я вдруг этим займется тык faa, если я все правильно понял, мне нужно добавить модуль в ядро, содержащий обработчик прерывания. А можно прерывания обрабатывать в коде из SDK? знаю что вопрос нубский, но да, я нуб(

-

За тег спасибо, на панельке его почему то нет. Вы хотите сказать что в конфигураторе ядра который с петалинуксом идет, нельзя настроить эту функцию?

-

Здравствуйте! Хочу обработать прерывания от AXI Timer в линуксе. На сайте xilinx нарыл пример. #include <linux/kernel.h> #include <linux/module.h> #include <linux/interrupt.h> #include <linux/irq.h> #include <linux/platform_device.h> #include <linux/slab.h> #include <asm/io.h> MODULE_LICENSE("GPL"); #define DEVICE_NAME "xilaxitimer" #define IRQ_NUM 91 #define XIL_AXI_TIMER_BASEADDR 0x41C00000 #define XIL_AXI_TIMER_HIGHADDR 0x41C0FFFF #define XIL_AXI_TIMER_TCSR_OFFSET 0x0 #define XIL_AXI_TIMER_TLR_OFFSET 0x4 #define XIL_AXI_TIMER_TCR_OFFSET 0x8 #define XIL_AXI_TIMER_CSR_INT_OCCURED_MASK 0x00000100 #define XIL_AXI_TIMER_CSR_CASC_MASK 0x00000800 #define XIL_AXI_TIMER_CSR_ENABLE_ALL_MASK 0x00000400 #define XIL_AXI_TIMER_CSR_ENABLE_PWM_MASK 0x00000200 #define XIL_AXI_TIMER_CSR_INT_OCCURED_MASK 0x00000100 #define XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK 0x00000080 #define XIL_AXI_TIMER_CSR_ENABLE_INT_MASK 0x00000040 #define XIL_AXI_TIMER_CSR_LOAD_MASK 0x00000020 #define XIL_AXI_TIMER_CSR_AUTO_RELOAD_MASK 0x00000010 #define XIL_AXI_TIMER_CSR_EXT_CAPTURE_MASK 0x00000008 #define XIL_AXI_TIMER_CSR_EXT_GENERATE_MASK 0x00000004 #define XIL_AXI_TIMER_CSR_DOWN_COUNT_MASK 0x00000002 #define XIL_AXI_TIMER_CSR_CAPTURE_MODE_MASK 0x00000001 #define TIMER_CNT 0xF8000000 static struct platform_device *pdev; void *dev_virtaddr; static int int_cnt; static irqreturn_t xilaxitimer_isr(int irq,void*dev_id) { unsigned int data; /* * Check Timer Counter Value */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCR_OFFSET); printk("xilaxitimer_isr: Interrupt Occurred ! Timer Count = 0x%08X\n",data); /* * Clear Interrupt */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data | XIL_AXI_TIMER_CSR_INT_OCCURED_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); /* * Disable Timer after 100 Interrupts */ int_cnt++; if (int_cnt>=100) { printk("xilaxitimer_isr: 100 interrupts have been occurred. Disabling timer"); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data & ~(XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK), dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); } return IRQ_HANDLED; } static int __init xilaxitimer_init(void) { unsigned int data; int_cnt = 0; printk(KERN_INFO "xilaxitimer_init: Initialize Module \"%s\"\n", DEVICE_NAME); /* * Register ISR */ if (request_irq(IRQ_NUM, xilaxitimer_isr, 0, DEVICE_NAME, NULL)) { printk(KERN_ERR "xilaxitimer_init: Cannot register IRQ %d\n", IRQ_NUM); return -EIO; } else { printk(KERN_INFO "xilaxitimer_init: Registered IRQ %d\n", IRQ_NUM); } /* * Map Physical address to Virtual address */ dev_virtaddr = ioremap_nocache(XIL_AXI_TIMER_BASEADDR, XIL_AXI_TIMER_HIGHADDR - XIL_AXI_TIMER_BASEADDR + 1); /* * Set Timer Counter */ iowrite32(TIMER_CNT, dev_virtaddr + XIL_AXI_TIMER_TLR_OFFSET); data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TLR_OFFSET); printk("xilaxitimer_init: Set timer count 0x%08X\n",data); /* * Set Timer mode and enable interrupt */ iowrite32(XIL_AXI_TIMER_CSR_LOAD_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(XIL_AXI_TIMER_CSR_ENABLE_INT_MASK | XIL_AXI_TIMER_CSR_AUTO_RELOAD_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); /* * Register Device Module */ pdev = platform_device_register_simple(DEVICE_NAME, 0, NULL, 0); if (pdev == NULL) { printk(KERN_WARNING "xilaxitimer_init: Adding platform device \"%s\" failed\n", DEVICE_NAME); kfree(pdev); return -ENODEV; } /* * Start Timer */ data = ioread32(dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); iowrite32(data | XIL_AXI_TIMER_CSR_ENABLE_TMR_MASK, dev_virtaddr + XIL_AXI_TIMER_TCSR_OFFSET); return 0; } static void __exit xilaxitimer_edit(void) { /* * Exit Device Module */ iounmap(dev_virtaddr); free_irq(IRQ_NUM, NULL); platform_device_unregister(pdev); printk(KERN_INFO "xilaxitimer_edit: Exit Device Module \"%s\".\n", DEVICE_NAME); } module_init(xilaxitimer_init); module_exit(xilaxitimer_edit); MODULE_AUTHOR ("Xilinx"); MODULE_DESCRIPTION("Test Driver for Zynq PL AXI Timer."); MODULE_LICENSE("GPL v2"); MODULE_ALIAS("custom:xilaxitimer"); собираю образ и файловую систему. загружается. все отлично. но в /usr/include/linux нет <linux/interrupt.h> и других. понимаю что нужно в конфиге ядра или файловой системе что-то сделать. Кто опытен в линуксах на цинке подскажите как быть. т.к. опыта особого ни в цинке ни в линуксе не имею.

-

Печатка для SIM900D

Balabes ответил serega98700 тема в Сотовая связь и ее приложения

Уважаемый CADiLO, где-то тут мелькало про подтяжку RX, в HD к 900D вроде нет про это ничего. Это было в других модулях или все же надо? -

Печатка для SIM900D

Balabes ответил serega98700 тема в Сотовая связь и ее приложения

Еще один маленький вопрос, если powerkey повесить на землю то модуль включится как только появится питание? без всяких кнопок. естественно через резистор, 4,7к должно хватить -

Печатка для SIM900D

Balabes ответил serega98700 тема в Сотовая связь и ее приложения

А, они внутри соединены? а то как то в sim900d_hardware_design_v2.02_0.pdf этот момент не уточняется. Значит придется вот так. В данном случае батарейка от нокии и будет питаться от батарейки и когда будет 5В, будет её заряжать. если я все правильно понял -

Печатка для SIM900D

Balabes ответил serega98700 тема в Сотовая связь и ее приложения

Здравствуйте. Тоже под этот модуль делаю схему. Я как то не совсем понял про питание. У него два пина VBAT, на них надо одно и тоже подавать? или я могу на один пустить 4В а к другому литиевый аккум и он сам умный разберется чем питаться? -

Нашел в чем дело. Проект сгенерированный CubeMX первым делом вызывает HAL_Init(); В ней вызывается функция HAL_MspInit а уже она в свою очередь вырубает jtag и swd полностью /**DISABLE: JTAG-DP Disabled and SW-DP Disabled */ __HAL_AFIO_REMAP_SWJ_DISABLE(); Будьте внимательны!

-

http://www.atollic.com/index.php/kb/11-st_...ng/11-kb_stlink http://www.atollic.com/index.php/kb/3-debu...onnection_error Это не помогло(

-

У меня и truestudio с st-link как-то не дружит. Уже на двух машинах с Win7x64 одинаковая ситуация. GDB_server запускается, дрова для st-link v2 стоят, а в консоле при запуске сами смотрите что Прошивка в ст-линк последняя. В уже названном кокосе все дебажилось. Причем если ST-Link Utility посмотреть в памяти все записано, но дебага нет. Может кто-нибудь подсказать? Тут поидеи процесс аналогичный эклипсу.

-

В общем проблема решилась обновлением CubeMX и установкой TrueSTUDIO, пока впечатления приятные он этой IDE

-

Настройка GPS приемника

Balabes ответил Balabes тема в Сотовая связь и ее приложения

Спасибо! Попробую. А можно как-то доподлинно узнать РОМ или не РОМ не вскрывая? -

Здравствуйте! Поделитесь кто-нибудь пустым проектом для IDE Coocox(1.7.8) с использованием HAL драйверов для F1. У меня чет не вышло все собрать из папки STM32Cube_FW_F1_V1.1.0 (ну или описание процесса)

-

Настройка GPS приемника

Balabes опубликовал тема в Сотовая связь и ее приложения

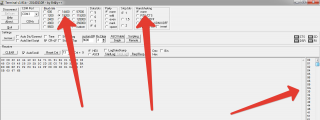

Здравствуйте! Есть приемник GlobalSat BR-355s4, хочу настроить его так что бы выключить все то, что он постоянно передает по усарту и оставить сообщение RMC по запросу. Пытался через терминал слать ему такие команды Отключить GGA $PSRF103,00,00,00,01*24 Отключить GLL $PSRF103,01,00,00,01*25 Отключить GSA $PSRF103,02,00,00,01*26 Отключить GSV $PSRF103,03,00,00,01*27 Отключить RMC $PSRF103,04,00,00,01*20 Запросить RMC $PSRF103,04,01,00,00*20 Отключить VTG $PSRF103,05,00,00,01*21 И пробовал несколько приложений для работы с приемниками (MiniGPS, GeoSDemo), ничего не вышло. подскажите где я ошибся? -

Спасибо, почитаю! По первому сообщению ТС очень похоже на то что мне надо

-

а как быть если пришло 138 байт? 100 я в прерывании увижу, а дальше?нужно знать когда кончились данные

-

Здравствуйте! Хочется, но не можется пока что реализовать глобальный счетчик. Поясняю, включается ДМА и начинает забирать с УАРТа в массив (допустим DMA_BufferSize= 50), счетчик ДМА начинает уменьшаться с каждым принятым байтом на 1. Все это происходит в режиме Circular, т.е. дойдя до 0 ДМА начнет переписывать массив с начала и счетчик снова станет = 50. Хотелось бы Глобальный счетчик, так что бы считал не кол-во байт до конца (как стандартно делает ДМА) а общее кол-во принятых. Пытался в прерывании по USART RXNE считать, но как я понял проц не выходит из прерывания, хотя флаг должен чистить ДМА при чтении из USART->DR. Может кто-то так делал?

-

void USART_SendSymbol(USART_TypeDef *USARTx, uint8_t data) { while((USART_GetFlagStatus(USARTx, USART_FLAG_TC)) == RESET); USART_SendData(USARTx, data); } и USART2->DR = RXBuf Аналогичные результаты дает. и даже на скоростях 115200 и 256000 тоже самое, попробую другой терминал на 115200 в Putty все нормально.

-

с чего бы ей 10 раз прислать что надо, а потом хрень?) тем более что я делал прием трех пакетов и если их принять, а потом выкинуть в усарт то все нормально было

-

как видите вот так RXBuf = read_data_reg(); USART_SendSymbol(USART2, RXBuf); STATE++; вот это некорректно принимает только до А нормально, потом хрень какая то. write_data_reg(outb); outb = outb + 0x01; write_command_reg(0x05); STATE++;

-

модем это FX919 - и пока пытаюсь реализовать так называемый прозрачный режим, после 2х синхропосылок отправляю некоторые байты по одному непрерывно. а приняв их хочу выкинуть их в усарт. вот и хотелось бы что бы проц вынимал из модема новые байты и просто клал их куда-то а они дальше сами отправлялись что бы он успел взять все байты и не потерять, он же не сможет принять следующий байт пока я не достану этот. По скорости вроде запас есть, т.к. сам модем работает на 9600 (если кондюки и кварц сильно не врут) а усарт 19200. Так вот успеет ли f107 достать байт и положить его в усарт? когда передавал пакеты по 10\12\7 байт первые 10 принимал, но пока их отправлял второй и третий пакетик уже не успевал принять правильно (это было для тренировки, реализовывать решено начать именно с режима по байту). Пакеты будут позже.