lennox

-

Постов

77 -

Зарегистрирован

Сообщения, опубликованные lennox

-

-

16 minutes ago, petrov said:

интуитивно подозреваю, что нужно чтобы 2 точки были правее и 2 точки левее

Именно, для точек посередине линии задержки больше всего информации для интерполяции. Использовал только с оптимальным диапазоном 0..1.

не могли бы Вы привести ссылку, на модель в которой нет ошибки?

Таких нет, во всех какие-то ошибки. :)

Посмотрите более поздние.

спасибо!

-

7 minutes ago, petrov said:

Там ошибка, оптимальный диапазон mu 0..1 -> z^-2..z^-1.

вопрос может и глупый, я только начал. а из чего это следует?

если я хочу сделать mu 1..2, что для этого нужно?

интуитивно подозреваю, что нужно чтобы 2 точки были правее и 2 точки левее, поэтому когда фиксируем индексы как:

[-1 0 1 2] -> mu = [0..1]

[0 1 2 3] -> mu = [1..2]

[-2 -1 0 1] -> mu = [-1..0]

после вычисления обратной матрицы получаем требуемые коэффициенты. верно?

не могли бы Вы привести ссылку, на модель в которой нет ошибки?

-спасибо!

-

Здравствуйте.

Разбираюсь с символьной синхронизацией, а точнее с ресемплером по схеме Фарроу.

Вот не могу понять чем определяется оптимальный диапазон mu? От того как зафиксированны индексы отсчетов?

Вот я зафиксировал индексы по оси времени как [-1 , 0 , 1 , 2] и посчитал обратную матрицу в Maple (как написано на dsplib) то коэффициенты получаются соответствуют схеме из моделей petrov'a.

Запустил модель petrov'a - там видно что мю в диапазоне от [-1..0]. Почему?

на сайте дсплиб оси зафиксированны вот так [-2 -1 0 1]. Коэффициенты немного другие. Какой там диапазон мю, как это понять?

P.S.

Еще вопрос, почему в некоторых схемах petrov'а в сумматоре кое где к timing_error прибавляется 1ца, а кое где из 1цы ошибка вычитается?

-спасибо!

-

1 hour ago, new123 said:

40 байт на 10G ethernet? =)) весь mac + ip заголовок в crc =)

что смешного? проверка crc. 40 байт (суммарная шина с 10 трансиверов). 100gbps.

-

On 2/3/2019 at 10:07 AM, new123 said:

Может кто пытался делать crc на широкой шине. Заранее благодарен за любые советы.лет 6 назад считал CRC по шине 320бит на 156.25МГц.

уже не помню как и кода нет, но помню что читал альтера кукбук (глава CRC decomposition)

-

2 hours ago, Pavel Proskura said:

В. И. Ипатов Широкополосные системы и кодовое разделение сигналов.

спасибо.

Поделитесь, пожалуйста, следующими книгами

DIXON, R. C.: ‘Spread Spectrum Systems’

DIXON, R. C.: ‘Spread Spectrum Techniques’

‘The ARRL Spread Spectrum Sourcebook’, (American Radio Relay League Inc, 1997)

Варакин. Сис-мы связи с шумоподобными сигналами

-

посоветуйте, пожалуйста, что почитать по ШПС, ППРЧ ?

есть ли книги приближенные к практической реализации?

-спасибо

-

-

On 11/7/2018 at 1:45 PM, Olga_woroncova said:

Здравствуйте! Подскажите, как смоделировать влияние на OFDM сигнал смещения относительно друг друга частот дискретизации между ЦАП и АЦП передатчика и приемника? Это явление называют sampling clock offset (SCO).

-

Здравствуйте уважаемые.

Посоветуйте отладочную плату или готовое устройство с 100g Eth портом + FPGA .

Спасибо.

точно не помню с какой работал, когда занимался 100G, но помню, что HTGххх от HighTech Global.

посмотрите там.

-

Все определяется Вашими требованиями к избирательности КВ приемника.

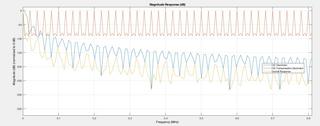

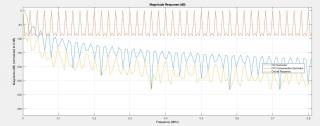

Самый простой и наглядный способ - постройте сквозную АЧХ всех каскадов фильтрации. Для этого надо импульсные характеристики всех фильтров привести к частоте дискретизации АЦП, то есть интерполировать на величину коэффициента децимации перед фильтром. Все интерполированные импульсные характеристики свернуть между собой. fvtool() от результирующей импульсной характеристики покажет сквозную АЧХ.

спасибо.

-

я не очень могу представить откуда в практических задачах мог приехать НЧ-сигнал с полосой порядка 20КГц оцифрованный на 100МГц.

опечатки нет. fs=1.5e9, bw=3.2e3 (единственный такой режим. однополосная, КВ)

100e6, 20e3 - это условный пример.

все-таки повторю вопрос , при каскадной реализации фильтров из каких условий выбирается уровень подавления в каждом следующем фильтре?

из каких условий выбирается разрядность данных между фильтрами? где бы почитать об этом на конкретном примере ?

-спасибо

-

здравствуйте.

подскажите, вот как у меня в посте выше есть cic и cfir

условно говоря, с выхода cic разрядность пусть 96 бит, это много для входа корректирующего.

Например, я округляю до 32 бит (беру старшие 32 значащих по результатам моделирования или есть другой способ? есть ли смысл окргулять по правилу 0.5 или именно так и надо? имею ввиду примерно следющее cic_out[96:65]+cic_out[64] если >0 и наоборот если отрицательный результат)

Так вот на сколько давить внеполосные сигналы в корректирующем фильтре? на 20*log10(2^32) = 193дБ ? как правильно?

-спасибо

-

спасибоПо первому вопросу:По второму:

-

Опубликовано · Изменено пользователем dcs · Пожаловаться

Здравствуйте,

подскажите как сделать так, чтобы АЧХ (CIC,CFIR,и результирующая) отображались визуально "гладко, без изломов" при увеличении для моего примера при больших коэффициентах децимации.

Начальная частота семплирования Fs = 100MHz. На выходе хочу, например, 10kHz.

data @100MHz -> CIC (decimate by 5000) -> CFIR (decimate by 2) -> data @10kHz

P.S.

можно ли отобразить результат последнего fvtool(CICDecim, CICCompDecim, filtCasc, ... от 0 до целевой 10кГц?

clc, clear, close all; %% CIC Fs_init = 100e6; % Hz CIC_output_sample_rate = 20e3; % integer multiple of Fs_init CIC_decim_factor = Fs_init/CIC_output_sample_rate; % decimatin factor CICDecim = dsp.CICDecimator( ... 'DecimationFactor', CIC_decim_factor, ... 'DifferentialDelay', 1, ... % нули АЧХ cic будут на частотах кратных 20кГц 'NumSections', 4); Gain_CIC = gain(CICDecim); f_CICDecim = fvtool(CICDecim,'Analysis','freq','ShowReference','off'); f_CICDecim.NormalizeMagnitudeto1 = 'on'; legend(f_CICDecim,'CIC decimator'); %% CFIR with decimation by 2 fs = CIC_output_sample_rate; % sample rate @compensator input fPass = 2e3; fStop = 4e3; CICCompDecim = dsp.CICCompensationDecimator(CICDecim, ... 'DecimationFactor',2, ... 'PassbandFrequency',fPass, ... 'StopbandFrequency',fStop, ... 'PassbandRipple', 0.25, ... 'StopbandAttenuation', 80, ... 'SampleRate',fs); f_CICCompDecim = fvtool(CICCompDecim,'Analysis','freq'); legend(f_CICCompDecim, 'CIC compensator decimator'); filtCasc = dsp.FilterCascade(CICDecim,CICCompDecim); f = fvtool(CICDecim, CICCompDecim, filtCasc, ... 'ShowReference','off', ... 'Fs', [fs*CIC_decim_factor fs fs*CIC_decim_factor]); f.NormalizeMagnitudeto1 = 'on'; legend(f,'CIC Decimator','CIC Compensation Decimator', ... 'Overall Response');

-спасибо

-

решили вопрос?

Я лепил Matlab2016b + ISE14.7 sysgen нa Linux Mint 18.1 Serena.

С форумов ничо не помогло - переписал ихние скрипты, поудалял из них awk (большой опыт в линуксе)

нет не получилось.

пришлось поставить виртулку с win7 и там все развернуть.

но если поможете, буду благодарен)

-

Опубликовано · Изменено пользователем dcs · Пожаловаться

Тогда вопросы:какая ОС, есть ли в списке поддерживаемых (и Matlab и Vivado)

версия Matlab

версия Vivado

Куда и как поставлены Matlab и Vivado?

Про ключи/лицензии пока не надо :)

1.

установлена Linux Mint 18.3 (based on Ubuntu 16.04.3 LTS согласно википедии)

в списке поддерживаемых она есть (согласно ug973):

Linux Support• Red Hat Enterprise Workstation/Server 7.2, 7.3, and 7.4 (64-bit)

• Red Hat Enterprise Workstation 6.6, 6.7, 6.8, and 6.9 (64-bit)

• SUSE Linux Enterprise 11.4 and 12.3 (64-bit)

• CentOS 7.2, 7.3, and 7.4 (64-bit)

• CentOS 6.7, 6.8, and 6.9 (64-bit)

• Ubuntu Linux 16.04.3 LTS (64-bit)

и матлаб и вивадо - сами по себе работают.

2. куда поставлен:

dcs@pc ~/Desktop $ which matlab

/usr/local/bin/matlab (реально вот стоит /usr/local/MATLAB/R2018a/bin)

dcs@pc ~/Desktop $ which vivado

/opt/Xilinx/Vivado/2018.1/bin/vivado

dcs@pc ~/Desktop $ which sysgen

/opt/Xilinx/Vivado/2018.1/bin/sysgen

вивадо 2018.1

матлаб 2018а

как поставлен?

матлаб (делал как тут снято инсталл )

далее слелал

ln -s $MATLAB/bin/matlab matlab where $MATLAB is the MATLAB installation directory.

вивадо - запустил xsetup

сначала ставил матлаб потом виваду

P.S. после запуска симулинка в библиотеке элементов - систем генератора нет.

в виндовсе при установке вивадо - он находит установленный матлаб ну и видимо добавляет все что нужно в симулинк, в линуксе он (установщик) - даже не намекнул на матлаб

вот здесь форум залинкс человеку советуют

From your xterm, type the command below (replace your_matlab_installation_root_dir with the actual directory name)sg_config -install_to_matlab your_matlab_installation_root_dir

Now manually start simulink again, and check if Xilinx Block Sets shows up.

но у меня нету sg_config

ну или я не нашел. как минимум which sg_config - ничего не выдает

в общем, помогите плиз

мне собственно сисген то сейчас не нужен, но в перпективе хочу освоить. так что надо, чтобы работал. раз взялся - надо решить проблему

-

фаа, это я смотрел

там написано

This issue has only been reported on unsupported versions of the Ubuntu operating system. However, to avoid this issue on any OS, the Vivado 2016.3 install will no longer set the LD_LIBRARY_PATH variable.у меня последняя версия 2018.1 и эта переменная не установлена.

сожержимое сеттингс64.сш

############################################################## # Copyright (c) 1986-2018 Xilinx, Inc. All rights reserved. # ############################################################## source /opt/Xilinx/DocNav/.settings64-DocNav.sh source /opt/Xilinx/Vivado/2018.1/.settings64-Vivado.sh source /opt/Xilinx/SDK/2018.1/.settings64-SDK_Core_Tools.sh

может еще что-нибудь

-

приветсвую.

не по своему желанию перешел на линукс.

сумел запустить все (виваду, матлаб, sdk), но не получается систем генератор.

вывод в консоли:

awk: symbol lookup error: awk: undefined symbol: mpfr_z_subInternal error 2: Could not determine the path of the

MATLAB root directory.

original command path = /usr/local/bin/matlab

current command path = /usr/local/bin/matlab

Please contact:

MathWorks Technical Support

for further assistance.

подскажите, пожалуйста, что и как делать?

-спасибо

-

Вот по превышению какого-то уровня на выходе модуля определяем наличие известной последовательности

а где можно почитать как этот порог задавать (вычислять) ?

-спасибо

-

здравствуйте,

хотел сделать 2 эквивалентных куска генерации входных воздействий на фифо.

initial begin fork ///////////////////////////////////////////////////////////////////////// pulse_gen: begin forever begin randcase 1: rand_pulse = 1; 5: rand_pulse = 0; endcase @(posedge aclk); end end ///////////////////////////////////////////////////////////////////////// push_data: begin wait(aresetn_done); forever begin s_axis_tlast = 0; s_axis_tuser = 0; if (s_axis_tready == 1) // FIFO ready to receive data begin s_axis_tvalid = rand_pulse; if (rand_pulse) s_axis_tdata = $urandom_range(255,0); @(posedge aclk); end else begin s_axis_tdata = 0; @(posedge aclk); end end end ///////////////////////////////////////////////////////////////////////// join_none end

и

always_ff @(posedge aclk) begin if (aresetn == 1'b0) begin s_axis_tvalid <= 0; s_axis_tdata <= 0; end else begin s_axis_tvalid <= s_axis_tready & rand_pulse; if (s_axis_tready & rand_pulse) s_axis_tdata <= $urandom_range(255,0); end end

получилось, что корка по-разному реагирует на входные воздействия в двух случаях.

в первом случае работает неверно (пропускается первый байт в пачке), во втором - все хорошо.

подскажите в чем проблема и как исправить?

спасибо.

-

"как из I/Q перейти просто к мягким решениям"

документ не смог найти у себя на компе. я считал по формулам из appnote от AHA. там на примере кам16 был показан расчет.

попробуйте найти.

вот документ китайский язык, страница 7 - там формула но это перевод оригинального аппноута))

-

Опубликовано · Изменено пользователем dcs · Пожаловаться

Хотелось бы увидеть развернутую аргументацию почему Вы считаете, что я ошибаюсь.Ответьте, пожалуйста, на несколько простых вопросов:

1) Всякую ли и всегда ли синтаксически правильную конструкцию синтезатор сможет воплотить физически в FPGA/ASIC?

2) Всякую ли и всегда ли синтаксически правильную конструкцию симулятор сможет просимулировать?

3) Зачем синтезатору нужно "уметь" код типа always @(posedge iCLK) oDONE <= А; интерпретировать как регистр?

4) Зачем симулятору нужно "уметь" код типа always @(posedge iCLK) oDONE <= А; интерпретировать как регистр?

5) В чем, на ваш взгляд, заключается разница между задачей синтеза и моделирования (симуляции)?

6) Вы все еще считаете, что я ошибаюсь?

1)нет

2)не знаю, уверен что нет!

3)за тем, что так посчитал разработчик! если он так не думает, то надо ему объяснить!! (с помощью констрейнов) есть другие варианты?

4)как иначе?

5)

6) да

-

Еще необходимо понимать, что код

always @(posedge iCLK) oDONE <= ...

только для синтезатора является регистром, а вот симулятор этот код так не интерпретирует. При этом, поведение при симуляции полностью совпадает с поведением регистра, но, повторюсь, симулятор не считает это регистром.

это еще почему? Вы ошибаетесь

Процесс разработки

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

например, https://github.com/analogdevicesinc/hdl/tree/master/library/util_wfifo