Adv

-

Постов

120 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Adv

-

-

Здравствуйте!

Ставлю Quartus 11.0 sp1 Full на ноутбук с Windows 7 Домашняя базовая. При установке драйверов USB Blaster Windows ругается, что драйвера не подписанные и отказывается их ставить (а не спрашивает: "все равно продолжить?"). Это что, фишка Домашней версии Windows 7? Сносить ее не хочется, ибо лицензионная с ноутбуком.

Может где надо что-то разрешить?

При старте - отключите обязательные подписи драйверов (при старте Винды, разумеется). Тогда начнёт спрашивать - продолжить или нет.... ну, и ставить.

-

Судя по +100 наверное кристалла?

Да. температура кристалла.

-

Можно и на ftp залить... :)

8 гигов-то.... И потом - опять официальную заливать? Народу , как вижу, это не очень надо. Если Вам требуется - дам ссылки в личку. Лежит уже у нас на сервере (не Электроникс). Другим - аналогично. Если All решит - на местный сервер заливать - залью. А сам небуду....

-

18 апреля появился Quartus II 12. Пока - cb. Многие противные глюки устранены. GUI, наконец -то, работет быстро. У меня время компиляции с 2ч 30м упало до 1ч 56 мин.

Приятно. Можно поделиться с тем, кто хочет. Или подождать официального релиза... Всётаки - бетта....

-

Нда?

И какой период зависаний? И, если не секрет, какая у Вас ОС.

Не часто. Как раньше писал - падает на работе мышью с константами. Если работать с клавы - падений нет. ОС W7 SP1 x64 лицензионная от Dell (Т7500).

-

мы легких путей не ищем

мы легких путей не ищем

Мудрость гласит - если уж совсем ничего не получается, то загляните, наконец, в инструкцию.....

-

Пока - да.

Но - поменшало их.... Можно работать.

-

Вы ещё и в VHDL ядро генерировали.....

Яcно. В VERILOG этой ошибки просто нет (при генерировании в мегавизарде выбрать VERILOG а не VHDL). Почти все (за редким исключением) ядра Алтеры - это Верилог. И для других языков - проблемы типа этой. К сведению.

С уважением Adv.

-

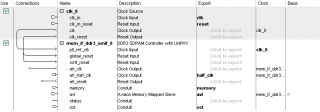

Ага, только теперь(в Квартусе11.1) нужно использовать контроллер с UniPHY, т.е. генерить не через МегаВизард (не генерится), а через qSys.

После генерации ядра с UniPHY в qSys (только DDR3-ядро) я подключил полученный компонент к своему проекту, обвязал его и... получил ошибку, что фиттер не может сделать режим open-drain для ног mem_ck[0] и mem_ck_n[0], т.е. для тактовых ног.

Может я что-то не так понимаю и делаю??

:help:

:help:Уважаемый billidean! Вы скрипты запускали перед компиляцией? Пожалуйста, почитайте это - www.altera.com/literature/hb/external-memory/emi_tut_qdr.pdf.

Это - пример использования UNI PHY, рабочий. Проверял .

В .qsf файле проекта должны быть такие (или похожие, эти - из моего проекта...) строки (это выдержка - там их много после запуска скрипта *_pin_assignments.tcl):

.................

set_instance_assignment -name INPUT_TERMINATION "PARALLEL 50 OHM WITH CALIBRATION" -to ddr3_mem_dqs_n[1] -tag __pr_16_ddr3_p0

set_instance_assignment -name OUTPUT_TERMINATION "SERIES 50 OHM WITH CALIBRATION" -to ddr3_mem_dqs_n[1] -tag __pr_16_ddr3_p0

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.5-V SSTL CLASS I" -to ddr3_mem_ck -tag __pr_16_ddr3_p0

set_instance_assignment -name OUTPUT_TERMINATION "SERIES 50 OHM WITHOUT CALIBRATION" -to ddr3_mem_ck -tag __pr_16_ddr3_p0

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.5-V SSTL CLASS I" -to ddr3_mem_ck_n -tag __pr_16_ddr3_p0

set_instance_assignment -name OUTPUT_TERMINATION "SERIES 50 OHM WITHOUT CALIBRATION" -to ddr3_mem_ck_n -tag __pr_16_ddr3_p0

set_instance_assignment -name IO_STANDARD "SSTL-15 CLASS I" -to ddr3_mem_a[0] -tag __pr_16_ddr3_p0

set_instance_assignment -name CURRENT_STRENGTH_NEW "MAXIMUM CURRENT" -to ddr3_mem_a[0] -tag __pr_16_ddr3_p0

..........

и т.д.

Нет там открытого коллектора (open-drain) и близко. Используется динамическая терминация (Dynamic ODT). Полагаю - и у Вас тоже используется.

Заранее прошу прощения , если Вы это уже читали.

p.s. На всяк случай прикрепляю пример. И вот что - если у Вас ранее отработал скрипт от Altmemphy (*_pin_assignments.tcl) - то всё равно запускайте его по-новому (от uni PHY, разумеется).

Порядок запуска скрипта ОТЛИЧАЕТСЯ от запуска в Altmemphy (!!) Будьте внимательны.

-

Здравствуйте.

Имеется проект под StratixIV на Q9.1, который качает данные в DDR3 и из нее.

Используется HPC II.

Все работает отлично.

Далее, взял этот проект и вставил его как компонент в другой проект, который создан в Q11.1.

Здесь-то и началось все веселье.

Сначала Квартус потребовал перегенерить ядро HPC II, ладно сделал, проект вроде скомпилился.

Заливаю в кристалл, обмена с DDR-кой нет.

Смотрю на SignalTap'е, сигнал local_ready='0' с самого начала, т.е. он даже не был в '1'.

Перекомпилил проект, залил, обмен есть, но поведение сигнала local_ready мне не нравится, при записи данных в DDR-ку он иногда падает в '0'.

Такого поведения от него я не видел при отладке начального проекта в Q9.1, там этот сигнал падал в '0' только при вычитывании большого объема данных из DDR-ки, когда буфер контроллера HPC II заполнялся.

Кто может что-нибудь посоветовать, как победить проблему в Q11.1???

З.Ы.: после каждой перекомпиляции поведение конртоллера HPC II меняется, и это не есть гуд.

Этот контроллер более не поддерживается для выбранного Вами семейства. Предлагают использовать ТОЛЬКО UNI PHY.

Ниже - таблица из документа Introduction to ALTMEMPHY IP (http://www.altera.com/literature/hb/external-memory/emi_altmemphy_ref_intro.pdf)

Table 13–3. Device Family Support

Device Family

Protocol

DDR and DDR2 DDR3

Arria® GX Final No support

Arria II GX Final Final

Cyclone® III Final No support

Cyclone III LS Final No support

Cyclone IV E Final No support

Cyclone IV GX Final No support

HardCopy II Refer to the What’s New in Altera

IP page of the Altera website. No support

Stratix® II Final No support

Stratix II GX Final No support

Other device families No support No support Почёркнуто мной.

Предупреждаю - тот с ещё большими причудами. Там процессорная система для калибровки (в самом ядре). Особенно если у Вас высокая частота (на прим. 533МГц)

И причуды - сама версия 11.1. Со вторым сервиспаком, вроде получше, а до этого - регенерировать систему (использую QSYS) было просто невозможно - всё падало. Пересоздавал проект - работает как часы. Регенерирую - всё валится снова....

Однако, было бы несправедливо не сказать - эта самая система "вытягивает" почти безнадёжные (с точки зрения правильности трассировки - их бракует HL2010, море красного...) платы. Работают без сбоев. HPC II так не может.

-

Я, конечно, не скажу за всю Альтеру, :) но попробую объяснить......

А происходит следующее - для нового правят - для старого - ломают. Такую банальность, как то, что одно новое исправление приходится три (новых!) ошибки я просто пропускаю. Но то, что системы с DDR3 в сервиспак 1 невозможно нормально регенерировать (тупо не работают) - факт. Причём, если создавать проект по-новой - всё летает на Ура... А что с описаниями на PHY 10G ?? Ни про смещение на 4 байта , ни про обяз. ресет. Догадайся сама.... и т.д и т.п. На кой ч..... такая поддрержка семейства (Stratix V) , которого по сути ещё нет-то?? Чтобы старое не работало? И не надо предлагать старые версии - про новый синтез все в курсе - вещь нужная и хорошая.

Хоть выговорился. Фух... Очень надеюсь на Sp2.

-

Доброго времени суток, уважаемые!

Требуется помощь. Может, кто-то сталкивался с SignalVu от Тектроникса?? Победить его счётчик количества запусков надо.

С уважением и благодарностью ко всем кто хоть чем-то поможет, Adv.

-

Спасибо,это радует.А в графике глюки так и остались?Привык топ-уровень делать в графике.

Да. Это уже, видимо, и не исправят. Да и все примеры уже написанные идут... Раньше топ-уровень все только рисовали. И ещё было замечено что в Эклипсе время от времени отваливается логин SBT. Приходится перезапускать. Причины пока не выяснили...

-

Есть отличия от v11.0?Поделитесь впечатлениями.

Впечатления более положительные, чем отрицательные. Про новый редактор уже говорили (у и меня он вываливается - на константах, их редактировании мышью в Верилоге. С клавы этого нет.)Конкретно у нас - под W7 x64 - на одной машине корректно встал Ниос, на другой нет. И заставить встать так и не получилось. GUI не работает. Кабеля не видит. В Jawa пишет, что путь не виден. С консоли - всё о'кей...

Так и запускаю. Вторая - с GUI нормально работает, так что там и пишем. Это - внешнее. Изменился сам Квартус. Синтез сущ. поменялся. По-моему - в лучшую сторону. Прога стала строже, раньше Менторовские были строже, а теперь Ментор пропустит - Квартус очень часто не пропускает. К Верилогу (написанию) строже стал особенно. Ну, и много прочего...всё не опишешь сразу. Сократилось время компиляции - ранее 2 часа 46 мин, теперь 2ч 06 мин для одного и того же проекта.

Приятно.

-

Моделсим ASE, прилагаемый к 11.1, склонен к зависаниям :(.

На сервере есть полный 10с.

-

Что есть реальные деньги?

Нам предложили за плату 380х160 прибл. 16-ти слойная - 1900$ за штуку, для заказа 3-х штук(прототипы) и это - без стоимости подготовки производства....

Думаю, это НЕ реальные деньги. Т.к. оговаривалось и дальнейшие использование материала (если принять во внимание, что меньше 30м2 матерал не продают)

-

Доброго времени суток!

Кто-нибудь может посоветовать изготовителя (или просто изготовить) PCB на FR408?? За РЕАЛЬНЫЕ деньги.

География значения не имеет.

За ранее спасибо. Отвечать можно в личную почту.

-

vadimuzzz спасибо, что не забыли! Не надо рыться..... Ещё раз спасибо!

-

Большое спасибо!

С уважением Adv.

-

я такую использую, только на 128 Мбит. все будет работать, разве что для ниосовского программера может потребоваться override файлик сделать, не проблема

Если не тяжело, можно подробнее?? Никогда других, кроме Altera флешей не использовал. Но пришла пора.....

Из документации не следует, что там что-то надо менять. Или я что-то упустил??

-

Вопрос к вам, как к мастеру по ремонту РЭА. Допустим у вас будет схема современного телевизора, нарисованная на уровне "транзисторов" (те детализировано устройство всех микросхем и тд), причем без всяких пояснений, разбиений на функциональные блоки (те одна часть блока питания на 20ом листе схемы, другая на 789, третья на 1ом и тд).

Скажите, насколько такая схема будет информативна и полезна для ремонта?

Этот человек всё это знает. Он ищет того, кто проходил это. Просто ищет готовое. Потому, что знает, насколько это сложно. Он , конечно может сказать , что мол, это не так и т.д. и т.п. Чтож, может быть я неправ. Заранее приношу извинения. Только такое у меня складывается впечатление.

Дискуссия тут дальше по-моему, просто не имеет смысла. Подчёркиваю - это только моё мнение. Не более.

С уважением ко всем Adv.

-

По-моему это просто плохая пайка BGA (ПЛИС-то EP1C12F324C8N). Актуально если отказ частичный и произошёл спотнанно.

-

У каждого свои тараканы в голове.

Именно. Раз сходивший по этому пути не пойдёт по нему вторично. Удач.

-

Ну почему, когда овчинка стоит несколько тысяч баксов, и владелец этой овчинки готов платить 50% от стоимости овчинки, то на ремонт только одной овчинки можно потратить месяц, и не беспокоится, что за этот месяц ты ничего не заработаешь. Особенно зная, что текущие ремонты, то есть те на которые ты сегодня живешь, занимают у тебя 25% рабочего времени.

Кроме того, для ремонта не нужно слизывать все, ибо ремонтник не собирается заниматься производством и продажей. Для ремонта почти всегда хватает зацепки за один конец ниточки, и через этот конец найти где собака порылась.

Это столько НЕ стоит. Стоит ЗНАЧИТЕЛЬНО (на порядок, как минимум) дороже. И на такое ходят не в одиночку. И НЕ всё - невозможно!

Или всё - или ничего. И это намного дольше - не на месяц! На ТАКОМ "ремонте" - не заработаешь.

ПЛИС можно менять если есть уверенность, что она и является причиной дефекта. Но практика показывает, что это далеко не всегда так. Гораздо чаще причиной дефекта является то что к ней подключено..Да. Верно. Но имеющий уши да услышит первое (см. выше)

С извинениями Adv.

Как убрать из анализа путь?

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Попробуйте что-то вроде этого.....

set_false_path -fall_from [get_clocks $gtxclk] -rise_to [get_clocks tx_output_clock] -setup

Пределайте под своё, разумеется(свои имена частот вставьте). Только - вставьте имена правильно. Там возможно ещё море скобок (как в любом скрипте....). Правильное написание этих частот со скобками - посмотрите сами прямо в ТаймКвесте.