swt

Участник-

Постов

11 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйПосетители профиля

716 просмотров профиля

-

1. Если скорость передачи данных 350 МГц, то я должен в параметрах IDELAYE2 указать 400МГц? 2. При этом на управление могу подать меньше?

-

Прошу помочь разобраться правильно ли я понял: 1. что в блоке IDELAYCTRL тактовая частота должна быть от 190 to 210 от 290 to 310 от 390 to 410 такая же как указана в параметрах IDELAYE2 ??? inst_IDELAYCTRL : component unisim.VCOMPONENTS.IDELAYCTRL port map( RDY => delay_locked_o, REFCLK => delay_clk_i, RST => delay_rst_i ); 2. Какую частоту можно подавать на вывод С в управлении задержкой блока IDELAYE2 inst_IDELAYE2 : component unisim.VCOMPONENTS.IDELAYE2 generic map( CINVCTRL_SEL => "FALSE", DELAY_SRC => "IDATAIN", HIGH_PERFORMANCE_MODE => "FALSE", IDELAY_TYPE => "VARIABLE", IDELAY_VALUE => IODELAY_VALUE, PIPE_SEL => "FALSE", REFCLK_FREQUENCY => 200.0, SIGNAL_PATTERN => "DATA" ) port map( CNTVALUEOUT => CNT_data_idelay_out, DATAOUT => data_idelay_s, C => up_clk_i, CE => СE_data_idelay, CINVCTRL => '0', CNTVALUEIN => '0', DATAIN => '0', IDATAIN => data_ibufds_s, INC => '1', LD => '0', LDPIPEEN => '0', REGRST => '0' ); 3. Параметр IDELAYE2 REFCLK_FREQUENCY выбирается из диапазонов от 190 to 210 от 290 to 310 от 390 to 410 ,но не обязательно должен соответствовать частоте на которой передаются данные и заводятся в блок ISERDESE2. Просто шаг подстройки будет соответствовать выбраному параметру? 4. Не смог понять когда необходимо произвести сброс IDELAYCTRL поясните пожалуйста P.S. скорость передачи данных в проекте 350 МГц

-

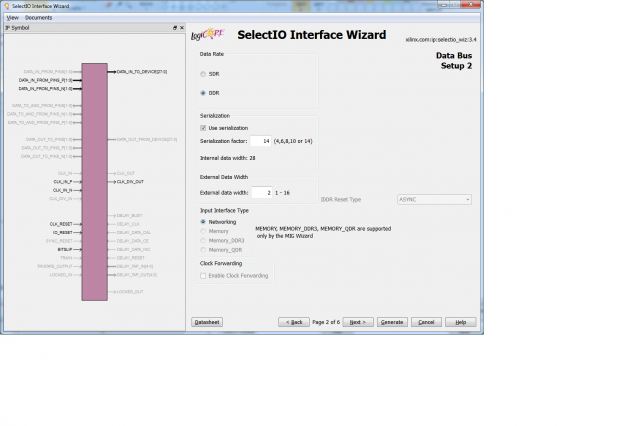

При освоении нового элемента пробую разные варианты для закрепления прочитанного материала в xapp524 и стараюсь начинать с простого: вот попробовал ядро использовать SelectIO Interface Wizard выбрал опцию Clocking strategy = internal для того что бы использовать оба сигнала от АЦП фрейм клок и клок данных и не понял где же задается частота в этом Wizard, она нужна чтоб посчитать шаг сдвига IDELAYE2. Покрутился покрутился и решил пойти дальше и столкнулся с проблемой синтез идет , Но при имплементация вылетело критическое предупреждение [Timing 38-472] The REFCLK pin of IDELAYCTRL lvds_1L_14bit/inst/delayctrl is not reached by any clock but IDELAYE2 lvds_1L_14bit/inst/pins[0].idelaye2_bus has REFCLK_FREQUENCY of 200.000 Mhz (period 5.000 ns). The IDELAYCTRL REFCLK pin frequency must match the IDELAYE2 REFCLK_FREQUENCY property value. нашел по тексту в файлике inst : selectio_wiz_0_selectio_wiz (selectio_wiz_0_selectio_wiz.v) цитата ".... .REFCLK_FREQUENCY (200.0) ......" , а исправить не выходит - файлик только на чтение!!! Вот почему Wizard не спросил меня про частоту на которой будет работать мой проект?

-

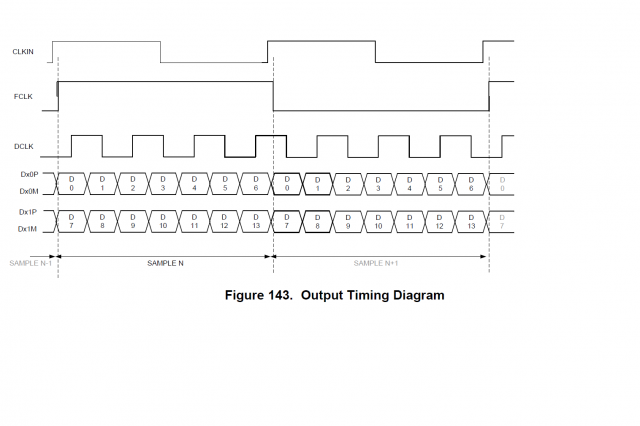

наверно обойтись можно, но частота оцифровки 100 МГц, разрядность 14 бит, режим DDR и 2 линии LVDS получается clock сопровождения данных 350 МГц придется контролировать размещение в ПЛИС преобразователя (последовательного=>параллельный)

-

Отличный вариант спасибо! почему мне не пришло это в голову и более того в документе XAPP524 который привел blackfin ранее как я понял рекомендуется работать с диффиринциальной шиной как с недиффиринциальными сигналами в котором по in_p идут четные биты а in_n нечетные. То есть предложили использовать буфер пина недифферинциальный как я понял. На один ISERDESE2 подать прямой clock, а на второй инверсный (или я их не понял от слова совсем). как я понял рекомендуется работать с диффиринциальной шиной как с недиффиринциальными сигналами в котором по in_p идут четные биты а in_n нечетные. То есть предложили использовать буфер пина недифферинциальный как я понял. На один ISERDESE2 подать прямой clock, а на второй инверсный (или я их не понял от слова совсем). Мне кажется такое использование дифферинциальной шины похоже на костыли, но если другого ничего не придумать......

-

согласен, но это когда одна дифферинциальная пара то можно сделать 14 бит, а тут их две..... и если ставишь две пары при DDR то 7 бит поставить нельзя, а при 14 на выходе получается 28 бит и это явная лажа...

-

ISERDESE2 +ADC3444 сложность настройки

swt опубликовал тема в Работаем с ПЛИС, области применения, выбор

Задача Подключить ADC3444 к ПЛИС kintex7 Исходные две пары LVDS по которым передаются 14 битные отсчеты в режиме DDR Проблема ISERDESE2 не конфигурируется на 7 бит в режиме DDR вопрос кто как это обходит? -

В настоящий момент первый раз делаю проект с АЦП с дифферинциальными парами ADC3444, грабли собираю, было бы здорово подглядывать в рабочий проект. Буду признателен, если скинете.

-

Wi-fi модуль SPB800 hd-wireless

swt ответил mpr тема в Wireless/Optic

Могли бы подсказать? приобрел и только начал разбиратся =) можно ли настроить SPB800 c прошивкой spb800-serial_to_wifi_rxxx.hlf что бы слушать всю служебную информацию в момент подключения к сети по порту UDP ? -

можно ли настроить SPB800 c прошивкой spb800-serial_to_wifi_rxxx.hlf что бы слушать всю служебную информацию в момент подключения к сети по порту UDP

-

в документации на модуль сказано что он может работать как преобразователь wifi в com-порт, собственно говоря сом-порт единственный интерфейс для настройки и передачи данных через данный модуль. задача следующая с помощью модуля создать сеть к которой подключится единственное устройство wifi и через порт udp1984 принимать данные без паролей без шифрования. устройство которое должно подключится и передать данные "рабочее и точно передает данные как только устанавливается связь". Я вижу сеть созданную модулем, подключаюсь, но данные через сом-порт в программе терменал не отображаются. готов показать скрин шот настроек модуля может ктото возьмется подсказать ? PATH FLAGS SZ TYPE VALUE(S) ---------------------------- ---------------- -- ----- -------------- /wl/ssid NV 1 SSID WiRC /wl/key NV 1 STR /wl/key_type NV 1 U8 none(0) /wl/mode NV 1 U8 ap(1) /wl/channel NV 1 U8 1 /wl/hwaddr RO PROC 1 STR N/A /wl/rssi RO PROC 1 S32 N/A /wl/status RO PROC 1 STR Disconnected /net/dhcp NV 1 BOOL 0 /net/ip NV 1 IP 192.168.1.1 /net/mask NV 1 IP 255.255.255.0 /net/gw NV 1 IP 192.168.1.1 /net/dns NV 1 IP 208.67.222.222 /net/status RO PROC 1 STR N/A /proto/active NV 1 U8 none(0) /proto/none/mode NV 1 U8 tcp-client(0) /proto/none/host NV 1 STR /proto/none/port NV 1 U16 1984 /uart/baudrate NV 1 U32 57600(57600) /uart/rtscts NV 1 BOOL 0 /uart/databits NV 1 U8 8(8) /uart/parity NV 1 U8 none(0) /uart/stopbits NV 1 U8 1(1) /uart/mode NV 1 U8 rs232(0) /uart/duplex NV 1 U8 half(0) /shell/nodots NV 1 BOOL 0 /auth/username NV 1 STR /auth/password NV 1 STR /dhcpd/enable NV 1 BOOL 1 /httpd/port NV 1 U16 80 /httpd/auth NV 1 U8 digest(2) /hw/board RO PROC 1 STR spb800 /hw/rev RO PROC 1 STR 2841