umarsohod

-

Постов

47 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные umarsohod

-

-

Нужно было просверлить отверстие в стене, а где-то в этом районе проходила проводка к розетке.

Для поиска скрытой проводки использовал такой способ. Поскольку два провода между собой

расположены на некотором расстоянии, магнитное поле не идеально скомпенсировано, и его можно обнаружить.

В качестве датчика использовал небольшой 50-герцовый трансформатор от блока питания.

Спилил часть сердечника со стороны вторичной обмотки (обычно на таких траннсах обмотки раздельные).

А первичную обмотку подключил к усилителю. И , если подносить транс к проводу с током,

то, соответственно, в колонках (а лучше в наушниках) начинает гудеть 50герц.

Чтобы убедиться , что это именно "нужные 50герц" в розетку подключил нагрузку(настольную лампу) и

включал/выключал. Правда расстояние обнаружения было небольшое, несколько сантиметров. -

Можно два трансформатора.

журнал Радио №11 1997г стр 49 -

Just now, Zinka said:

Не обидется, только спасибо скажет.

Эксперименты с латором могут быть опасны, 6к не шутки.

Если не боитесь, поставте на латоре сначала 50, потом потихоньку поднимайте.

-

Там, конечно, не все сердечник, я думаю килограмма 4, плюс первый транс. Итого 10вт активных потерь,

от которых никуда не дется. Усилок нужно помощнее.

Почему нельзя поднять частоту? хотя-бы для эксперимента.

-

Опубликовано · Изменено пользователем umarsohod · Пожаловаться

Сколько второй транс весит? Потери в железе до 2х вт/кг

Попробуйте повысить частоту

-

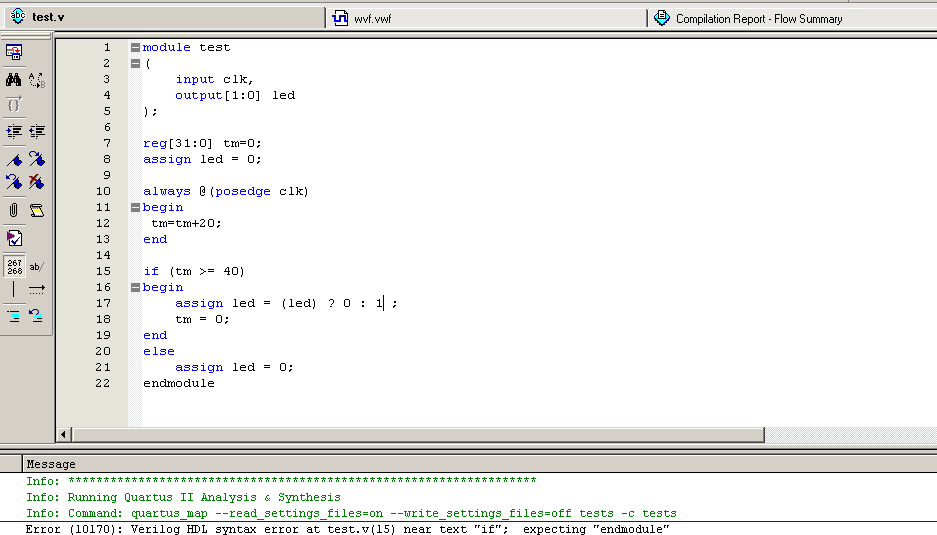

Для того, чтобы видеть, стартовал проект или нет.

-

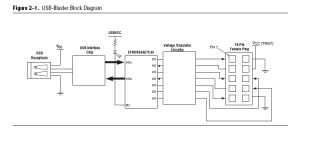

Исходники - https://marsohod.org/413-mbftdi-sources

Там есть програмка для разбери, можно попробовать адаптировать.

-

На CONF_DONE и NSTATUS и nCONFIG подтяжки обязательно.

Удивительно , что у вас вообще стартует.

Эти пины еще куда-то подключены?

-

Flip-Fp0p - браво.

Господа инженеры - учите Квартус, там есть все.

-

Надо же было столько копьев сломать из за ерунды.

DDIO в МАХ10 есть.

Пример использования - https://marsohod.org/projects/proekty-dlya-platy-marsokhod3/307-max10-hdmi

-

Опубликовано · Изменено пользователем umarsohod · Пожаловаться

Поведение "altera_onchip_flash_block" очень похоже на поведение "ALT_UFM_NONE" для MaxII, почитайте на него документацию.

Но я разбирался только с тем , что мне было нужно. Младший бит "ardin" действительно похож на вход сдвигового регистра адреса,

но какой длинны этот регистр неизвестно . Я задвигаю 512 нулей "впрок".И данные действительно начинаются не сначала.

К модулю есть параметр "ADDR_RANGE1_OFFSET(512)", но его изменить у меня не получилось.

-

Я думаю, вы что-то неправильно пробуете.

Почитайте внимательно ворнинги компилятора.

-

Вам для какой цели это нужно?

Если просто все подряд прочитать, можно так - https://github.com/marsohod4you/M02mini/blob/master/forth_j1/ufmr.v

-

У нас пару раз была похожая проблема, но в чем причина не знаю.

https://marsohod.org/forum/7-mbftdi/4783-mbftdi-i-signaltap-oshibka

-

Если "sof" загружается нормально, то оборудование работает.

Другой проект не пробовали?

-

Когдато давно, соединял две CPLD сдедующим образом : передача одного бита происходила за 3 цикла,

сначала "1" затем, собственно один бит данных, затем "0". На приемной стороне этот поток подавался на вход "D"

триггера, а на клок этот-же поток, только задержанный на 1.5 цикла. Таким образом при тактовой в 200Мгц, скорость

обмена была 66 мегабит.

10LP в "DDR" -режиме может работать на 800 Мгц, и таким способом можно получить скорость 260 мбит.

Если на приемной стороне есть свободный PLL, то можно передавать 2 бита за 5 циклов и получить скорость 320 мбит.

-

-

Есть ли официальные какие-то документы на эту тему?

У них одинаковый DEVCE ID.

А на счет таймингов, с3 из этой компании самый быстрый.

-

Опубликовано · Изменено пользователем umarsohod · Пожаловаться

Какие модели так совместимы, хотя бы один пример.На одну и ту-же плату ставим EP3C10E144C8N и EP4CE6E22C8N, все работает.(если помещается)

С 10LP та-же история, я уже пробовал под него компилировать а зашивать в 3, то-же работает.

-

Можно компилировать под 4 а заливать в 3, битстрим подходит.

Но у 4 IO пинов чють меньше, некоторые пины использовать не получится.

-

Нужно придумать свою валюту, что-бы майнилась только на FPGA.

Был-бы хороший толчек отрасли, ато ПЛИСы в развитии как-то подзастряли.

-

Что за чип? Если в QFP, попробовать "exposed pad" пропаять.

-

Опубликовано · Изменено пользователем umarsohod · Пожаловаться

-

Опубликовано · Изменено пользователем umarsohod · Пожаловаться

Попробуйте запустить "JTAG Chain Debugger", но, что-то у меня плохое предчувствие.

Питание для преобразователей на разъеме есть?

Как найти замыкание проводки в стене?

в В помощь начинающему

Опубликовано · Пожаловаться

Должно гудеть только там, где течет ток