-

Постов

46 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Orochi

-

Звание

Участник

- День рождения 14.09.1986

Старые поля

-

skype

Array

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Вот как подключен этот этот компонент у меня. avalon_slave_export type: conduit (как раз внешняя логика). P.S.: Если не ответил на вопрос предыдущего поста переформулируйте и поподробней)

-

Создать СИшный проект с BSP не проблема, а вот с С++ проблема.

-

Не стал создавать тему ради пустякового вопроса, но нигде не могу найти как создать проект С++ в NIOS II EDS, да и все примеры генерятся на Си. Подскажите где я что пропустил в этой жизни =) ps: если быть более точным то сам проек на С++ создать не проблема File->New->Project->C/C++ ... но как тогда к нему подключить BSP?

-

Я учился работать с регистрами анализируя код этого компонента (файл прилагается). Всё с коментариями, даже с таблицами (карты регистров). Посмотрите, там всё понятно изложено. SD_Card_Controller_SPI.7z

-

Есть: "создай новый файл и пиши с нуля" =) (по крайней мере у меня получается)

-

Спасибо большое за ответы, буду дальше разбираться с DMA и Avalon-ST.

-

Avalon-ST

Orochi опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

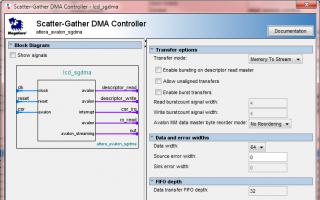

Задался целью разобраться, как всё-таки работает Avalon-ST и посмотрел SignalTap следующую (картинка 1) конструкцию. Посмотрел сигналы между SG-DMA и Timing Adapter 1 и получил "картинка 2". Такое подключение было сделано по какой то из альтеровских мануалов и работает. Вопрос в другом: как видно из списка сигналов имеем: out_valid, out_ready, out_data, out_empty, out_startofpack, out_endofpack. Из полученных диаграмм видим что out_valid всегда 1, и по сути данные передаются по готовности (out_ready). Почему же не используются сигналы out_startofpack и out_endofpack? На всякий случай приведу настройки SG-DMA и Timing Adapter 1. -

написал в личку

-

Бегло просмотрел tt_nios2_multiprocessor_tutorial.pdf (Creating Multiprocessor Nios II Systems) и не нашёл там упоминания того что надо заходить в Windows->Preferens ... Уточните по какому мануалу что вы делали, на какой станице и какой строчке у вас что то не получается. На картинке содержание Preference моего Eclipse

-

Удалил сигнал ready. То что получилось видно на картинке. Вопрос такой: например, в момент времени "1" мы имеем перепад valid 0->1. Как видно из диаграммы пока valid не станет 0 передаются 2 "пачки" данных D1,D2. Так вот если я установлю valid=1 перед 1 посылкой и сброшу только после последней, не получится ли тот эффект которого я добиваюсь? (а имеенно передача 1 отсчёта данных за 1 цикл clk в течении всего времени получения данных от интерфейса conduit).

-

По сути есть та же задача: написать модуль, получающий данные с частотой от 0 до 100MHz (частота константа и определяется в зависимости от состояния регистров в модуле), пишет их в FIFO (меняем клоковый домен/буфер) и далее в DMA/SGDMA и в память (SDRAM). На картинке примерно изобразил то как я себе представляю структуру модуля: На входе conduit так как данные получаем из вне. На выходе Avalon-ST Source, т.к. в спеификации по интерфейсам было написано что этот интерфейс для потоковой передачи данных. Управления внутренними регистрами модуля осущетвляется через интерфейт Avalon-MM. Остались вопросы по Avalon-ST как видно на картинке (внизу) есть пропуски циклов, когда данные не пишутся. Подскажите как сконфигурировать Avalon-ST что бы можно было писать в FIFO 1 пачку (32 бита) за 1 такт в течении всего промежутка времени получения данных с интерфейса conduit. И тема про DMA тоже интересна, прошу выкладывать результаты "трудов" если не жалко на форум, будем учиться вместе)

-

Изнутри модуля тактируемого частотой CLOCK никак не узнать частоту этого CLOCK, так как мерять надо относительно чего то, и не получится измерять частоту относительно этой же частоты. Вам нужена или заведомо большая опять же извесная частота, или внешние модули которые тактируются опять же извесной частотой. В любом случае изврат из области микросхемотехники. Как вариант добавте в свой модуль субмодуль на который приходит известная частота, он её изменяет на необходимую вам (меньшую) частоту, и регулирует её вам по Вашему же закону и Вашим же условиям, которые вы пропишите.

-

по поводу объёма памяти: в документации на плату заявлено 128МБ и в даташите 4 банка( по крайней мере у меня). На счёт записи в память напрямую, сам никогда не прбовал, небыло пока нужды, но может быть выложите исходники, или хотя бы кусок кода которым Вы пишите/читаете из памяти, и возможно так Вам помогут быстрее.

-

Вы специально поставили Bank = 2? У меня на DE2-115 этот параметр равен 4 и как следствие доступной памяти побольше 128) По поводу "заставить работать" terasic предлагает демо примеры для изучения, и на них всё прекрасно работает и крутится, не пробовали изучать? По поводу моделирования, може быть поставить галочку в настройках SDRAM "генерировать функциональную модель для тестбенча"?

-

поковыряв чужие модули (компоненты qsys к отладочным платалм различных производителей) я замечал что частота которой тактируется модуль, там где это критично притята константой, тоесть известна. И как следствие, если подать не ту частоту, компонент не работает. Как вариант, может быть, написать ещё 1 компонент на основе счётчика и регистра состояния (хранящий частоту на выходе) вы будете знать частоту и управлять ей по необходимости. (я в ПЛИС сообществе начинающий, если написал бред прошу не бить, а сказать как принципиально можно сделать это полегче) B)