ArtoM23

Участник-

Постов

28 -

Зарегистрирован

-

Посещение

Весь контент ArtoM23

-

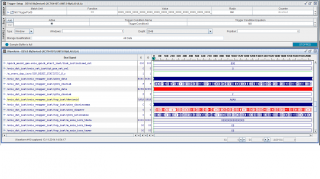

Здравствуйте, коллеги. Ваши комменты почитал, интересен вопрос. У меня в системе АЦП ad9680 4 штуки и плис virtex 7 410t. Подключено 4 линии 10 Гбит. Стадии инициализации проходят, получаю данные из АЦП. Частота тактовая 1000 Мгц, Sysref 50 Мгц. При выборке 512 кб вижу "рваный" в одном месте синус, то есть сигнал теряет 4 отсчета в посылке, при этом счетчики ошибок встроенные в корку плис JESD не обновляются. То есть сигнал получен таким с АЦП, ошибок декодирования не было на линии. Прошу дать совет, что делать? rolleyes.gif

-

Подключаете программатор, открываете импакт. Конфигурацию можно вычитать из flash. Слева кнопка ReadBack

-

Исходя из опыта на плате ставится внешний датчик температуры, который опрашивается по i2c например. ИМХО System monitor лучше использовать только для ПЛИС. :rolleyes: Кстати а интересно, внешнее устройство находится у Вас на плате или это отдельное изделие?

-

Спс за ответ. Нашел готовое решение ise 14.7 Selectio wizard. Ребята из ксалинкса сделали все просто отлично, а главное понятно. Думаю сэкономит мое время, а главное поможет.

-

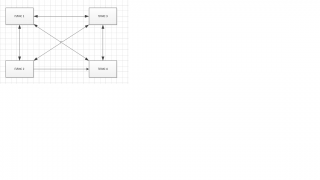

Связь 4 ПЛИС kintex 7 физ линиями на ПП

ArtoM23 опубликовал тема в Форумы по интерфейсам

Здравствуйте! Есть плата на которой стоят 4 ПЛИС kintex7 с физическими связями через HP банки 32,33,34 как показано на рисунке ниже. Всего 48 линий. Необходимо передавать минимум 20 битные данные с 800 МГц на линию. То есть 1 связь должна пропускать 24*800 = 19200 Мбит/сек. Мой вариант организовать это с помощью ioserdes. Это логично, что вы думаете? -

CDCE62005 настройка по SPI

ArtoM23 ответил aosp тема в Схемотехника

Спс, разобрался. Надеюсь кто-то сэкономит часы, а в моем случае деньки ) Просто нужно соблюсти последовательность и ничего не забыть. 1) Прогружаем SPI регистры 1-8. 2) Проверяем LOCK. Если LOCK установлен, но на выходе частота не та, что ожидается переходим п.3. или даем команду на перекалибровку в соостветствии с cdce62005.pdf Если LOCK установлен, но на выходе постоянка, то проверьте согласование по входу опоры и обратно в п.1. 3) Даем инструкцию на запись EEPROM. 4) Вкл/выкл микросхему пин -PWDW. После этого проверяем частоту на выходе. По поводу программирования на 10 раз, это я как раз заходил в режим перекалибровки не изменяя при этом других регистров. -

CDCE62005 настройка по SPI

ArtoM23 ответил aosp тема в Схемотехника

Здравствуйте, подскажите мне пжл как вы решили данную проблему. Использую cdce62005.pdf и программу evalcdce62005.exe. Прогружаю 7 регистров без 8го. После ряда циклических прогрузок PLL входит в нужный режим. Как вы решили проблему, есть ли жесткий алгоритм прогрузки? :cranky: HELP, не удается запустить, знающие помогите!!! -

Что касается питания ПЛИС, у нас есть расхождение с рекомендацией. Последовательность активности питаний: VMGTAVTT и VMGTAVCC одновременно, VCCINT, VCCAUX, VCC0. - плисина и сигнальник подключены напрямую или через свич? ПЛИС и DSP подключены напрямую (точка-точка). - клоки рапиды тактируются у них от одного генератора, или от разных? Клоки рапиды и DSP и ПЛИС подключены к разным генераторам, точнее на dsp идет клок рапиды от PLL2 cdce62005 312.5 МГц. На ПЛИС клок рапиды можно завести двумя путями: - напрямую от генератора 125 Мгц - от pll0 cdce62005, пропустив через неё сигнал генератора 125 МГц. Пробовал эти два варианта. - в стандартной корке рапиды от ксайлинкса есть возможность принудительно сбросить линк и порт, вы пробовали так делать? Да, так делать пробовал, результат аналогичен. - посмотрите что в регистрах ошибки SRIO сигнальника прописано когда все плохо. В одном из регистров утановлен бит ошибки на прием данных. error decode 8b/10b. - есть ли уверенность, что программа в сигнальнике стартовала? Механизм конфигурирования DSP после подачи питания еще не отлажен. То есть я в chipscope смотрю, что DSP_RESET_STATISTIC в 1, а затем шью dsp вручную. - соответствует ли стартовая последовательность на 6678 даташиту? Здесь я не совсем понял, что вы имеете ввиду. Стартовая последовательность SRIO? Errata скачал. изучаю. Спасибо за мысли. у нас на плате revision1.) То есть у Вас также не было инициализации между ПЛИС и DSP по рапиде?

-

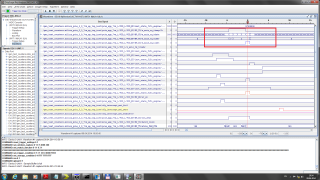

Здравствуйте! Используем самостоятельно изготовленную плату с установленной ПЛИС xc7k410t и DSP tms320c6678. На данном этапе идет отладка взаимодействия ПЛИС и DSP с использованием интерфейса SRIO gen 2 v1.7. Включением питания на плате управляет мк stm8. Сначала контроллер открывает питание на ПЛИС, затем ПЛИС конфигурируется и "дает" мк разрешение на включение питаний dsp. dsp включается в соответствии с документом TMDXEVM6678L_EVM_A102_1.pdf стр 4. Далее мк сообщает ПЛИС о том, что DSP включен и плис прогружает PLL1 и PLL2 необходимые для работы DSP (в своем изделии повторена схема на стр. 7). После чего, ПЛИС ожидает захвата pll1 и pll2, а затем сигналы сбросов dsp подтягиваются к единице в соответствии со схемой на стр.4. Как только DSP сброшен выставляется сигнал DSP_RESET_STATISTIC. Ну и наконец) Проблема в том, что инициализация порта SRIO в режиме 1gb/s 1x проходит от включения к включению платы. То есть, я могу запустить изделие, затем после прогрузки ПЛИС, вкл. DSP, после захвата PLL сконфигурировать DSP и в chipscope увидеть "работающий порт" или увидеть "нечто", что представлена на рисунке ниже. контуры питаний на плате были тщательно проверены, PLL-ки гарантированно всегда в захвате. Как думаете, в каком направлении копать? :cranky: Применительно к DSP хочу отметить, что если инициализация порта прошла успешно после включения, то разные режимы работы 4x 3.125gb/s, 4x 5gb/s, 1x 2gb/s, 1x 5gb/s работают адекватно, порты инициализируются.

-

Добрый день! Интересует как на Вашем предприятии с секретностью и присваивается ли сотрудникам форма допуска?

-

DDR3 MIG virtex6

ArtoM23 ответил bogaev_roman тема в Среды разработки - обсуждаем САПРы

Смотрите первоисточник mig 3.92. Пользовался им и вполне толково написано) Раздел user interface. К тому же используйте ModelSim и вы получите модель которая идет с коркой. Инструкция по запуску модели в том же ug 406. -

Проблема решена. :bb-offtopic: при передаче адреса в эвм необходимо отбрасывать два младших бита.

-

Форумчане, помогите :laughing:. Проблема обрела новую сторону. Изучил pg023. Открыл для себя "чудесный мир" интерфейсов этого ядра. Анализируя статус ошибок в chipscope из "Devise status register" выявил особенность. На шине регистрируется ошибка "fatal error". Согласно pg023 это может быть вызвано несоответствием длины передаваемых данных (полезной нагрузки) на шине pcie и в дескрипторе (заголовке tlp пакета). А также неправильным видом запроса. Подскажите в каком направлении копать? И интересно почему после выявлении ошибки система перестает регистрировать прерывания, а ядро pcie их якобы выдает по команде (msi_sent ='1'). Используемый драйвер, программа тестирования успешно использовался с отладочной платой virtex 6. Но там и ядро было без AXI).

-

Касательно стыковки seriallite/aurora. Модули seriallite в проекте не менялись. Произвел редактирование модулей aurora. Для virtex6 использовалась aurora 6.2. Параметры: - 2гб/сек с опорной частотой 125 МГц. - 1 линия. Параметры Seriallite: - 2гб/сек с опорной частотой 100 МГц. - 1 линия. Фактически были подогнаны параметры физических посылок aurora под интерфейс Seriallite. То есть в соответствии со спецификацией seriallite поправлены модули авроры: - standard_cc_module.vhd, - gtx.vhd, - sym_gen.vhd. Сравните файлы архиве mSimple_optica_altera_xilinx.rar.

-

Была похожая задача. Организовывали связь по оптике 25 метров. 6 плат Altera stratix 2 gx с SFP+ 2 gb с одной стороны и Xilinx Virtex 6 6 SFP+ с другой стороны. Связь осуществлялась протоколами serial lite/aurora. В стыковке serial lite и авроры могу помочь. Все сводится к редактированию модулей клоковой компенсации.

-

Вот код формирования посылокк на ядро pcie s_axis_rq*. PIO_TX_DMA_START_DESC : begin // Запись в память ЭВМ (host cpu) дескриптора с начальным адрессом памяти для DMA s_axis_rq_tvalid <= #TCQ 1'b1; s_axis_rq_tlast <= #TCQ 1'b0; s_axis_rq_tkeep <= #TCQ 8'hFF; // 4DW Descriptor and DW Payload For Memory Transaction s_axis_rq_tdata <= #TCQ {DATA_TLP_IN[223:96], // 4DW Payload 1'b0, // Force ECRC 3'b000, // Attributes 3'b000, // Traffic Class 1'b0, // RID Enable to use the Client supplied Bus/Device/Func No 16'b0, // Completer -ID, set only for Completers or ID based routing (AXISTEN_IF_ENABLE_CLIENT_TAG ? 8'h00 : req_tag), // Select Client Tag or core's internal tag 8'h00, // Req Bus No- used only when RID enable = 1 8'h00, // Req Dev/Func no - used only when RID enable = 1 1'b0, // Poisoned Req 4'b0011, // Req Type for MRd Req 11'h20, // DWORD Count 30'h0000_0000, DATA_TLP_IN[255:224],// Memory Write cpu Address [62 bits] 2'b10}; //AT -> 00- Untranslated Address 10-> Translated Address s_axis_rq_tuser <= #TCQ {(AXISTEN_IF_RQ_PARITY_CHECK ? s_axis_rq_tparity : 32'b0), // Parity 4'b1010, // Seq Number 8'h00, // TPH Steering Tag 1'b0, // TPH indirect Tag Enable 2'b0, // TPH Type 1'b0, // TPH Present 1'b0, // Discontinue 3'b000, // Byte Lane number in case of Address Aligned mode 4'hF, // Last BE of the Read Data 4'hF}; // First BE of the Read Data if(s_axis_rq_tready) begin state <= #TCQ PIO_TX_DMA_START_DW; trn_sent <= #TCQ 1'b1; cnt_tx_to_pci <= cnt_tx_to_pci +4; end else state <= #TCQ PIO_TX_DMA_START_DESC; end // PIO_TX_DMA_START_DESC PIO_TX_DMA_START_DW : begin // Запись в память ЭВМ (host cpu) полезной информации из FIFO s_axis_rq_tvalid <= #TCQ 1'b1; s_axis_rq_tlast <= #TCQ 1'b0; s_axis_rq_tkeep <= #TCQ 8'hFF; // 4DW Descriptor and DW Payload For Memory Transaction s_axis_rq_tdata <= #TCQ DATA_TLP_IN; // 4DW Payload s_axis_rq_tuser <= #TCQ {(AXISTEN_IF_RQ_PARITY_CHECK ? s_axis_rq_tparity : 32'b0), // Parity 4'b1010, // Seq Number 8'h00, // TPH Steering Tag 1'b0, // TPH indirect Tag Enable 2'b0, // TPH Type 1'b0, // TPH Present 1'b0, // Discontinue 3'b000, // Byte Lane number in case of Address Aligned mode 4'hF, // Last BE of the Read Data 4'hF}; // First BE of the Read Data if(s_axis_rq_tready) if(cnt_tx_to_pci < 20) begin cnt_tx_to_pci <= cnt_tx_to_pci +8; // на шине 8DW state <= #TCQ PIO_TX_DMA_START_DW; trn_sent <= #TCQ 1'b1; end else begin state <= #TCQ PIO_TX_DMA_START_DW_END; trn_sent <= #TCQ 1'b1; end else state <= #TCQ PIO_TX_DMA_START_DW; end // PIO_TX_DMA_START_DW PIO_TX_DMA_START_DW_END: begin // завершаем передачу данных в ЭВМ для записи в память s_axis_rq_tvalid <= #TCQ 1'b1; s_axis_rq_tlast <= #TCQ 1'b1; s_axis_rq_tkeep <= #TCQ 8'hF0; // 4DW Descriptor and DW Payload For Memory Transaction s_axis_rq_tdata <= #TCQ DATA_TLP_IN; // 4DW Payload s_axis_rq_tuser <= #TCQ {(AXISTEN_IF_RQ_PARITY_CHECK ? s_axis_rq_tparity : 32'b0), // Parity 4'b0000, // Seq Number 8'h00, // TPH Steering Tag 1'b0, // TPH indirect Tag Enable 2'b0, // TPH Type 1'b0, // TPH Present 1'b0, // Discontinue 3'b000, // Byte Lane number in case of Address Aligned mode 4'hF, // Last BE of the Read Data 4'hF}; // First BE of the Read Data if(s_axis_rq_tready) begin state <= #TCQ PIO_TX_RST_STATE; trn_sent <= #TCQ 1'b1; end else state <= #TCQ PIO_TX_DMA_START_DW_END; end // PIO_TX_DMA_START_DW

-

Virtex 7 pcie

ArtoM23 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Здравствуйте! Используется отладочная плата с ПЛИС xc7vx415t-2ffg1927. Сгенерил корку pcie virtex7 1.6. Ise 14.6. Параметры корки: - pcie gen 2. 5Gb/s - axi data 256 bit - clk 125 mhz - data word aligned Доступ/чтение BAR осуществляется без проблем. В ПЛИС организован DMA. Перекачка идет в тестовом режиме 1 пакета 128 байт. Затем после перекачки ПЛИС генрит прерывание MSI. Логика работы следующая: 1) ПК пишет в BAR начальный адрес оперативной памяти куда попадут данные из ПЛИС, длину запрашиваемых данных в TLP пакетах. Дает команду "СТАРТ". 2) ПЛИС передает данные. На ядро идут команды s_axis_rq*. 3) После передачи ядру запрошенных данных ПЛИС дает команду прерывания на ядро. Счетчик отправляется непосредственно из ПЛИС в ПК: Получаю на выходе прерывание, а данные в памяти ПК не перезаписываются, то есть вместо ожидаемой "пилы" в памяти лежат нули записываемые туда при инициализации драйвером. В модели корки показан режим работы IO, но используется интерфейс axis_cq/cc. Проблема может быть в заголовке TLP s_axis_rq? Есть ли примеры работы с интерфейсом s_axis_rq*? -

Итак, в результате удалось запустить тест traffic_gen во всех режимах на частоте 400 МГц. Проблема решилась путем предустановки линий ADDR, RAS, CAS с последующим защелкиванием CS. Также на некоторых платах напояли дополнительные конденсаторы (спасибо SM). Вопрос собственно в следующем. Есть ли какие - то примеры организации User interface для mig 3.92. И как организовать параллельное запись/чтение в память, так называемый режим кольцевого буфера?

-

На VTT рядом стоят 3x10 мкф - керамика. Допаяли 10 мкф тантал, 100 пф керамика, 3х0,1 мкф. Ошибки не исчезли. На Vref стоит со стороны ПЛИС по 0,1мкф на каждый банк. Со стороны памяти по 0,1 на каждую мс. Возле TPS на Vref 0,1мкф. Пробовали добавлять 220 мкФ тантал. Ошибки остались. На virtex 6 согласно ds152 должно быть 2.5В на VCCAUX. При тестировании памяти в режиме когда адрес совпадает с записанными данными была замечена интересная особенность. "ошибочные" данные совпадают с данными из другого адреса. Не может сбоить шина команд/адресса? С чем это может быть связано?

-

Похоже у нас тоже самое. Одна цепь 2,5 В и VCCAUX и VСCIO. А в чем природа ошибки? с SSO проблем не оказалось. Проверял в PlanAhead 14.7.

-

"по SSO - это должен trace уметь, делать отчет по SSO." под trace понимаем среду разводки? В нашем случае это PCAD 2004)

-

Питание памяти VCC 1,5 В формирует мс lt1764a. vref и vtt формируются tps51200 из VCC. Привязка такая. Пробуем добавлять конденсаторы на VTT :rolleyes: Спасибо за совет, только где можно о методике проверки SSO почитать?

-

Насчет vccaux, vtt, vref. Измерялась пульсация vtt, vref. Отклонения в пределах значений указанных в даташите на мс памяти. VCCAUX, VCC_O заведено от DC/DC преобразователя ltm4601 20А. Есть ли какие-то конкретные требования к VCC_AUX?

-

Здравствуйте, форумчане! Как выяснилось, выравнивание дорожек сигналов памяти на плате выполнено до 0.5 мм, без учета задержек на чипе. ("partgen -v xc6vlx240tff1159"). Собственно как это понять? Ознакомился с файлом xc6vlx240tff1159.pkg напрашивается пока только вывод, что "правильно" взять и укоротить дорожки конкретных линий на величину trace_length. Можно ли используя trace_length по ug 406 посчитать отклонения(skew) dq\dqs, adr\cmd \ CK? Еще раз по методике xilinx_mig_hardware_debug стр. 29-30 протестировал память на частоте 333 МГц С помощью traffic_gen выявлена особенность при использовании режима запись\чтение по фиксированному адресу калибровка проходит успешно и ошибок данных нет во всех режимах генерации данных. Начинаю увеличивать диапазон используемых адресов от 0 до x"ffffff" получаю ошибки данных. Адресное пространство rank_bank_row_col. col 0_9 бит row 10_23 бит bank 24_26 бит rank 27 бит Может ли это быть связано с выравниванием?

-

Здравствуйте, форумчане. Убрал по замечанию VladimirB резисторные матрицы 15 Ом с линий dq, dqs. Заменил их перемычками. К сожалению результат тот же. Данные на частоте 400 МГц бьются. Выравнивание линий выполнено с учетом разброса шариков BGA. Линии выравнены до 0.5мм. тест сигналов осциллографом пока ничем не помог. Всем спасибо за советы. Продолжаю поиск ошибок.