Tanichev

Участник-

Постов

31 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Tanichev

-

Звание

Участник

Посетители профиля

516 просмотров профиля

-

ADF7242

Tanichev ответил Tanichev тема в RF & Microwave Design

Если бы бюджета по TX не хватало, то мы бы не смогли добиться нормальной передачи при вносимом затухании 75 дБ. Ещё раз: Eval Board Tx ---> аттенюатор до 75 дБ ---> Rx наша плата Eval Board Rx <--- аттенюатор до 20 дБ <--- Tx наша плата Наша плата Rx <--- аттенюатор до 20 дБ <--- Tx наша плата Если бы несущие Tx и Rx были бы сдвинуты, то, опять же, у нас была бы одинаково плохая связь в обе стороны. Это, ведь готовый трансивер, мы не можем особо влиять на бейсбенд, мы можем лишь менять скорость передачи. В-общем, мне не понятно, куда деваются 55 дБ)) -

ADF7242

Tanichev ответил Tanichev тема в RF & Microwave Design

Катушки такие бывают)) Дело даже не в фильтрах, т.к. включал и без них, разницы нет -

ADF7242

Tanichev опубликовал тема в RF & Microwave Design

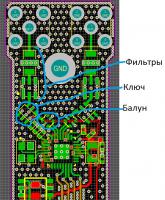

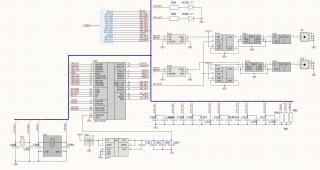

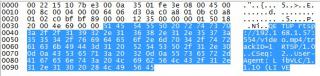

Исходные данные: трансивер у нас используется для передачи потокового видео с такими параметрами: 2 Mbps, GFSK, пакетный режим, данные передаются по SPI. Управляет трансивером FPGA Xilinx XC4VLX80. Чувствительность по даташиту на данной скорости: −87.5 dBm Даташит ADF7242 Суть проблемы: При достаточном уровне выходного сигнала (-2 dBm - измерено спектроанализатором) вносится затухание регулируемым аттенюатором. Если затухание 20 dB или больше, приёмник начинает "терять" пакеты. Однако, если в качестве передатчика использовать Evaluation Board (он также подключается через SPI к FPGA), при этом принимающий блок остаётся самодельный, то пакеты начинают "теряться" только при затухании 75 dB. Уровень выходного сигнала отладочной платы +2 dBm. Evaluation board: Спектры выходного сигнала самодельного блока и Evaluation board схожи. Далее прилагаю схему и разводку. Правда позже выяснилось, что балун на нашей плате включен неправильно, в качестве временной меры я сделал балун из катушек индуктивности и конденсаторов (как на Evaluation board). Вот так это теперь выглядит: Собственно вопрос: Что мы делаем не так? -

Может я не понял что-то, но вы пытаетесь преобразовать тип в указатель, хотя у вас переменная A не указатель. А ещё у вас массив содержит только 4 элемента 0...3, обращение к элементу номер 5 будет выходом за пределы массива. Я бы это написал так (для четвёрого элемента): A = (u16)(B[3]);

-

Спасибо! Я пользовался файлом UCF только для назначения выводов, т.к. больше про него ни чего не знал. Буду разбираться! Ещё раз спасибо!

-

Ну вот.. а я даже не знаю что такое констрейны, если не сложно, поясните пожалуйста :rolleyes:

-

Вопрос к гуру по ПЛИСненским делам: Создал в ISE проект некоторого периферийного модуля с шиной FSL, проверяю его работу без проца - просто залил проект в плисину. Использую внешний логический анализатор - всё работает именно так, как нужно. Но когда я добавляю свой блок с платформе с MicroBlaze, в работе модуля не всегда, но часто наблюдаются глюки типа: какой-либо сигнал, выходящий наружу, не работает, читаются неправильные значения из внутренних переменных... и т.д. При компиляции нет ни варнингов, ни ерорров указывающих на мой блок. Очень прошу помочь тех, кто знает решение этой проблемы. Заранее СПАСИБО!

-

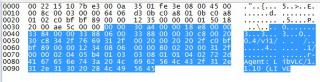

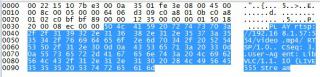

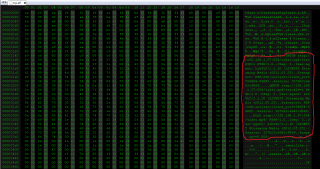

По мере работы с процессором появляются новые вопросы. Следующая "неадекватность" в работе программы проявилась в передаче указателя строки и последующего вывода её через ETHERNET. Код такой: TCPStringSend("SETUP rtsp://192.168.1.57:554/video.mp4/trackID=1 RTSP/1.0\r\nCSeq: 2\r\nUser-Agent: LibVLC/1.1.10 (LIVE555 Streaming Media v2011.05.25)\r\nTransport: RTP/AVP;unicast;client_port=54884-54885\r\nSession: 327b23c6643c9869\r\n\r\n"); TCPStringSend("QETUP rtsp://192.168.1.57:554/video.mp4/trackID=1 RTSP/1.0\r\nCSeq: 2\r\nUser-Agent: LibVLC/1.1.10 (LIVE555 Streaming Media v2011.05.25)\r\nTransport: RTP/AVP;unicast;client_port=54884-54885\r\nSession: 327b23c6643c9869\r\n\r\n"); TCPStringSend("PLAY rtsp://192.168.1.57:554/video.mp4/ RTSP/1.0\r\nCSeq: 3\r\nUser-Agent: LibVLC/1.1.10 (LIVE555 Streaming Media v2011.05.25)\r\nSession: 327b23c6643c9869\r\nRange: npt=0.000-\r\n\r\n"); В ходе решения проблемы я временно ограничил вывод строк 100 символами. В итоге, такие пакеты были получены компом (выделена область, содержащая строку): Пакет номер РАЗ: Пакет номер ДВА: Пакет номер ТРИ: Видно, что строка №1 дошла коряво. При этом были попытки заранее определить строки, сделать их переменными, но именно 3 строки отправлялись с глюками (две и одна - нормально). Я проверил содержание elf файла, но там все три строки хранятся правильно: Подскажите пожалуйста где я мог ошибиться. Спасибо PS Приведу на всякий случай коды своих процедур: int TCPStringSend(const char *DataBuffer) { u16 DataSize = 0; //while(/*DataBuffer[DataSize]*/*(DataBuffer + DataSize) != 0) DataSize++; TCPPackageSend(&SOURCE_IP_ADDRESS[0], &DESTINATION_IP_ADDRESS[0], DEVICE_DEFAULT_PORT, RTSP_DEFAULT_PORT, TCP_PSH | TCP_ACK, 0, DataBuffer, /*DataSize*/100); TCPClSequenceNum = TCPClSequenceNum + DataSize; return 0; } int TCPDataSend(const char *DataBuffer, u16 DataSize) { TCPPackageSend(&SOURCE_IP_ADDRESS[0], &DESTINATION_IP_ADDRESS[0], DEVICE_DEFAULT_PORT, RTSP_DEFAULT_PORT, TCP_PSH | TCP_ACK, 0, DataBuffer, DataSize); TCPClSequenceNum = TCPClSequenceNum + DataSize; return 0; } void TCPPackageSend(u8 *SourceIPAddr, u8 *DestinationIPAddr, u16 SourcePort, u16 DestinationPort, u8 Flags, u8 AddOptions, const char *DataBuffer, u16 DataSize) { u8 BufferToSend[1500]; u8 HeaderLength = 20; u16 BytesCounter = 0; u16 PacketLength = 0; u16 HeaderCheckSum = 0x0000; if(AddOptions == 1) { PacketLength = DataSize + 32; BufferToSend[20] = 0x02; BufferToSend[21] = 0x04; BufferToSend[22] = 0x05; BufferToSend[23] = 0xB4; BufferToSend[24] = 0x01; BufferToSend[25] = 0x03; BufferToSend[26] = 0x03; BufferToSend[27] = 0x08; BufferToSend[28] = 0x01; BufferToSend[29] = 0x01; BufferToSend[30] = 0x04; BufferToSend[31] = 0x02; HeaderLength = 32; PacketLength = DataSize + HeaderLength; for(BytesCounter = HeaderLength; BytesCounter < PacketLength; BytesCounter++) BufferToSend[BytesCounter] = DataBuffer[BytesCounter - HeaderLength]; } else { HeaderLength = 20; PacketLength = DataSize + HeaderLength; for(BytesCounter = HeaderLength; BytesCounter < PacketLength; BytesCounter++) BufferToSend[BytesCounter] = DataBuffer[BytesCounter - HeaderLength]; } BufferToSend[0] = (u8)((SourcePort & 0xFF00) >> 8); //Порт отправителя BufferToSend[1] = (u8)(SourcePort & 0x00FF); BufferToSend[2] = (u8)((DestinationPort & 0xFF00) >> 8); //Порт получателя BufferToSend[3] = (u8)(DestinationPort & 0x00FF); BufferToSend[4] = (u8)((TCPClSequenceNum & 0xFF000000) >> 24); BufferToSend[5] = (u8)((TCPClSequenceNum & 0x00FF0000) >> 16); BufferToSend[6] = (u8)((TCPClSequenceNum & 0x0000FF00) >> 8); BufferToSend[7] = (u8)(TCPClSequenceNum & 0x000000FF); BufferToSend[8] = (u8)((TCPSrvSequenceNum & 0xFF000000) >> 24); BufferToSend[9] = (u8)((TCPSrvSequenceNum & 0x00FF0000) >> 16); BufferToSend[10] = (u8)((TCPSrvSequenceNum & 0x0000FF00) >> 8); BufferToSend[11] = (u8)(TCPSrvSequenceNum & 0x000000FF); BufferToSend[12] = HeaderLength * 4; BufferToSend[13] = Flags; BufferToSend[14] = (u8)((TCP_WINDOW_SIZE & 0xFF00) >> 8); BufferToSend[15] = (u8)(TCP_WINDOW_SIZE & 0x00FF); BufferToSend[16] = 0; BufferToSend[17] = 0; BufferToSend[18] = 0; BufferToSend[19] = 0; HeaderCheckSum = tcp_sum_calc(PacketLength, SourceIPAddr, DestinationIPAddr, 0, &BufferToSend[0]); BufferToSend[16] = (u8)((HeaderCheckSum & 0xFF00) >> 8); //Контрольная сумма BufferToSend[17] = (u8)(HeaderCheckSum & 0x00FF); IPPackageSend(SourceIPAddr, DestinationIPAddr, TCP_PROTOCOL_TYPE, &BufferToSend[0], PacketLength); }

-

Полистал форум, не нашёл ответ на свой вопрос: - Создал я платформу в XPS, - Написал и отладил программу в EDK - всё отлично работает - Пришла пора записать готовую программу на плату - удалён модуль DEBUG из системы, проект собран в Release.. - Флэшка прошита (файл для флэш получен из download.bit) - НО! Программа "ждёт", что я нажму на кнопку в SDK: А нажать на неё я уже не могу, т.к. модуля DEBUG нет, да и вообще, платформа должна стать автономной. Видимо, где-то установлена какая-то галочка, которая меняет режим компилятора, я думал, что это переключается Debug/Release. Но видимо нет. Подскажите пожалуйста, где это делается. Спасибо.

-

Собирал платформу вручную, видимо. не нашёл, где и что указывать. Через визард работает. Спасибо за ответы

-

А почему у меня он всего один? Ведь XPS уже всё сделал. А это возможно вбить вручную? Как понимать эти координаты? Спасибо.

-

Пытаюсь собрать системку с MicroBlaze на Virtex-4 XC4VLX80. XPS собирает платформу нормально. Использую только BRAM. Затем, при попытке собрать прошивку вот так ругается: ERROR:Data2MEM:47 - Not all BitLanes in ADDRESS_SPACE 'microblaze_0.bram_block_0_combined' have BMM location constraints. Some data for this ADDRESS_SPACE may be lost during BIT file replacement. Verify that the BMM file has location constraints for all BitLanes. Bitlane(s) ---------------- bram_block_0/bram_block_0/ramb16_0 [31:31] bram_block_0/bram_block_0/ramb16_1 [30:30] bram_block_0/bram_block_0/ramb16_2 [29:29] bram_block_0/bram_block_0/ramb16_3 [28:28] bram_block_0/bram_block_0/ramb16_4 [27:27] bram_block_0/bram_block_0/ramb16_5 [26:26] bram_block_0/bram_block_0/ramb16_6 [25:25] bram_block_0/bram_block_0/ramb16_7 [24:24] bram_block_0/bram_block_0/ramb16_8 [23:23] bram_block_0/bram_block_0/ramb16_9 [22:22] bram_block_0/bram_block_0/ramb16_10 [21:21] bram_block_0/bram_block_0/ramb16_11 [20:20] bram_block_0/bram_block_0/ramb16_12 [19:19] bram_block_0/bram_block_0/ramb16_13 [18:18] bram_block_0/bram_block_0/ramb16_14 [17:17] bram_block_0/bram_block_0/ramb16_15 [16:16] bram_block_0/bram_block_0/ramb16_16 [15:15] bram_block_0/bram_block_0/ramb16_17 [14:14] bram_block_0/bram_block_0/ramb16_18 [13:13] bram_block_0/bram_block_0/ramb16_19 [12:12] bram_block_0/bram_block_0/ramb16_20 [11:11] bram_block_0/bram_block_0/ramb16_21 [10:10] bram_block_0/bram_block_0/ramb16_22 [9:9] bram_block_0/bram_block_0/ramb16_23 [8:8] bram_block_0/bram_block_0/ramb16_24 [7:7] bram_block_0/bram_block_0/ramb16_25 [6:6] bram_block_0/bram_block_0/ramb16_26 [5:5] bram_block_0/bram_block_0/ramb16_27 [4:4] bram_block_0/bram_block_0/ramb16_28 [3:3] bram_block_0/bram_block_0/ramb16_29 [2:2] bram_block_0/bram_block_0/ramb16_30 [1:1] bram_block_0/bram_block_0/ramb16_31 [0:0] FPGA Programming Failed due to errors while initializing bitstream. Я не могу понять, как собственно должен выглядеть этот файл :laughing: (он его сгенерил автоматически). Вот его содержание: // BMM LOC annotation file. // // Release 12.2 - Data2MEM M.63c, build 1.7 Jun 25, 2010 // Copyright (c) 1995-2011 Xilinx, Inc. All rights reserved. /////////////////////////////////////////////////////////////////////////////// // // Processor 'microblaze_0', ID 100, memory map. // /////////////////////////////////////////////////////////////////////////////// ADDRESS_MAP microblaze_0 MICROBLAZE 100 /////////////////////////////////////////////////////////////////////////////// // // Processor 'microblaze_0' address space 'bram_block_0_combined' 0x00000000:0x0000FFFF (64 KBytes). // /////////////////////////////////////////////////////////////////////////////// ADDRESS_SPACE bram_block_0_combined RAMB16 [0x00000000:0x0000FFFF] BUS_BLOCK bram_block_0/bram_block_0/ramb16_0 [31:31] INPUT = bram_block_0_combined_0.mem; bram_block_0/bram_block_0/ramb16_1 [30:30] INPUT = bram_block_0_combined_1.mem; bram_block_0/bram_block_0/ramb16_2 [29:29] INPUT = bram_block_0_combined_2.mem; bram_block_0/bram_block_0/ramb16_3 [28:28] INPUT = bram_block_0_combined_3.mem; bram_block_0/bram_block_0/ramb16_4 [27:27] INPUT = bram_block_0_combined_4.mem; bram_block_0/bram_block_0/ramb16_5 [26:26] INPUT = bram_block_0_combined_5.mem; bram_block_0/bram_block_0/ramb16_6 [25:25] INPUT = bram_block_0_combined_6.mem; bram_block_0/bram_block_0/ramb16_7 [24:24] INPUT = bram_block_0_combined_7.mem; bram_block_0/bram_block_0/ramb16_8 [23:23] INPUT = bram_block_0_combined_8.mem; bram_block_0/bram_block_0/ramb16_9 [22:22] INPUT = bram_block_0_combined_9.mem; bram_block_0/bram_block_0/ramb16_10 [21:21] INPUT = bram_block_0_combined_10.mem; bram_block_0/bram_block_0/ramb16_11 [20:20] INPUT = bram_block_0_combined_11.mem; bram_block_0/bram_block_0/ramb16_12 [19:19] INPUT = bram_block_0_combined_12.mem; bram_block_0/bram_block_0/ramb16_13 [18:18] INPUT = bram_block_0_combined_13.mem; bram_block_0/bram_block_0/ramb16_14 [17:17] INPUT = bram_block_0_combined_14.mem; bram_block_0/bram_block_0/ramb16_15 [16:16] INPUT = bram_block_0_combined_15.mem; bram_block_0/bram_block_0/ramb16_16 [15:15] INPUT = bram_block_0_combined_16.mem; bram_block_0/bram_block_0/ramb16_17 [14:14] INPUT = bram_block_0_combined_17.mem; bram_block_0/bram_block_0/ramb16_18 [13:13] INPUT = bram_block_0_combined_18.mem; bram_block_0/bram_block_0/ramb16_19 [12:12] INPUT = bram_block_0_combined_19.mem; bram_block_0/bram_block_0/ramb16_20 [11:11] INPUT = bram_block_0_combined_20.mem; bram_block_0/bram_block_0/ramb16_21 [10:10] INPUT = bram_block_0_combined_21.mem; bram_block_0/bram_block_0/ramb16_22 [9:9] INPUT = bram_block_0_combined_22.mem; bram_block_0/bram_block_0/ramb16_23 [8:8] INPUT = bram_block_0_combined_23.mem; bram_block_0/bram_block_0/ramb16_24 [7:7] INPUT = bram_block_0_combined_24.mem; bram_block_0/bram_block_0/ramb16_25 [6:6] INPUT = bram_block_0_combined_25.mem; bram_block_0/bram_block_0/ramb16_26 [5:5] INPUT = bram_block_0_combined_26.mem; bram_block_0/bram_block_0/ramb16_27 [4:4] INPUT = bram_block_0_combined_27.mem; bram_block_0/bram_block_0/ramb16_28 [3:3] INPUT = bram_block_0_combined_28.mem; bram_block_0/bram_block_0/ramb16_29 [2:2] INPUT = bram_block_0_combined_29.mem; bram_block_0/bram_block_0/ramb16_30 [1:1] INPUT = bram_block_0_combined_30.mem; bram_block_0/bram_block_0/ramb16_31 [0:0] INPUT = bram_block_0_combined_31.mem; END_BUS_BLOCK; END_ADDRESS_SPACE; END_ADDRESS_MAP; Подскажите пожалуйста, что нужно поправить в этом файле. Спасибо!

-

Всем спасибо! Всё заработало. Добавляю всё vhd и ngc файлы вручную

-

Ошибка такая: ERROR:NgdBuild:604 - logical block 't_xps_module_0/t_xps_module_0/XLXI_1' with type 'smth' could not be resolved. A pin name misspelling can cause this, a missing edif or ngc file, case mismatch between the block name and the edif or ngc file name, or the misspelling of a type name. Symbol 'smth' is not supported in target 'spartan6'. Я получается периферийный модуль сначала собираю в ISE, чтобы его отладить, потом делаю экспорт. Если в моём модуле нет corege-овских компонентов, всё собирается нормально, но если есть (в этом случае счётчик), то выходит такая ошибка. При экспорте он добавляет в pao vhd файл корки. Можете отправить содержание вашего pao файла?

-

Не получается, пока пробую. Делаю всё, как советуют: добавляю ngc файлы, создаю bbd файл, добавляю блок в проект заново. ошибка остаётся прежняя.. что-то где-то упускаю видимо