kt368

-

Постов

517 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные kt368

-

-

4 минуты назад, EvgenWL сказал:

Попробуйте выражение "All Xor OnSilkscreen" вместо всего, что указано на скриншоте

ничего не изменилось...

-

Здравствуйте.

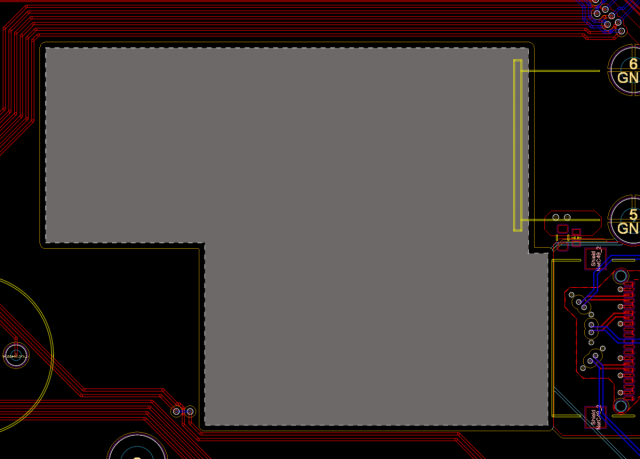

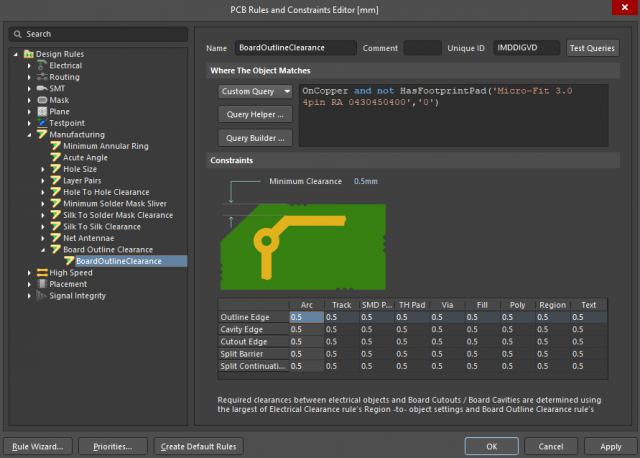

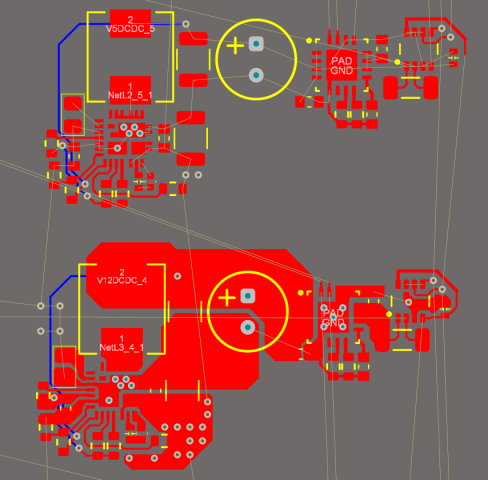

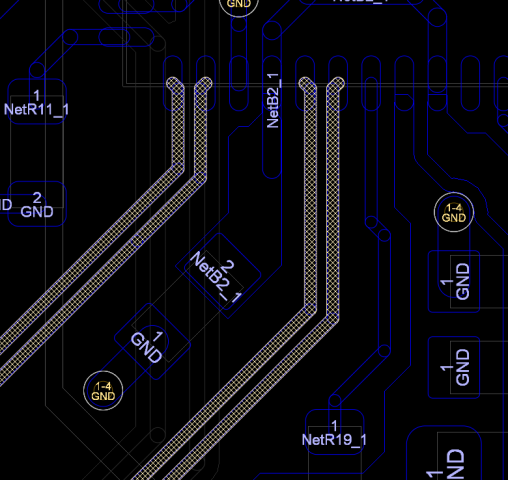

Некоторые разъёмы вылезают за габариты платы, и, для того, чтобы проверка "Board outline clearance" не считала это ошибкой, я в этом правиле использую фильтрацию по выражения OnCopper. Это срабатывает с границами платы, но не срабатывает с вырезами в плате, сделанными с помощью инструмента "Board Cutout". Вот скриншот этого участка платы:

Жёлтые линии USB-шного разъёма на слое Top Overlay ложатся на вырез в плате, и тут появляется violation.

Вот настройки DRC:

При производстве плат с этими линиями проблем нет - производители сами убирают их в гербер файлах.

Как вы советуете поступить с этими ошибками, чтоб не пришлось их все вручную waive ить?

-

Ой, да, пропустил что он управляется по току...

Из ассортимента тексаса нашёл подобный конденсатор только в даташитах на TPS54202 и TPS54308, и расчитывают их исходя из поднятия фазы на частоте crossover frequency, ёмкости порядка 33-100 pF.

Пожалуй, действительно, буду на практике играться с этим конденсатором, по факту напишу что получилось.

-

14 часов назад, borodach сказал:

если ваш скилл в ТАУ недостаточно прокачан, возьмите AOZ1282CI, без -1 или -2, она на более низкой частоте работает и этот конденсатор ей не нужен

Хочется попытаться сделать по-науке, поэтому, если не сложно, прокомментируйте следующие рассуждения:

Нашёл схожую микросхему у TI, LM3670. Тот же принцип управления и компенсации в ОС (ИМХО, если не так сильно не пинайте), та же частота,только не такая высоковольтная.

В её даташите есть рекомендации по расчёту этого конденсатора, они предлагают ноль, создаваемый этим конденсатором и верхним резистором в цепи ОС располагать на частоте 10 кГц. Этот ноль, как я понимаю, должен быть ниже crossover frequency, которая сильно зависит от параметров L и Cout. В даташите на LM3670 оперируют значениями индуктивности 4.7...10 uH, я для своей схемы предполагал использовать 47 uH (меньше пульсации тока в индуктивности), очень малый выходной ток позволяют это сделать. По-идее это отличие в индуктивности должно привести к более низкой crossover frequency, соответственно и частоту, на которой должен располагаться ноль, нужно тоже уменьшить. Правильно ли я рассуждаю?

И да, уменьшение crosover frequency по-сути ведёт к замедлению реакции преобразователя на скачкообразное изменение сопротивления нагрузки, верно? Т.е., возможно, индуктивность сильно увеличивать и не желательно?

-

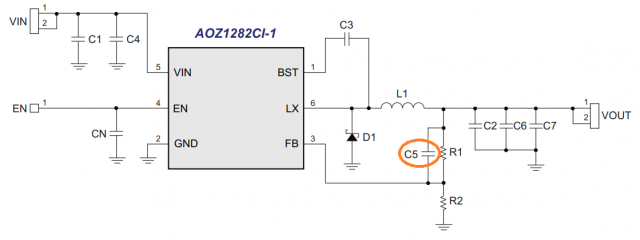

Здравствуйте.

Для питания МК (100 мА, 3.3 В) от имеющихся в устройстве 24В планирую применить AOZ1282CI-1.

Возник вопрос с номиналом конденсатора в цепи обратной связи (включён параллельно верхнему резистору делителя):

Он, как я понимаю, нужен для обеспечения стабильности цепи ОС, в даташите методики его расчёта нет. Кажется, в таких цепях обычно применяются конденсаторы порядка 5-22 пФ.

Хочу посоветоваться, что если я его возьму 10 пФ а потом при макетировании опытным путём проверю стабильность цепи ОС (посмотрю на реакцию при резком изменении тока нагрузки)?

-

Спасибо, работает!

Замечу, что эту команду нужно выполнять до репура полигонов. Если вы запустите репур полигонов, то, из-за того, что они не принадлежат ни к какой цепи, полигоны будут "пустые" (будут иметь только контуры, без заливки) и после "Design-Netlist-Update Free Primitive from Component Pads" им не присвоится никакая цепь.

-

Здравствуйте.

Есть проект с 10-ю одинаковыми DC-DC преобразователями. Сделал правильную разводку одного из них, далее с помощью функции Copy room formats копирую его разводку на другие преобразователи.

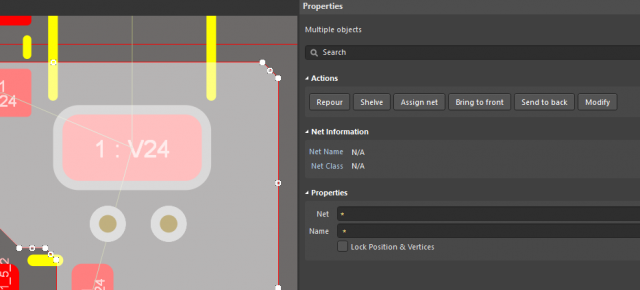

Расположение компонентов, их оириентация и треки скопировались успешн, полигоны не копируются. Для копирования полигонов я их скопом выделяю, а потом по привязке к какому-то паду копирую - вставляю их в другие преобразователи.

Скопированные полигоны не имеют цепей, т.е. в их свойствах "No Net". Было бы очень удобно, если бы полигону, при вставке его на существующий пад с присвоенной цепью, автоматически присваивалась бы цепь этого пада.

Сейчас приходится вручную выделять полигоны и указывать им цепи. Муторное занятие...

Иногда при вставке полигонов работает следующий "финт": Если полигон лёг на пад с присвоенной цепью, можно выделать этот полигон и пад, и тогда в панели Properties в разделе "Net Information" будет указана цепь, к которой подключён пад, и если зайти в поле свойств "Net", то вместо звёздочки там появится имя цепи, к которой подключён пад, и для присвоения такой же цепи полигону достаточно нажать "Enter". ТАк ыот, этот "финт" работает примерно в половине случаев, т.е., например, вчера при подобных операциях он работал, сегодня же - нет, и приходится имя цепи писать вручную

Бывают ли у вас такие же проблемы при использовании Copy room formats и копировании/вставке полигонов?

-

Здравствуйте.

Пытаюсь разобраться и начать использовать функционал панели "Collaborate, Compare and Merge".

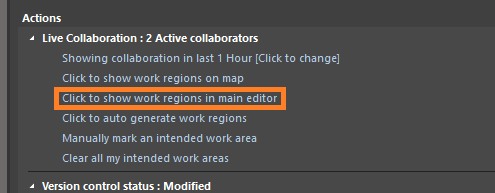

Вроде-бы всё получается, кроме показа рабочих регионов в главном окне редактора. Я так понял, при включении этого пункта (см картинку) рабочие регионы должны отобразиться в основном окне, в котором я выполняю трассировку платы?

Включение этого пункта никак не изменяет ничего в главном окне. Может нужно включить видимость чего-то в настройках (View Configuration или в настройках самого альтиума)?

-

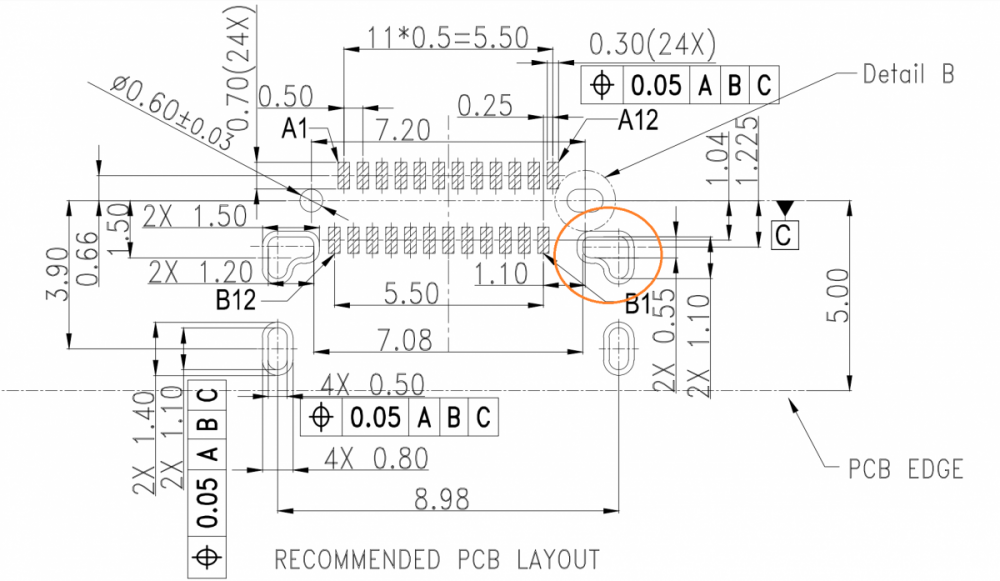

О, спасибо за наводку на PDF-ку с рекомендациями производителя, сделаю как в ней показано.

-

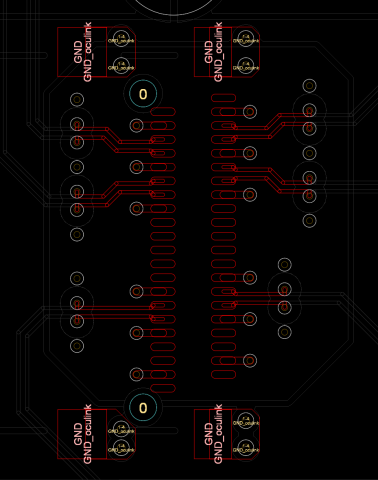

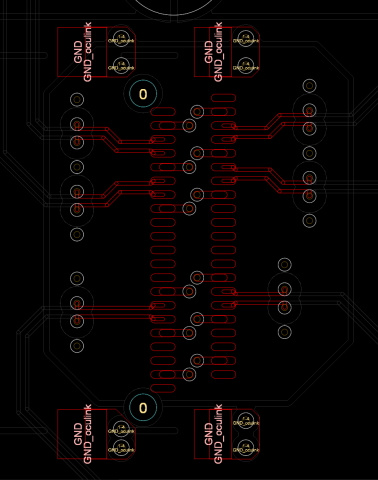

Здравствуйте. Требуется взять SATA диффпары (3 канала, 6 диффпар) с разъёма oculink. Решено установить разъём Molex P/N 1719820142.

Разъём установлен на верхний слой платы, диффпары должны идти по нижнему слою. Плата 4-х слойная.

Подскажите, какое подключение земли к референсным полигонам предпочтительнее? Мне кажется, что и тот и тот вариант допустим для SATA3, у каждого есть свои плюсы (имхо, может ошибаюсь), не могу определиться.

С этим типом разъёма сталкиваюсь впервые, ещё нет опыта/наработанных узлов платы.

-

Здравствуйте!

Подскажите, можно ли "протащить" harness через директиву Repeat?

Есть схема одного канала, в ней используется несколько диффпар. Можно используя многоканальную архитектуру вывести эти диффпары на схему верхнего уровня?

Я диффпары объединил в harnes'ы, а теперь не уверен, что из можно будет вывести по всей этой цепочке.

-

О, точно, FSO может по всей библиотеке ходить.

Спасибо большое!

-

Здравствуйте.

На одном из механических слоёв размещается информация, которая в последующем нужна для создания КД (она идёт в Assembly Drawing).

Подскажите, можно ли в pcblib файле перенести всё, что находится на этом механическом слое на другой механический слой скопом, для всех посадочных мест сразу?

Я понимаю, что можно в настройках Assembly Drawing выбрать другой слой, но по ряду причин интересует именно перенос со слоя на слой в самой библиотеке.

Заранее спасибо.

-

58 минут назад, misyachniy сказал:

"Продуктовая" подразумевает производство питания. Может "производственная"?

Да. Это все сленг из-за частого применения английского языка в работе :)

Уточню сразу на двух языках:

- Hardware product company

- Компания по производству аппаратного обеспечения

-

Мы - продуктовая компания Atola, №1 в своем сегменте рынка по всему миру. Наши системы используются для работы с жесткими дисками и восстановления данных. Более детальная информация - на сайте atola.com.На данный момент ищем инженера-электронщика, увлеченного своей профессией. Наша hardware-команда состоит из трех человек. Вы присоединитесь к ней и будете работать в киевском офисе.Чем предстоит заниматься в Atola:- Разработка специализированных компьютерных систем для работы с жесткими дисками, базирующихся на серверных компонентах- Комплексное проектирование плат и корпуса устройств- Эксперименты по развитию продуктов компании, поиск новых решений и идей- Регулярное общение и синхронизация при работе с командами программистов и QAОжидаем увидеть следующие качества:- Уверенное владение современной САПР для разработки электронных устройств- Владение современной механической САПР, умение проектировать корпус и платы устройства в комплексе- Системное мышление- Внимание к деталям- Cпособность продуктивно работать с большими техническими спецификациями (от 500 страниц)- Хорошие навыки по коммуникации в коллективе (умение внимательно слушать, умение формулировать свои мысли)- Уровень английского: Upper intermediateДополнительным преимуществом будет:- Опыт проектирования импульсных источников питания- Общее понимание принципов работы высокоскоростных интерфейсов- Опыт разработки устройств с интерфейсом PCIe- Опыт разводки BGA чипов- Опыт программирования микроконтроллеров- Практический опыт монтажа платУсловия работы:- Достойная зарплата с пересмотром раз в полгода- Дружный и дружелюбный коллектив- Собственный agile-подход по разработке hardware-продуктов- Гибкий график- Уютный офис в центре города в 5 минутах ходьбы от метро- 25 рабочих дней отпуска (24 + бонусный отпускной день 31 декабря)- Оплачиваемые больничные без необходимости брать справку- Напитки, еда в офисе за счет компании- English speaking club с преподавателемРезюме присылайте на адрес [email protected]

-

Разобрался, это участки, которые не проходят проверку по правилам диффпар, в данной случае расстояние между дорожками было меньше указанного в правилах.

Вопрос решён.

-

-

Пробую делать два перпендикулярных слота, всем спасибо.

-

Опубликовано · Изменено пользователем kt368 · Пожаловаться

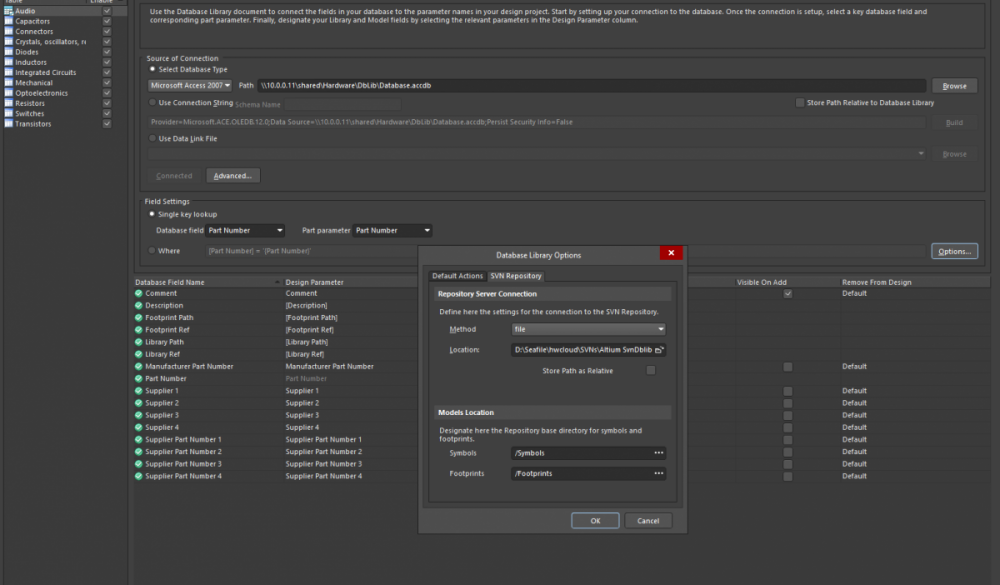

Здравствуйте.

При открывании SvnDbLib файла он часто открывается альтиумом как обычный dblib, при этом "Database library settings" выглядит как у dblib файла, т.е. не указан svn, а указана какая-то локальная папка. Если так открытый svndblib файл сохранить, то при всех последующих открытиях он будет открываться как обычный dblib файл.

И как вообще "правильно" открывать svndblib файл в альтиуме: через File-Open приходится в списке расширений вручную выбирать All Files, т.к. его нет в остальных категориях.

Такое чувство, что я что-то делаю не так.

Скрин "правльного открывания файла":

Скриншота "неправльного" открывания файла сечас нет, как будет - добавлю.

-

Опубликовано · Изменено пользователем kt368 · Пожаловаться

Слотовые отверстия мой производитель делает без проблем.

Получается, сделать его как вырез в контуре платы а затем в гербере на слое с аннотациями текстом объяснить производителю про металлизацию?

Вопрос был нет ли в альтиуме встроенного инструмента для создания такого пада.

-

Здравствуйте.

Подскажите, как можно в альтиуме сделать пад с отверстием сложной формы?

Если просто отверстие сложной формы, то я б сделал через Convert - Create Board cutout from selected primitives, но внутри такого отверстия не будет напыления меди, т.е. для пада это не подходит.

Это посадочное место для USB type C разъёма P/N 12401899E412A

-

Да, уже планирую в следующую версию устройств их поставить, от греха подальше.

-

Это устройство для копирования данных с разных источников: от PATA винчестеров до NVMe SSD. Через этот порт подключаются блоки расширения для поддержки внешних NVMe SSD, Apple SSD, в процессе разработки ещё нектороые блоки расширения.

Продолжаю эксперименты: ошибок не возникает при работе с внешним блоком расширения с NVME SSD, в нём "правильнее" сделана разводка дифф. пар, чем в блоке расширения Apple SSD. Видимо, поэтому линк с NVME работает, скорость DD в null - 3.2 ГБ/с .

Более того, включил блок расширения NVME через (!!!) 4 (!!!) внешних пассивные платы-удлинители PCIe (выполенны с соблюдением импедансов). И...... ВСЁ РАБОТАЕТ! На gen3! Я аж не ожидал. Кажется, в блоке расширения Apple SSD боооольшие проблемы с разводкой...

Но, т.к. в старых платах и с Apple SSD не было проблем ,то что-то китайцы проморгали в плате... Буду перезаказывать платы.

59 минут назад, Flood сказал:На этой плате есть M.2 коннектор. Для чего с такой материнкой нужен SSD от макбука?

Я могу ошибаться, но на мой взгляд, 4 коннектора на пути gen3 линка - чрезмерно много. Стандарт рассматривает максимум 2 коннектора в линке.

Если возможно, стоило бы поставить SSD в M.2 слот на мат. плате и этим решить проблему.

M.2 слот уже занят SSD для внутренних нужд устройства, да и цель - чтоб к закрытому устройству можно было снаружи подключать разные блоки расширения с интерфейсом PCIe.

-

Пассивно, цель - вывести PCIe порт наружу, для подключения внешних блоков расширения.

Altium Designer 19,избавиться от бегающей за курсором информацией

в Altium Designer, DXP, Protel

Опубликовано · Пожаловаться

Не советовал бы его убирать, там должна полезная инфа отображается. Предлагаю лучше закрепить его в левом верхнем углу окна. Для этого нужно его туда поместить, а потом зафиксировать его позицию комбинацией Shift+G.

И да, наполнение этого окна можно под себя настроить в "Preferences - Board Insight Modes". Очень рекомендую включить "last click delta" - прекрасная вещь!.