dortonyan

Участник-

Постов

77 -

Зарегистрирован

-

Посещение

Весь контент dortonyan

-

StewartLittle, спасибо за пояснения. Я просто выбирал между плисинами в корпусе QFP-144, а там только два типа: SA и SC.

-

MAX10_проблема

dortonyan опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую всех. Есть у меня проект, который собирается и работает на разных ФПГА (альтеровские циклоны и латтисовские FPGA). А теперь попробовал собрать этот же проект под MAX10 и вылезла проблема инициализации ROM. Квартус скачал версии prime 21.1.0. Плисину для проекта задал 10М08. Модуль памяти описан как массив с портами для чтения и записи, а так же с начальной инициализацией стандартной верилоговской ф-ей $readmemh с загрузкой данных из файла. Сначала при компиляции квартус выдал ошибку: Error (276003): Cannot convert all sets of registers into RAM megafunctions when creating nodes. The resulting number of registers remaining in design exceeds the number of registers in the device or the number specified by the assignment max_number_of_registers_from_uninferred_rams. This can cause longer compilation time or result in insufficient memory to complete Analysis and Synthesis Вроде как не хватает ячеек, хотя для моего проекта там ресурсов с избытком (в разы). Попробовал убрать функционал для записи в память, оставил только чтение и начальную инициализацию. И стало понятно почему не хватало ресурсов: проект собрался, но ROM почему-то синтезируется ячейками, не подключаются блоки M9K памяти (для RAM подключаются, для ROM - нет). Настройки синтеза не трогал, все по умолчанию. Но на всякий случай перепроверил опцию синтеза ROM из ячеек, опция включена. Кто-нибудь работал с MAX10 плисинами, что за фигня? P.S. Поторопился с созданием топика. Пока писал, нашел проблему. ) Надо просто в опциях девайса выбрать тип конфигурации с начальной инициализацией памяти: https://russianblogs.com/article/25521715884/ И такая опция есть только на МАХ10 плисинах с индексом SA. -

Спасибо всем! Да, я имел ввиду атрибуты, неправильно написал сразу. Атрибут syn_multstyle не прокатил. Нашел мануал по атрибутам для lattice и в нем описание для умножителей. У них он чутка иначе называется: /* synthesis syn_dspstyle="logic" */ С ним все собирается как надо. Единственное что получается не универсально, т.к. зависит от синтезатора. Может можно писать в строке несколько атрибутов подряд под разные синтезаторы?

-

Не ну есть же в верилоге директивы, типа запрета вырезания проводника оптимизацией. Подумал может что-то есть и для моего случая. А в синтезаторе там опций с гулькин нос. Да, он самый. Но опять же, там опций всего ничего. Может какая-то версия урезанная... Я и без хелпа уже посмотрел все что есть. Да, я тоже обратил внимание, что логика оптимизируется хуже, чем например MachXO2. Зато дешевые, и есть выделенные блоки DSP, что при необходимости построения умножителей компенсирует нехватку логики. Мой текущий проект как раз хорошо помещается в 2к плисину с 4-мя DSP блоками, но приходится второстепенные операторы умножения расписывать кейсами. Сделать то же самое автоматом компилятор почему-то не умеет.

-

Привет всем. Попробовал тоже работать с iCECube2 и возникла следующая проблема: В верилог коде использованы операторы умножения как для блоков умножения данных (DSP функционал), так и для второстепенных целей - в комбинаторной логике. Так вот в квартусе или диамонде все хорошо: компилятор малоразрядные умножители с небольшим набором комбинаций множимого и множителя заменяет комбинаторной логикой. А в кубе компилятор, видя оператор умножения, сразу же пытается подставлять для него DSP блоки. И т.к. блоков не хватает, то вместо того, чтобы заменить комбинаторной логикой - выдает ошибку. Пришлось в коде умножитель заменять кейсом, тогда все собирается как надо. Но это как-то неудобно. Можно ли как-то заставить компилятор куба использовать логику для построения простых умножителей? Или может быть есть для этого случая какая-нибудь верилог-директива?

-

Пошарил еще раз по опциям маппинга в диамонде и нашел аналогичную опцию запрета триггеров на портах. Отключил - заработала оптимизация маппингом как в квартусе. Вся разница была в том, что в квартусе эти триггеры по умолчанию выключены, а в диамонде наоборот включены.

-

Понятно, спасибо, буду знать. Просто при включении оптимизации фиттера обычно ресурсов расходуется на несколько ячеек меньше. Я решил, что значит тасует логику.

-

Так перемещение триггеров это и есть "поелозить круги по чипу". ) В общем на проекте с назначенными пинами оно тоже работает, может похуже (я сильно не сравнивал), но фронты ровняет. Я в одном проекте сразу пытался распиновку подбирать, чтобы получить сдвиги поровнее. Потом включил оптимизацию фиттера и понял, что занимался ерундой. )

-

Понятно. Т.е. он оптимизирует не логикой, а чисто маппингом. Ну соб-но для меня как юзера пофиг, главное что оптимизирует. Должно получиться то же самое. На проектах с назначенными пинами тоже оптимизирует. Фигово, что диамонд так не умеет. Походу он тупо оптимизирует на минимальные задержки маппинга.

-

Ура! Помогла директива /* synthesis syn_keep=1 */. des00, большое спасибо! Это гораздо проще констрейнтов (блин, еще выговори :)). Так что данный вопрос для себя я закрыл. Тем более, что высокая точность фронтов мне не требуется, грубой подгонки вентилями хватит. Остальное доделает оптимизация трассировщика.

-

Проект пожалуйста. Но там ничего особенного нету. Настройки синезиса по умолчанию. В настройках фиттера только галка переставлена на Standart Fit. DF2_output.rar Возможно в констрейнтах я написал какую-то фигню, с ними начал разбираться буквально вчера. Но это в любом случае не отменяет факта, что просто оптимизация фиттера двигает фронты на наносекунды. И это явно не за счет пикосекундных модулей задержки. Соб-но то же самое можно видеть на любом другом проекте, это я просто для примера привел.

-

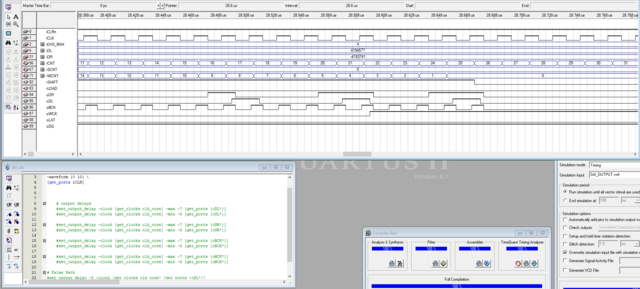

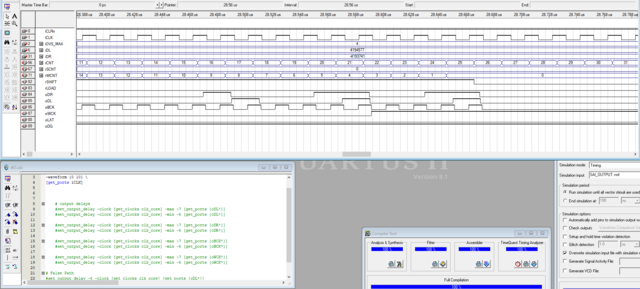

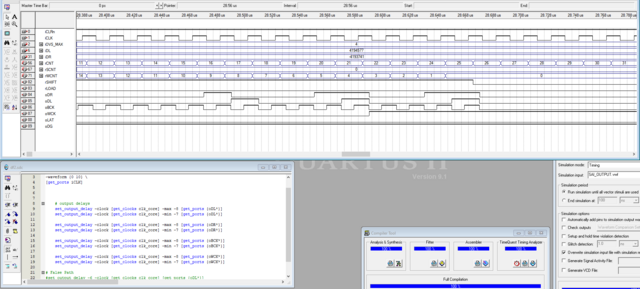

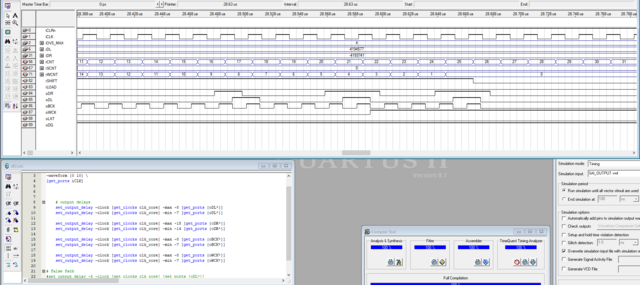

Может мы говорим про разные задержки, но даже просто включение оптимизации трассировщика запросто убирает разбежки фронтов на выходе в 3..5нс. Как еще если не перераспределением вентилей? Вот для примера выход с настройками трассировщика по умолчанию: Тактовая частота iCLK = 50МГц, т.е. 20нс период. Видно, что на выходных фронтах разбежки порядка 5нс. Включаем усиленную оптимизацию трассировщика: Гораздо ровнее. А теперь подключаем констрейнты: Выровнялось все идеально, не смотря на первоначальные разбежки в 5нс. А теперь допустим надо сдвинуть выход oDR на 7нс. Меняем констрейнт и получаем сдвиг: Можно и на 20нс сдвинуть. Все запросто двигается. Что не так? Спасибо за наводку, попробую поискать. А это я просто не догоняю как. Никогда не пользовался DDR.

-

Я полагал что это делается обычным перераспределением вентилей. Типа если надо задержка, то просто добавляется пара инверторов и готово. А в первом циклоне есть такие блоки? На нем все отлично двигается. Соб-но можно выровнять фронты, если в проекте на выход с отстающим фронтом добавить вентиль. Но чтобы компилятор его не вырезал при оптимизации придется выводить вход вентиля на входной порт. Получается какой-то костыль. Я думал что констрейнты для того и нужны, чтобы компилятор делал то же самое автоматом. P.S. Залез в мануал на MachXo2, там как и в циклоне есть модуль формирования задержек для DDR интерфейса. Это оно? 2-ой вопрос не понял. Как это вывести клок как дата? В смысле пересинхронизировать? Так я же в первом посте написал, что частота битклока на выходе равна частоте мастрклока, тактирующего плис.

-

Констрейнты в Lattice Diamond

dortonyan опубликовал тема в Среды разработки - обсуждаем САПРы

Собрал проект под LcmXO2 плисину. Но на выходе между сигналом данных и сигналом битклока получается разбежка порядка 10нс. Частота битклока равна частоте тактового клока, поэтому выполнить пересинхронизацию обоих сигналов не получается. Настройки оптимизации трассировщика исправить ситуацию не помогли. Поэтому решил выровнять фронты констрейнтами. Скачал мануалы по диамонду, нашел как задаются ограничения для цепей. Но не тут-то было. Что не задаю, ничего не меняется. Репорт показывает всегда задержку Clock to Output: 14 нс для одного сигнала и 24..28 нс для другого. Пробовал через SpreadSeed->Preference: задать задержку в меню "CLOCK_TO_OUTPUT". Попробовал задать констрейны через SDC файл (командой set_output_delay) - ничего не меняется. Причем диамонд DSC файл подключает, ограничения в репорте пишет, но тайминги "Clock to Output" не меняет. Для проверки SDC констрейнов подключил этот же файл к проекту в квартусе. Там все отлично работает, фронты двигаются взад-вперед на любой заданный тайминг. В диамонде ничего не меняется. Не пойму что я делаю не так, уже поломал голову разбираться. Может нужно включить какую-то опцию в трассировщике? Кто-нить знает как правильно задавать констрейнты в диамонде? -

Проблема с Матлабом

dortonyan ответил _sda тема в Вопросы системного уровня проектирования

Приветствую всех. Имею тоже проблемку, заключающуюся в выводе данных. Для расчета КИХ фильтра использую приложение Filter Builder. Полученные коэф-ты выводятся в графическом окне. Далее для работы с этими коэф-тами я их копирую из графического окна в эксель, но это очень неудобно. Т.к. их нельзя выделить целиком, и в окне нет меню для экспорта коэф-тов в текстовый файл. Подскажите, есть ли способ выполнить экспорт расчитанных коэф-тов в хоть какой текстовый файл, или консоль, чтобы можно было их копировать целиком? -

QUARTUS, MODELSIM

dortonyan ответил aosp тема в Среды разработки - обсуждаем САПРы

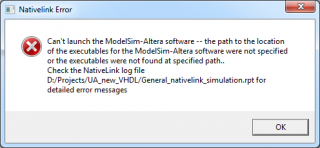

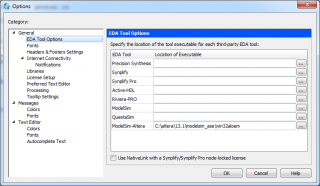

Привет всем. Пытаюсь запустить моделсим из квартуса. Скачал последнюю 13-ю версию квартуса и моделсима с сайта альтеры. Написал простенький код на VHDL, скомпилировал, все гуд. Но при попытке запуска RTL анализа появляется окно с ошибкой о ненайденом исполнительном файле modelsim-altera: Проверил в опциях путь, все ок: Кто-нибудь узал 13-ый квартус с моделсимом? Не могу понять где косяк. -

msalov, спасибо за пояснения - точно, подзабыл. И вторая ваша запись конечно получше будет.

-

Привет всем. Такая ламерская проблемка с PIC32: не могу найти трабл в программе. Написал код на си последовательного вывода данных, в котором передается 5-тирязрядное число. unsigned char Data = 15; // 5-ти разрядное число unsigned char i; for (i=0; i<5; i++) { mPORTBClearBits(BIT_3); // CLK установить 0 if (Data && 16) mPORTCSetBits(BIT_0); // DAT установить 1 else mPORTCClearBits(BIT_0); // DAT установить 0 Data <<= 1; // Сдвиг mPORTBSetBits(BIT_3); // CLK установить 1 } В результате, если значение Data = 0, то на выходе порта данных ноль. Но если задано число больше нуля, то на выходе данных все 5 тактов единицы, независимо от значения числа. В симуляторе проверял значение регистра Data - оно сдвигается, как и положено. Т.е. неправильно работает условие побитового "И": всегда дает единицу, при значении Data > 0. Не могу понять почему.

-

Вопросы начинающих

dortonyan ответил KA_ru тема в Altium Designer, DXP, Protel

Спасибо, попробую так. Появилась еще проблемка. Создал новый проект, и как-то отключилась полезная ф-я. Суть ее в том, что когда я скрываю слои (shift+s) компоненты из скрытого слоя все еще можно передвигать. Где можно эти настройки посмотреть? В старом проекте все гуд (компененты в скрытом слое не двигаются), т.е. это какая-то локальная установка в проекте. В настройках борды ничего такого не нашел. -

Вопросы начинающих

dortonyan ответил KA_ru тема в Altium Designer, DXP, Protel

Iptash, так тоже пробовал - не прокатывает. После перезапуска прога сбрасывает эти установки на прежние. -

Вопросы начинающих

dortonyan ответил KA_ru тема в Altium Designer, DXP, Protel

И мне подскажите, кто знает. Как установить в PCB редакторе настройку яркости сетки по умолчанию? Вручную устанавливаю так: Design->Board options->Grids->Coarse. Яркость делаю Darker, но после перезапуска прога сама сбрасывает настройки отображения PCB и сетки на значения по умолчанию. Смотрел в настройках DXP->Preference->PCB editor->Defaults, пункта настройки сетки нет, где еще можно посмотреть? Или как отключить сброс настроек на умолчания? -

Разные вопросы

dortonyan ответил [email protected] тема в Altium Designer, DXP, Protel

Пнял, я думал видяха нужна только в 3Д. Сейчас пользуюсь интегрированной. -

Разные вопросы

dortonyan ответил [email protected] тема в Altium Designer, DXP, Protel

Привет всем. Вопрос по производительности AD. В трассировщике при удалении проводника или рисовании нового AD периодически задумывается, бывает даже на пару секунд. Такие зависания раздражают и замедляют работу. Можно ли это победить какими-то настройками, или таков движок AD и с этим ничего не поделать? В Rulse все что можно поодключал - не помогло. -

Да я в курсе, что не предполагают. Видел схему УВХ на 2SK241, которые тоже позиционируются как RF усилители. Я бы и пользовал аналогичные транзисторы, но им на смену пришли двухзатворные усилители, которые видимо удобнее для построения модуляторов. А ток утечки как для RF транзисторов, так и для ключей прямо нигде не указывают. В документациях пишут только номинальное напряжение запирания ключа при токе стока 1..10uA. Конечно если увеличить запирающий потенциал, то ток утечки по идее соот-но уменшится, но прямо это нигде не указано. В общем, раз такое мутное дело - надо макетировать, пробовать.

-

Это как? Там же потенциалы по обе стороны ключей почти неизменны. Под интегрирущим УВХ я имел ввиду инвертированный интегратор с ключами на виртуальной земле. Про сопутствующие проблемы я как бы в курсе. Больше интересует применимость двух-затворых ВЧ мосфетов в данном случае.