ims

Участник-

Постов

19 -

Зарегистрирован

-

Посещение

Весь контент ims

-

Резистивный делитель и ТКС

ims ответил ims тема в Схемотехника

В штучные можно резисторы и по доллару поставить. Или сборки, как MrYuran предлагал... Я так понимаю, это зависит от нюансов технологии. Читал когда-то про толстопленочные, вроде. Там изначально делали пленку заведомо меньшего сопротивления и лишнее отжигали лазером. В этом случае каждый резистор подгоняется индивидуально, и вряд ли стоит ожидать сильную корреляцию соседей по ленте по сопротивлению... ТКС, по идее, да, как сплавили материал, так и получится для всей партии. Но кто знает, что там их роботы начудят :rolleyes: -

Резистивный делитель и ТКС

ims ответил ims тема в Схемотехника

Да, конечно. Или дискретные с малым ТКС... Просто с детства отложилось, что делитель на однотипных резисторах малочувствителен к ТКС, ибо ползут одинаково. А "±" в даташитах не замечал годами... Получается, что стремиться к выравниванию температуры на резисторах делителя совершенно бессмысленно... -

Резистивный делитель и ТКС

ims опубликовал тема в Схемотехника

Добрый день! Для резисторов общего назначения производители обычно нормируют ТКС симметричным допуском, например, здесь. В то же время, бытует мнение, что применение однотипных резисторов в делителе существенно уменьшает температурный дрейф. Например, здесь об этом говорил ув. Herz. Хотелось бы разобраться, какие есть этому основания, и какой остаточный дрейф отношения сопротивлений можно ожидать? Другими словами. Пусть требуется резистивный делитель на 2, который в диапазоне температур 20...120 градусов должен иметь дрейф не более ±1%. Можно ли обоснованно заложить в схему два одинаковых резистора с ТКС ±100ppm, или необходимо применение более экзотичных с ТКС ±50ppm? -

INPUT_SETUP в Lattice Diamond

ims ответил ims тема в Среды разработки - обсуждаем САПРы

Пробовал — по отчету видно, что задержка вывода клока не учитывается. Synplify может и старается, но в LPF это скорее всего описать нельзя. Примеров констрейнов для "FPGA-synchronous input" в материалах Lattice я не нашел. Вот синтезируемый пример: module top ( input clk, output pll_clk, input d1, input d2, input d2_clk, output reg q1, output dummy ) /* synthesis syn_useioff = 1 */; PLLa _pll (.CLKI(clk), .CLKOP(pll_clk)); // Ввод на клоке PLL ПЛИС reg rd1; always @ (posedge pll_clk) rd1 <= d1; // Ввод на внешнем клоке reg rd2; always @ (posedge d2_clk) rd2 <= d2; // Вывод на клоке PLL ПЛИС always @ (posedge pll_clk) q1 <= dummy; assign dummy = rd1 ^ rd2; endmodule LPF: BLOCK RESETPATHS; BLOCK ASYNCPATHS; INPUT_SETUP PORT "d1" 10 ns HOLD 10 ns CLKNET "pll_clk_c"; # CLKPORT "pll_clk" не работает FREQUENCY PORT "d2_clk" 20 MHz; INPUT_SETUP PORT "d2" 10 ns HOLD 10 ns CLKPORT "d2_clk"; CLOCK_TO_OUT PORT "q1" 10 ns MIN -10 ns CLKNET "pll_clk_c" CLKOUT PORT "pll_clk"; (Diamond сам создает клоки clk_c и pll_clk_c в соответствии с настройками PLL, как бы неявно выполняет derive_pll_clocks -create_base_clocks) Из post-fit отчета Trace видно следующее: 1) Для входа d1, который мы хотим тактировать сгенерированным клоком, рассчитывается PADI_DEL + ROUTE данных от ножки d1 к регистру rd1, ROUTE клока от PLL к регистру rd1, и все… Задержка сгенерированного клока от PLL к ножке и наружу не рассчитывается. Дополнительных параметров, аналогичных CLKOUT PORT для CLOCK_TO_OUT, INPUT_SETUP не поддерживает. 2) Для входа d2 с тактированием от внешнего клока на d2_clk все правильно: PADI_DEL + ROUTE данных от ножки к регистру и PADI_DEL + ROUTE клока от ножки к регистру. 3) Для выхода q1 с тактированием сгенерированным клоком тоже все правильно: ROUTE клока от PLL к регистру, ROUTE + OP0PAD_DEL от регистра к ножке, ROUTE + DOPAD_DEL от PLL до ножки для сгенерированного клока. Во вложении архив проекта. constr.zip -

INPUT_SETUP в Lattice Diamond

ims ответил ims тема в Среды разработки - обсуждаем САПРы

Я попробовал. Synplify из SDC сгенерировал LPF с констрейнами вида INPUT_SETUP "adc_data[7]" 40.0 NS CLKPORT = "adc_clk"; ... На это Map выдал WARNING: Semantic error in "INPUT_SETUP PORT "adc_data[7]" 40.00000 ns CLKPORT "adc_clk" ;": "adc_clk" matches no clock ports in the design. This preference has been disabled. Соответственно, дальше анализ этих констрейнов не выполнялся. Я так понимаю, в качестве CLKPORT обязательно должна быть ножка с входным внешним клоком, сгенерированные клоки CLOCK_TO_OUT не понимает. Ну да, против лома... Задержку вывода клока от PLL наружу даже получается удобно сосчитать в Diamond — у меня есть выходной сигнал, который выдается относительно того же adc_clk, и величина задержки, оказывается, есть в отчете соответствующего CLOCK_TO_OUT. Криво это, но похоже нормального способа нет. Странно, задача ведь совершенно стандартная... -

INPUT_SETUP в Lattice Diamond

ims ответил ims тема в Среды разработки - обсуждаем САПРы

Timing Closure 3.10 смотрел. Зачем CLKSKEWDIFF в данном случае? CLOCK_TO_OUT констрейнит выход, вопрос про вход... Собственно, как раз CLOCK_TO_OUT сделан правильно — там есть параметр CLKOUT PORT, который позволяет указать, с какой ножки генерируется клок для внешнего мира. Как раз такого параметра явно не хватает INPUT_SETUP... -

INPUT_SETUP в Lattice Diamond

ims опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день! Простая задача: ввод данных с АЦП в MachXO2. АЦП тактируется от PLL ПЛИС: module top (input clk, output adc_clk, input [7:0] adc_data); PLL _pll (.CLKI(clk), .CLKOP(adc_clk)); reg [7:0] rdata; always @ (posedge adc_clk) begin rdata <= adc_data; // Дальше работаем с rdata... end endmodule В Quartus/TimeQuest временные ограничения для шины данных можно было бы задать так: create_generated_clock -name {adc_clk} -source [get_pins {_pll/PLLInst_0/CLKOP}] [get_ports {adc_clk}] set_input_delay -clock {adc_clk} -max [...] [get_ports {adc_data[*]}] set_input_delay -clock {adc_clk} -min [...] [get_ports {adc_data[*]}] При этом учитывается как задержка данных на входных буферах ПЛИС, так и разность времен распространения клока от выхода PLL через кристалл наружу и от выхода PLL до регистров внутри ПЛИС. В Lattice Diamond SDC не поддерживается (во всяком случае, в Place & Route и I/O Timing Analysis). Задавать временные ограничения нужно в LPF. В LPF ничего похожего на create_generated_clock нет. Аналогом set_input_delay является INPUT_SETUP. Вроде бы естественно написать: INPUT_SETUP PORT "adc_data*" ... ns HOLD ... ns CLKPORT "adc_clk"; Однако при этом, судя по отчету, в расчет берется только PADI_DEL + ROUTE данных минус ROUTE клока от PLL к регистру. Задержка вывода клока от PLL наружу не учитывается, что делает такой анализ бессмысленным. Вопрос: как правильно задать временные ограничения для этого интерфейса в Diamond? -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

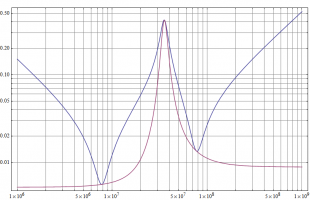

Вот прямо противоположные рекомендации Альтеры AN574 (p.16): Действительно, для параллельного соединения конденсаторов из поста #1 (1мкФ + 4x10нФ) ESR получается большой: (синяя линия - |Z|, красная - Re(Z)). При параллельном соединеним разных конденсаторов в импедансе появился полюс на частоте 35МГц с добротностью 6. Соответственно, симуляция отклика на ступеньку тока 1А при нагрузке 1Ом показывает довольно значительные колебания: Почему Альтера считает, что это полезно? Или я что-то не так понял? -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

Я параметры тоже брал из SimSurfing, только переключил модель с Precise на Simple. Забавно, что в упрощенной модели SRF сдвинута на 5.5МГц, как Вы наглядно показали на графиках. -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

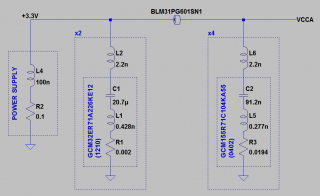

91.2нФ из-за DC bias 3.3V. Модели брал из SimSurfing Murat-ы - там можно получить C-L-R Netlist для конкретного смещения по постоянке. Оттуда же и модель BLM. С бусинами протупил, действительно, все написано. Даже, оказывается, читал когда-то альтеровские аппноты, но не отложилось, что резонансы могут получаться настолько низко. Теперь дошло :rolleyes: -

Параллельное включение блокировочных конденсаторов

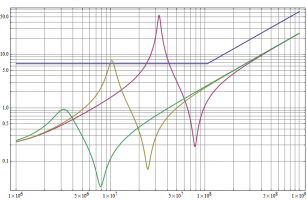

ims ответил ims тема в Схемотехника

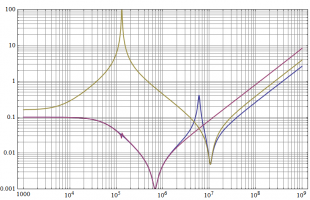

Еще немного картинок :rolleyes: На рисунке приведен вариант развязки шин цифрового и аналогового питания (например, для PLL или АЦП): Импеданс источника питания моделируется резистором 0.1Ом и дросселем 100нГн. Bulk-конденсаторы на основной шине +3.3В - 22мкФ (1206), 2шт. Блокировочные конденсаторы на шине VCCA - 0.1мкФ. Монтажная индуктивность конденсаторов - 2.2нГн. Между шинами - BLM31PG601SN1. Результат расчета импеданса по моделям Murata: Синяя линия - импеданс с закороченной бусиной. Как обычно имеет место резонансный пик на частоте 6МГц из-за взаимодействия конденсаторов разных номиналов. Красная линия - импеданс со стороны шины +3.3В при наличии бусины. Пик на частоте 6МГц полностью исчез. Желтая линия - импеданс со стороны шины VCCA при наличии бусины. На частоте 131кГц появился резонанс большой амплитуды (123Ом). Действительно, из модели BLM31PG601SN1 следует, что на низких частотах бусина ведет себя как дроссель с индуктивностью около 4мкГн. Совместно с емкостью около 400нФ это приводит к низкочастотному резонансу. Если в схеме добавить на шину VCCA керамический конденсатор 10мкФ с малым ESR, то основной резонанс сгладится и уйдет ниже по частоте (4Ом 31кГц), но появится еще один поменьше (0.6Ом @ 5МГц): Если последовательно с керамическим конденсатором 10мкФ включить демпфирующий резистор 2 Ома, как, например, рекомендуют здесь, то низкочастотный резонанс снизится еще в два раза (1.4Ом @ 29кГц), а высокочастотный резонанс останется на месте: М.б. это всем известно, но для меня низкочастотные "пакости" от бусин были полной неожиданностью. Бусины всегда ассоциируются с высокими частотами, и та же Murata приводит характеристики от 1МГц. -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

С симуляцией все сходится. Расчет «по Отту» обещает только то, что если модуль импеданса не превышает Zt (с учетом разрешенного подъема на 20дБ/декада после fc), то амплитуда пульсаций dV не превышает 0.5*J*Zt (J - размах тока пульсаций). В посте #33 так и получилось: для варианта с конденсатором 100нФ пульсации в симуляторе 80мВ пик-пик (амплитуда 40мВ), что с запасом меньше «целевых» 100мВ. Выделять отдельно низкочастотные и высокочастотные пульсации, как сделал я, в этом контексте бессмысленно. Упражнения с математикой только из-за того, что по тексту Отта мне показалось, что оценка dV<=0.5*J*Zt является строгим математическим следствием принятой модели потребления в виде треугольных импульсов тока. Ни доказать ни опровергнуть это у меня сходу не получилось. Но это и не важно – можно рассматривать как эмпирическую методику. Тем более, что с ней согласуются даже грубые предельные случаи вроде голого дросселя на ножках питания. Хотелось бы еще выяснить, как правильно оценивать индуктивность коротких дорожек. Например, для дорожки длиной 1,5мм получилось около 1нГн - больше, чем индуктивность via. Но общая формула справедлива для длинных дорожек, l>>h... Правильно ли я понимаю, что при расчете развязки индуктивностью plane-ов принято пренебрегать? Во всяком случае, в альтеровской PDN Tool судя по эквивалентной схеме это вроде бы так… Еще, у Отта в разделе 11.4.5 есть странный пассаж: Интересно, какого порядка индуктивность внутренних соединений, например, в каком-нибудь большом QFP? Если она того же порядка, что индуктивность дорожки или via, на каком основании ею можно пренебречь? В общем, пока не все ясно :rolleyes: -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

На самом деле амплитуду можно строго оценить сверху (tr - время нарастания, T - период следования импульсов): Если считать, что модуль импеданса везде не превышает Zt, то Но это амплитуда, пик-пик размах в два раза больше... Кстати, в посте #33 у меня ошибка. 40дБ/декаду это спадание амплитуды гармоник треугольных импульсов. Целевому импедансу Отт "разрешает" расти (без особого обоснования) на 20дБ/декаду после fc=1/(pi*tr). Для этого случая оценка амплитуды V расходится. Исправленный график |Z(f)| для поста #33: -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

Для гармонического источника все сходится - dV=J*|Z(f)| (без двойки, конечно). Насчет "гармонического импеданса" - это Вы знатно сказали :rolleyes:. Если импульсы тока периодические, то в линейной схеме независимо от формы импульсов Фурье-спектр напряжения связан с Фурье-спектром тока через импеданс: Vn=Jn*Z(fx*n), где fx - частота следования импульсов, n - номер гармоники. Если мы задаемся целевым предельным значением модуля импеданса, то, зная спектр тока, можем однозначно оценить сверху среднеквадратическое значение напряжения пульсаций. А вот амплитуда... Я так понимаю, она может получиться любая, как фаза ляжет... -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

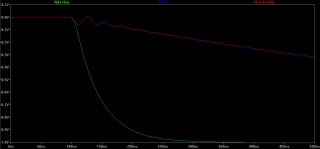

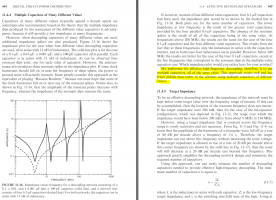

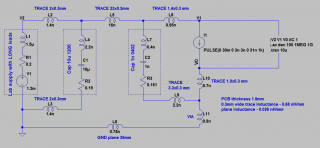

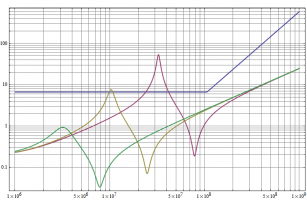

Да, "хочется освоить цепочку анализа". Сейчас я разбираюсь с книгой Отта (Henry W. Ott Electromagnetic Compatibility Engineering), из которой Alexashka приводил графики в сообщении 11. Для большей ясности хотелось бы разобрать простой модельный пример. Буду признателен, если участники форума найдут возможность покритиковать. Пусть есть двусторонняя плата FR-4 толщиной 1,5мм, разведенная, как показано на рисунке. Ширина дорожек 0,3мм (разводка намеренно плохая для усиления паразитных эффектов и упрощения расчета). На плате установлен единственный активный элемент - инвертор LVC1G04. Частота передачи данных до 100Мбит/с. Выход нагружен на CL=10пФ. Питание VCC=3.3В подводится слева, от источника с большим ВЧ импедансом (например, от лабораторного БП через длинные провода). Развязка питания выполнена блокировочным конденсатором 0402 в непосредственной близости от МС и bulk-конденсатором 1206 10мкФ на расстоянии 25мм. Нижняя сторона платы – сплошной земляной полигон. Оценим поведение схемы при номиналах блокировочного конденсатора 0402 1нФ, 10нФ, 100нФ. Топологию и остальные параметры схемы не меняем. Анализ: 1) Согласно даташиту Cpd=18пФ. Время нарастания tr в даташите не указано, принимаем равным 3нс. 2) Амплитуда динамического тока J = (CL+Cpd)*Vcc/tr = 30мА [Ott eq.11-1, 11-2b]. 3) Целевой импеданс для амплитуды пульсаций dV=0.1В (3% от Vcc) - Zt=2*dV/J=6.7Ом, граничная частота fc=1/(pi*tr)=106МГц [Ott 11.4.5]. 4) Эквивалентная схема для расчета импеданса приведена на рисунке, schematic для LTSpice во вложении. Микросхема моделируется источником тока (треугольные импульсы Trise=Tfall=3нс, амплитуда I1=0, I2=30мА) [Ott 11.2.1]. Индуктивность дорожки шириной 0.3мм при расстоянии до полигона 1.5мм — 0.68нГн/мм [Ott eq.10-5], индуктивность полигона — 0.026нГн/мм [Ott Fig.10-19], индуктивность межслойного - 0.8нГн ("типичное значение" из [Ott]). Паразитные параметры конденсаторов взяты из альтеровской PDN Tool (0402 1нФ — L=0.4нГн, R=161мОм; 0402 10нФ — L=0.4нГн, R=60мОм; 0402 100нФ — L=0.4нГн, R=28мОм). 5) Результат расчета импеданса приведен на графике. Синяя линия - целевой импеданс (рост 40дБ на декаду выше граничной частоты). Положения максимумов: (32.6МГц, 54Ом), (10.3МГц, 7.6Ом), (3.2МГц, 0.94Ом). Таким образом, номиналы 1нФ и 10нФ не проходят по целевому импедансу, а 100нФ – проходит. 6) Симуляция эквивалентной схемы в LTSpice дает следующие оценки для пик-пик пульсаций напряжения питания на микросхеме (V(V1)-V(V0)) в установившемся режиме на частоте максимума импеданса: 0402 1нФ f=32.6МГц — 628мВ 0402 10нФ f=10.3МГц — 31мВ НЧ + иголки 6нс 82мВ 0402 100нФ f=3.2МГц —1.4мВ НЧ + иголки 6нс 80мВ Вопросы. Амплитуда иголок в вариациях с 10нФ и 100нФ одинакова из-за того, что на высоких частотах импедансы для этих двух случаев практически одинаковы. Правильно? Амплитуда низкочастотных пульсаций при симуляции получается намного меньше, чем должно быть по формуле dV=J*Z/2 (31мВ против 114мВ, 1.4мВ против 14.1мВ). Как это можно объяснить? Хотелось бы также услышать замечания по эквивалентной схеме и расчету паразитных индуктивностей. P.S. Не надо больше про STM32F103. У меня нет проблем с его разводкой. Эта тема скорее методически-образовательная :rolleyes:. pdn1.rar -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

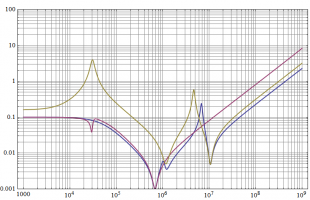

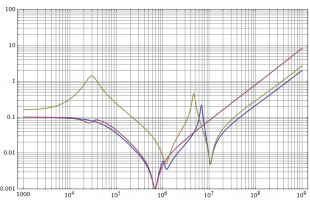

Графики |Z(f)| для схем из поста Alexashka #22: 0,1мкФ + 10нФ; 0,1мкФ + 10нФ + 1нФ + 100пФ; четыре конденсатора 0,1 мкФ. Добавочные индуктивности везде 8нГн. -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

Графики |Z(f)| для схем из поста Alexashka #22: 0,1мкФ + 10нФ; 0,1мкФ + 10нФ + 1нФ + 100пФ; четыре конденсатора 0,1 мкФ. Добавочные индуктивности везде 2нГн. -

Параллельное включение блокировочных конденсаторов

ims ответил ims тема в Схемотехника

С Вашими графиками согласиться не могу. Посмотрите, например, на характеристики CGA3E1X7R1C105KT на сайте производителя. В окрестности резонанса на графике есть характерный "клювик" – на Ваших кривых его нет. На частоте резонанса импеданс должен быть равен ESR (R1 в модели) – у Вас намного больше. Скорее всего, Вы потеряли мнимые единицы в импедансе конденсатора и дросселя: 1/(i ω C), i ω L. Если у Вас под рукой есть пакет Mathematica, посмотрите программу, которой я строил графики. Ошибиться там сложно. Нет, не учитывал. Не могли бы привести поддающуюся расчету эквивалентную схему? Хотелось бы разобрать по возможности упрощенный пример, на котором можно убедиться расчетом, что при некоторых заданных условиях схема (с процессором или с дискретной логикой) будет работать с блокировочным конденсатором 0402 10нФ, и не будет работать, например, с 1206 100нФ (или, совсем грубо, с электролитом 10мкФ). capacitor_impedance2a.rar -

Параллельное включение блокировочных конденсаторов

ims опубликовал тема в Схемотехника

Добрый день! Для развязки питания цифровых схем обычно рекомендуется параллельное включение конденсаторов разных номиналов для получения низкого импеданса в широком диапазоне частот. Например, здесь для развязки питания STM32F103 ув. =AK= советует параллельное включение конденсатора 1мкФ и 4-х конденсаторов 10нФ. Если взять эквивалентные схемы конденсаторов, например, для серии CGA3, и построить график зависимости модуля импеданса для параллельного включения 1мкФ и 4x10нФ, то получится кривая с резонансным подъемом на частотах 20-50МГц (желтая линия на графике). На частоте 35МГц импеданс параллельно включенных конденсаторов почти в 5 раз больше, чем импеданс каждого из конденсаторов по отдельности. Результат ожидаемый, поскольку в диапазоне частот между собственными резонансами конденсаторов фазы их импедансов различаются практически на 180 градусов, конденсаторы "мешают" друг другу. Эффект заметный, однако о нем совершенно не упоминается в контексте проектирования развязки питания. Это действительно не важно? Или в реальных платах вредное взаимовлияние конденсаторов как-то нивелируется?