Dootch

Свой-

Постов

90 -

Зарегистрирован

-

Посещение

Весь контент Dootch

-

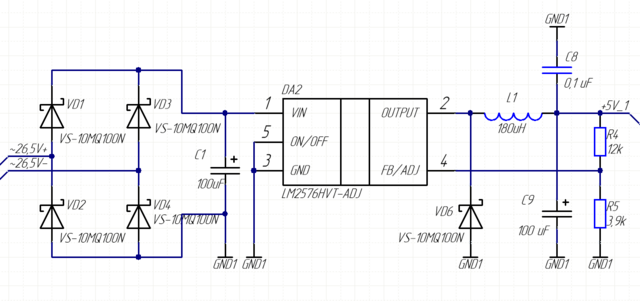

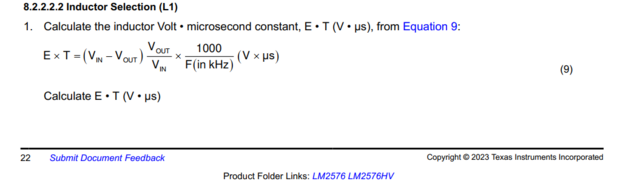

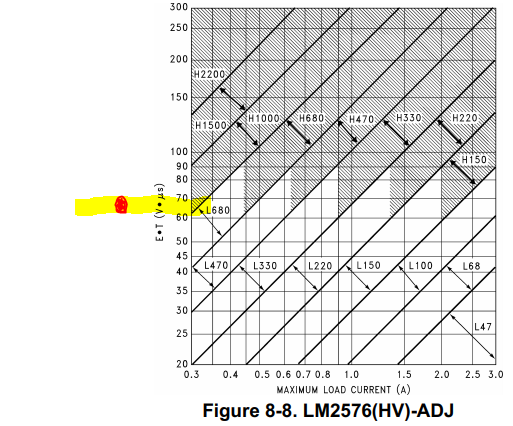

Добрый день! Имеется схема с LM2576HVT-ADJ и 5 В на выходе. LM2576HVT-ADJ выбрана из-за широкого диапазона входных напряжений. На выходе LM2576HVT-ADJ по пяти вольтам нагрузка потребляет 156 мА, то есть мощность 0,78 Вт. На входе, при этом, на напряжении 26,5 В ток составляет 46 мА, то есть мощность 1,22 Вт. КПД в этом случае получается 64%. Мне такой низкий КПД не подходит. Тем более, что производителем заявляются более высокие значения КПД. Как я понял, на КПД влияет выбор обвязки и, в частности, индуктивности. Я сделал как в дататшите от Техаса. Рассчитал E*T по формуле С учетом ожидаемого разброса входного напряжения получил значение от 64 до 69. Постарался прикинуть значение индуктивности с учетом, что выходной ток у меня будет где-то между 150 и 200 мА Получил точку вне диапазона картинки (красным), но как будто мне предлагают выбрать индуктивность из региона H1500 или H1000 (так и не понял, чем отличается H от L). Рекомендуемых даташитом катушек у меня нет, поэтому пытался импровизировать с имеющимися RLB0914 на 180 uH. Впаивал одну как на схеме - КПД 64%, впаивал 5-8 последовательно (может это не слишком корректно, но попробовал) - КПД не меняется. Вопрос: как мне повысить КПД в данном случае?

-

Добрый день! Прошу посоветовать полезные книги на русском языке по машинному обучению человеку в подарок. Кратко, человек может в Phyton и намерен вкатиться в эти ваши нейронные сети.

-

Фильтрация точечного графика

Dootch ответил Dootch тема в Алгоритмы ЦОС (DSP)

К чему тогда фраза "Не надо ничего изобретать. Надо решать задачу стандартными методами."? Если модификация того же K-mean потребует больше времени и сил чем другие методы, то я лучше поизобретаю. Или попробую предложенные тут подходы. -

Фильтрация точечного графика

Dootch ответил Dootch тема в Алгоритмы ЦОС (DSP)

Просмотрел алгоритм К-средних и даже попробовал его применить с использованием библиотеки alglib. Мне кажется в данной задаче подобный алгоритм кластеризации без глубокой модификации плохо применим. Во-первых, нам неизвестно количество центров. Во-вторых кластеризация хорошо работает с реально локализованными группами, а тут помимо явно видных кластеров, есть еще множество разбросанных по полю точек, которое в один кластер объединено не будет. -

Фильтрация точечного графика

Dootch ответил Dootch тема в Алгоритмы ЦОС (DSP)

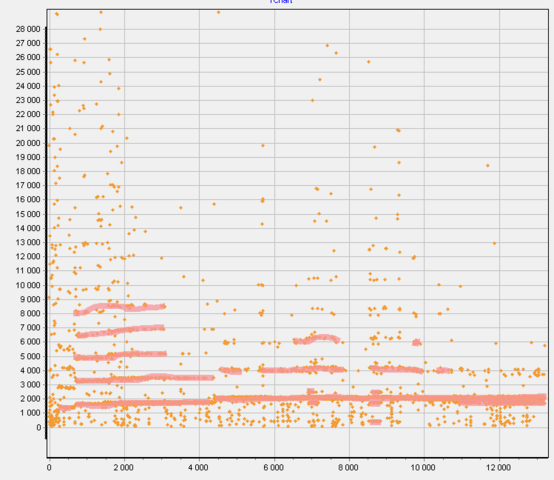

Число отсчетов примерно такое как на графике (около 13к). Анализ не нужно делать в реальном времени, есть блок данных у него нужно выявить значения этих фиксированных уровней плюс оценить их дисперсию и пометить те точки, которые лежат на этих уровнях. Собственно, точки которые лежат на этих уровнях мне нужно отбросить, это я имел ввиду под словом выделить. В результате нужно что-то вроде того как на картинке. Я пробовал отсортировать массив по возрастанию и пометить точки лежащие на "горизонтальных" участках получившегося массива. Горизонтальность оценивал по скользящей дисперсии или по наклону аппроксимирующей прямой, но как не настраивал параметры, все равно выделяется много лишних, случайных точек. -

Фильтрация точечного графика

Dootch опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день! Имеется набор данных (одномерный массив). Если построить график этого массива по точкам, то получится приложенная картинка. На графике видны полосы значений, вокруг которых концентрируются значения массива. Никак не могу придумать алгоритм выделения (фильтрации) этих полос на фоне остальных точек. Пробовал строить гистограмму и фильтровать по локальным максимумам, но она не очень эффективна если сначала идет линия, потом прерывается, а потом начинается снова. Может кто подскажет в какую сторону двигаться? -

Спасибо всем за отклик. Хочу попробовать такой вариант: AC(28..50 В, 8 кГц) => диодный мост => LM2576HVT-ADJ (выход 12 В) => два B1212S-1WR2

-

Добрый день! Имеется линия питания AC (меандр) с диапазоном амплитуд 28В..50В и частотой 8 кГц. Необходимо получить из нее два изолированных друг от друга 12В DC. Мощность потребителя 1-2 Вт. Ранее для решения этой задачи наматывался кастомный трансформатор EFD25 с двумя вторичными обмотками, которые подключались к выпрямителям и далее питали схему. Проблема в том, что хочется отказаться от ручной намотки трансформатора и использовать какое-то готовое покупное решение. На ум приходит схема: AC(28..50 В, 8 кГц) => диодный мост => два DC-DC конвертора с широким диапазоном входных напряжений (к примеру AM2GH-4812DZ). Проблема в том, что DC-DC конверторы с таким широким диапазоном входов не особо распространены и доступны в больших количествах. Особенно сейчас. Прошу предложений, каким образом кроме указанного мной можно решить такую задачу?

-

Добрый день! Хочу проверить одну возможность. Сейчас для хранения кода и данных Nios II мной используется следующая процедура: - Вектор reset процессора устанавливается на epcs_flash_controller - из elf файла создается hex - из hex и sof создается jic - jic пишется во флэшку. Можно ли как-то разместить hex файл блоке памяти ПЛИС и указать этот блок процессору? После чего просто скомпилировать и зашить pof или jic во флэшку? Надеюсь понятно объяснил. Нужно мне это для попытки реализовать многопроцессорную систему на одной микросхеме ПЛИС.

-

Объединение токовых ЦАП

Dootch ответил Dootch тема в Вопросы аналоговой техники

разве не до 18? -

Объединение токовых ЦАП

Dootch ответил Dootch тема в Вопросы аналоговой техники

Не хватает разрядности -

Объединение токовых ЦАП

Dootch опубликовал тема в Вопросы аналоговой техники

Добрый день. В нашем проекте используется 4 16-разрядных ЦАП MAX5885 с токовым выходом. Задача состоит в сложении выходных сигналов. Первая мысль состоит в том, чтобы включить выходы ЦАП как показано на рисунке 7 из даташита на MAX5885, а затем подать положительные и отрицательные дифференциальные напряжения всех цап на схему параллельного сумматора на ОУ. Рисунки приложил. Но не покидает ощущение, что токовые выходы нескольких цап можно суммировать гораздо проще. Прошу подсказать нужную схему включения. -

Как опознать клемму заземления

Dootch опубликовал тема в Компоненты

Добрый день. На старом приборе имеется клемма заземления. В принципиальной схеме на этот прибор она именуется как ЯЫЧ.835.018. Интернет по этой информации ничего не дает, поэтому прошу опознать название клеммы. Интересует именно клемма российского производства, желательно с приемкой 5. -

Синтез КВ радиосигналов

Dootch опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Стоит задача имитации сигналов радиостанции РВМ. РВМ радиостанция одновременно передает на трех частотах: 4,996 МГц, 9,996 МГц и 14,996 МГц. На первом этапе нужно синтезировать сигнал, состоящий из суммы указанных синусоидальных частот. Опорной частотой выступает эталонный высокостабильный сигнал 100 МГц. Хочу попытаться все сделать внутри FPGA. То есть на вход подаю эталонные 100 МГц через компаратор, далее в FPGA формирую нужные отсчеты для ЦАП. Основная проблема в том, что все эти частоты не кратны между собой и не кратны с опорной частотой. Также синусоидальные частоты не должны быть округленными, а формироваться из опорки. Думал решить все в лоб: то есть вычислять сумму sin(2*pi*4996000*10нс*n)+sin(2*pi*9996000*10нс*n)+sin(2*pi*14996000*10нс*n), где n - это номер периода опорной частоты, но такое выражение в FPGA будет считаться очень медленно. Возможно есть более простые методы для решения подобных задач? Если так прошу подсказать где и что искать? -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

Как я понял for at least the duration of tCFG это минимальное время, я держу low долго, секунды. Потом поднимаю nStatus сейчас не могу посмотреть пока -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

Кстати сейчас проверил в Pin Connection Guidelines для циклона 4 для nCONFIG написано: Dedicated configuration control input. Pulling this pin low during user-mode will cause the FPGA to lose its configuration data, enter a reset state, and tri-state all I/O pins. Returning this pin to a logic high level will initiate reconfiguration. а для циклона 5: Pulling this pin low during configuration and user mode causes the Cyclone V device to lose its configuration data, enter a reset state, and tri-states all the I/O pins. A high-to-low logic initiates a reconfiguration. Если тут нет опечатки, то не совсем понятно как сделать high-to-low logic если он уже в low logic установлен когда я его сбросил. -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

Подавали, ничего не меняется. -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

Да, включается,считывает конфиг из флэшки и запускается. -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

MSEL у меня подключены как 10011, то есть POR Delay : Standard -

Сброс Cyclone V

Dootch ответил Dootch тема в Работаем с ПЛИС, области применения, выбор

Читал, есть две версии 1. фраза When you use the nCONFIG pin in a passive configuration scheme, connect the pin directly to the configuration controller наводит меня на мысль что дергать ножкой nCONFIG можно только если я использую Passive configuration, а моя схема, приведенная выше с nConfig подключенной к внешнему контроллеру работать не будет. 2. фраза A high-to-low logic initiates a reconfiguration наводит на мысль, что после того как я подал на ножку ноль и FPGA сбросилась мне надо подать переход high-to-low для запуска процесса реконфигурации. И какая версия верна? -

Сброс Cyclone V

Dootch опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день, Имеется плата с Cyclone V. Конфигурация FPGA и/или EPCQ работает по схеме: Есть необходимость периодически сбрасывать FPGA внешним микроконтроллером. Для этого нога nCONFIG подключена к выводу контроллера. При установке контроллером нуля FPGA переходит в состояние сброса. Чтобы вывести из состояния сброса контроллер переводит ногу в Z-состояние, соответственно nCONFIG подтягивается к единице, но FPGA уже не выходит из сброса и не начинает реконфигурацию. В Cyclone® V Device Family Pin Connection Guidelines написано: Pulling this pin low during configuration and user mode causes the Cyclone V device to lose its configuration data, enter a reset state, and tri-states all the I/O pins. A high-to-low logic initiates a reconfiguration. Прошу объяснить где я заблуждаюсь и как мне вывести FPGA из сброса без отключения/включения питания. -

Я в начале топика для простоты указал, что сигналов два, на самом деле их 8. Прошу прощения за неточность. Идея в том, что счетчик крутится по кругу непрерывно, а из значений регистров вычисляется временной интервал между любой парой сигналов.

-

Для количества измеряемых импульсов больше двух в голову приходит только такая схема: И счетчик и регистры получают на синхронизацию один и тот же тактовый сигнал, регистры имеют вход разрешения работы на который поступает сформированный по предложенной Вами схеме edge detector сигнал, правда схема edge detector немного изменена (добавлен второй триггер перед инвертором)

-

Спасибо, а если увеличить число измеряемых импульсов до восьми? В общем случае кажется нужно прописать некий констрейн.

-

Как правильно писать в регистр

Dootch опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день. Собираю на ПЛИС Cyclone V E схему, которая измеряет разность времен прихода двух импульсов А и B. Длительность импульсов около 200 мкс, частота 1 Гц. Время измеряется в единицах опорной частоты 100 МГц, подаваемой на счетчик. Схема приведена на рисунке. Сигналы записи состояний счетчика в регистр я формирую синхронно с опорной частотой. Для того, чтобы состояние счетчика записывалось всегда корректно, как я понял необходимо указать компилятору что данные с счетчика на входе регистров должны быть стабильны к моменту прихода сигнала записи. Вопрос как это сделать? Возможно для корректной работы нужно изменить схему, но что-то никаких идей нет.