maxics

Участник-

Постов

280 -

Зарегистрирован

-

Посещение

Весь контент maxics

-

Какой ограничитель лучше поставить. Например на 6 В. Заранее благодарен.

-

Спасибо за информацию. Не знал об этом... Значит необходимо ставить отдельный стабилизатор на контроллер USB и только после того как с Хостом будет налажен контакт давать ENABLE на основной стабилизатор.

-

Планирую потреблять ~300 мА. А причем тут энумерация? Я вставляю шнурок, от USB получаю ток до 500 мА.

-

В разрабатываемой печатной плате, питание +5 В планируется брать от USB. На плате планируется установка АЦП и ПЛИС Spartan-6. На входе планируется поставить DC-DC преобразователь EN5322QI ( http://www.altera.com/devices/power/enpiri...r/en5322qi.html ) из которой буду делать 3.3 В. Данный DC-DC работает с диапазоном вх. напряжений 2.4 В - 5.5 В. В связи с этим вопросы: 1) замерял напряжение от USB на 3-х компах: 5,14; 5,11; 5,15. Хватит-ли EN5322QI, т.к. верхняя граница приближается к питанию USB? Как обезопасится от скачков напряжения? 2) В описании на EN5322QI говорится, что достаточно только одного кондера 10 мкФ на входе. Хватит-ли этого?

-

ПЛИС-Spartan 6. Требуется в прямом эфире двигать фазу DCM для подбора оптимального смещения с помощью VIO Chipscope. Планируется подавать на порт PHASE SHIFT DCM. Можно ли так сделать?

-

Управление генератором SI570

maxics опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Помогите разобраться как управлять генератором SI570. Для начала требуется прочитать данные с регистров 7 -12. В описание представлена следующая схема чтения: Slave Adress - 55h . Что есть Byte Adress? И почему в ответе 2 байта, вроде каждый регистр - 1 байт? -

ПЛИС + WIFI

maxics ответил maxics тема в Работаем с ПЛИС, области применения, выбор

Я думаю, что 802.11g- 54 Мбит/c, а 802.11n - в разы больше, не помню сколько... -

ПЛИС + WIFI

maxics ответил maxics тема в Работаем с ПЛИС, области применения, выбор

Заинтересовался этим модулем (hlk-rm04). Скорость нужна не менее 5 МБайт/с в идеале 10 МБайт/с. Реально прокачать данные с такой скоростью с помощью этого модуля. -

ПЛИС + WIFI

maxics ответил maxics тема в Работаем с ПЛИС, области применения, выбор

Никакой софт я не собираюсь перекладывать на Spartan6. Есть рабочий проект. где реализована передача данных по Ethernet 100M, пакеты UDP. Сейчас стоит задача также передавать, только по WIFI -

ПЛИС + WIFI

maxics опубликовал тема в Работаем с ПЛИС, области применения, выбор

Имеется задача передачи данных от Spartan 6 на планшет по WIFI. Скорость необходима не менее 5 Мб/с. Spartan 6 подключен к PHY ETHERNET Marvell 88e1111, протокол UDP. Скорость 100 М. Имеются-ли OEM Wifi модули, которые можно подключить к PHY ETH и осуществить дальнейшую передачу по WiFI? Кто-нибудь делал подобное? Нужно-ли будет менять протокол передачи UDP в ПЛИС или достаточно управлять модулем по UART? -

Установлен Multisim 12.0.1. Пытаюсь добавить инструмент LabView в Multisim. Например: Analog to Digital Conversion (ADC) Simple and Advanced Tools ( https://decibel.ni.com/content/docs/DOC-21222 ). Всё делаю как описано здесь: https://decibel.ni.com/content/groups/multi...ered-by-labview . Т.е в общих установках смотрю путь и кладу скачанные файлы, затем перезапускаю Multisim, но в приборах Labview ничего не вижу. При этом некоторые приборы удаётся установить, например: FIR Digital Filtering Tool ( https://decibel.ni.com/content/docs/DOC-28521 ). В чём может быть ошибка?

-

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

Понятно, спасибо всем! -

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

И всё-таки непонятно предназначение конденсатора 1 мкФ в схеме в ООС? Например, в приведенной Alexashka схеме, такового конденсатора после резистора R45 нет и, как я понимаю, работает. -

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

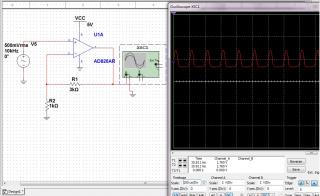

Спасибо. Есть ещё несколько вопросов: 1. Зачем нужен 1 кОм резистор с '+' входа ОУ на делитель (без него тоже работает)? 2. Зачем нужен 1 мкФ кондер на землю в ООС? Без него схема не работает. 3. Если сигнал после ОУ планируется оцифровать АЦП с Vref=2.5 В, то конденсатор на выходе ОУ ставить не нужно? -

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

Переменное напряжение 50-100 mV -

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

Необходимо будет усиливать сигналы с медицинских датчиков. -

Что неправильно в схеме?

maxics ответил maxics тема в В помощь начинающему

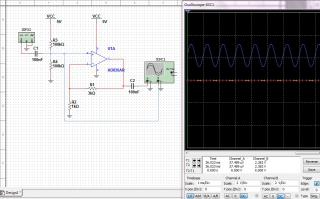

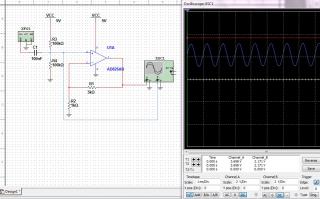

Спасибо всем окликнувшим. Согласен, не было делителя. Но теперь следующие проблемы. Прикладываю результаты с конденсатором и без на выходе. -

Что неправильно в схеме?

maxics опубликовал тема в В помощь начинающему

-

Коммутация сигналов после герконов

maxics ответил maxics тема в Вопросы аналоговой техники

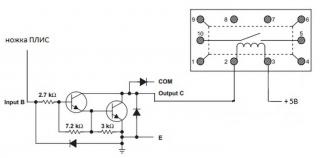

В Итоге остановились на сборке Дарлингтона ULN2003A, подключив ее к герконовому реле по следующей схеме: Когда с ножки ПЛИС подается ‘0’, то на выводе 2 геркона +5 В, соответственно ключ разомкнут, если подаем с ножки ПЛИС ‘1’, то на выводе 2 геркона +0.7 В – ключ замыкается. Проблема в помехе которая лезет в два канала одновременно: Отключаем +5В с реле(вывод 1) и видим чистый шум: Что неправильно в схеме подключения? Как исправить ситуацию? -

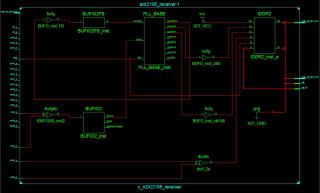

Между IDDR2 и данными никакой доп. логики нет. Это видно из схемы. Проблему решил, убрав BUFG для clk0 и clk180 между PLL и IDDR2, т.е такт завожу напрямую от PLL. После этого констрейнты стали выполняться.

-

Сделал все как было написано выше. Такт пускаю через BUFIO2 и затем на PLL, где делаю такт для IDDR. Стабильности не прибавилось. Не выполняются тайминги для констрейнтов описанных в UCF: NET "out2a_p" LOC = L3; NET "out2a_n" LOC = L1; NET "FR_p" LOC = K2; NET "FR_n" LOC = K1; NET "DCO_p" LOC = J3; NET "DCO_n" LOC = J1; NET "reset" LOC = D13; INST "x_ADC2195_receiver/ibuf_2a" IOB =TRUE; INST "x_ADC2195_receiver/IBUFGDS_inst2" IOB =TRUE; #INST "x_ADC2195_receiver/ibuf_FR" IOB =TRUE; INST "x_ADC2195_receiver/IDDR2_inst_a" IOB =TRUE; #INST "x_ADC2195_receiver/IDDR2_inst_b" IOB =TRUE; #INST "x_ADC2195_receiver/IDDR2_inst_c" IOB =TRUE; #INST "x_ADC2195_receiver/IDDR2_inst_d" IOB =TRUE; # NET "DCO_p" TNM_NET = "DCO_p"; TIMESPEC TS_DCO_p = PERIOD "DCO_p" 5 ns HIGH 50 %; #NET "x_ADC2195_receiver/DCO" TNM_NET = DCO; NET "x_ADC2195_receiver/CLK0" TNM_NET = CLK0_GRP; NET "x_ADC2195_receiver/CLK180" TNM_NET = CLK180_GRP; NET "out2a*" TNM = "out2a"; TIMEGRP "out2a" OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "DCO_p" TIMEGRP "CLK0_GRP"; TIMEGRP "out2a" OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "DCO_p" TIMEGRP "CLK180_GRP"; NET "Data_SV_out_I[0]" LOC = b20; NET "Data_SV_out_I[1]" LOC = b21; NET "Data_SV_out_I[2]" LOC = b22; NET "Data_SV_out_I[3]" LOC = d20; NET "Data_SV_out_I[4]" LOC = d21; NET "Data_SV_out_I[5]" LOC = d22; NET "Data_SV_out_I[6]" LOC = c20; NET "Data_SV_out_I[7]" LOC = c22; NET "Data_SV_out_I[8]" LOC = f20; NET "Data_SV_out_I[9]" LOC = h19; NET "Data_SV_out_I[10]" LOC = h18; NET "Data_SV_out_I[11]" LOC = e20; NET "Data_SV_out_I[12]" LOC = e22; NET "Data_SV_out_I[13]" LOC = f21; NET "Data_SV_out_I[14]" LOC = f22; NET "Data_SV_out_I[15]" LOC = h20; NET "test[0]" LOC = k16; NET "test[1]" LOC = j16; NET "test[2]" LOC = h16; NET "test[3]" LOC = h17; //////////////////////////////////////////////////// Timing constraint: TIMEGRP "out2a" OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE COMP "DCO_p" TIMEGRP CLK0_GRP; For more information, see Offset In Analysis in the Timing Closure User Guide (UG612). 2 paths analyzed, 1 endpoint analyzed, 1 failing endpoint 1 timing error detected. (1 setup error, 0 hold errors) Minimum allowable offset is 2.404ns. -------------------------------------------------------------------------------- Paths for end point x_ADC2195_receiver/IDDR2_inst_a (ILOGIC_X0Y83.D), 2 paths -------------------------------------------------------------------------------- Slack (setup path): -1.154 ns (requirement - (data path - clock path - clock arrival + uncertainty)) Source: out2a_n (PAD) Destination: x_ADC2195_receiver/IDDR2_inst_a (FF) Destination Clock: x_ADC2195_receiver/clk0 rising at 1.111ns Requirement: 1.250ns Data Path Delay: 2.975ns (Levels of Logic = 3)(Component delays alone exceeds constraint) Clock Path Delay: -0.236ns (Levels of Logic = 4) Clock Uncertainty: 0.304ns Clock Uncertainty: 0.304ns ((TSJ^2 + DJ^2)^1/2) / 2 + PE Total System Jitter (TSJ): 0.050ns Discrete Jitter (DJ): 0.132ns Phase Error (PE): 0.233ns В чем может быть причина ошибок?

-

Что есть "лапы"?

-

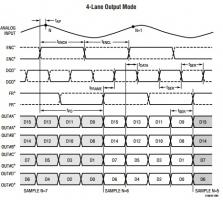

Требуется принять поток данных в SPARTAN-6 с двухканальной АЦП LTC2195. Частота 100 МГц, режим DDR 4 lane, т.е данные в АЦП приходят с частотой 200 МГц по переднему и заднему фронту. Это второй релиз платы (разводка сильно не менялась). В первом релизе, потратив много времени, удалось подобрать смещение фазы DCO (такт с АЦП) с помощью DCM (PHASE_SHIFT). В последнем релизе сделать это не удается. Видно искажение входного сигнала. Пытались подобрать фазу DCO, закреплять в PlanAhead, но безрезультатно. Бывает, что при определенном значении Phase Shift данные принимаются верно, но достаточно что-нибудь поменять в проекте, как все "уезжает". В чем может таиться ошибка? Как лучше организовать прием? Файл с исходным кодом: ADC2195_receiver.vhd

-

Решил остановится на ULN2803 (или ULN2003). Как я понимаю диод параллельно обмотке можно не ставить т.к. он есть в микросхеме. СOM подключаю к 5 В.

-

Всего 6 шт. Хотелось бы сборку поставить... Накидал схемку управления герконовым реле с помощью транзисторной сборки ULN2803. Правильно? Какой диод параллельно обмотке лучше поставить? COM напрямую подключать к GND? Хватит-ли тока ножки ПЛИС для переключения Базы?