_yes_

Участник-

Постов

22 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о _yes_

-

Звание

Участник

-

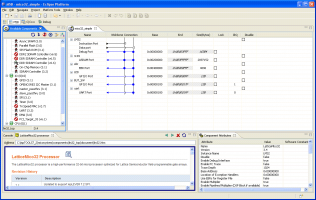

на этапе "import" EDIF в OrCAD происходит много разных ошибок и в результате некоторые цепи оказываются разорванными. может опции нужно хитрым образом ставить? я попробовал пару вариантов - результат лучше не стал --------------------------- также попробовал CAMCAD professional (4.4) - там вообще непонятно как экспортировать схему, то есть взять схему из PADS-а получается (на картинках все выглядит хорошо), а в каком формате писать? --------------------------- может вообще по-другому надо?

-

для каждого семейства есть что-то типа http://www.latticesemi.com/products/develo...uationboard.cfm http://www.latticesemi.com/products/develo...luationboar.cfm есть для "попробовать задешево" http://www.hardware-design.de/products.html купить можно все (поставщик avnet ru), но есть все-таки некие трудности из-за малой популярности у нас

-

ну а как этот микро/пикоблейз применить к АЗИКу? ну или вообще не к ксайлинсу? насколько я знаю, опенсорсные клоны микроблейза не очень хороши у латиса (вроде бы) юзать как хочешь не запрещено в лицензии btw: у латтиса есть и 8-ми битник - mico8 там защита есть и не в флашлвых семействах - защита криптованием AES-128, как в стратиксах/виртексах (и вроде Альтера что-то похожее в циклон-ls хочет сделать) а скорости в LF, особенно в 3-м (ECP3) будут повыше XP это по-моему для экономии места/быстроты запуска и т.п., защита при некриптованой внутренней прошивки, имхо, не очень серьезная

-

xp2-17 (grade -5) 66 (33x2) по синтезу (STA) до 90, на 99 не лезло - не стал упорствовать

-

это так? то есть в честном Web Edition-ском проекте NIOS будет работать пока JTAG подключен? если не так, то где-нибудь об этом подробно написано?

-

да, именно так. то есть располагаю .text .rodata .rwdata во внутренней памяти и все работает без жтага (что вобщем-то и требуется для отладки самой железяки - радиотракта и т.п.) то есть пока CFI флаш не смог пока подключить, и разбираться нет времени, пользую так. спасибо у S3 340 мегабайт он-чип памяти легко выделяется в голове мусор из-за "многостаночности", так как одновременно есть железо на ксайлинсе и латтисе впридачу, а софтпроцессор восновном LEON... если туплю с Альтерой - не сильно пинайте :) UPD: согласен со звучавшем ранее мнением - софт у Альтеры поприличнее чем у конкурентов.

-

сильно помогает verilog-mode для emacs, собственно отпарсить библиотеку v модулей и повставлять модули и соединить их - это как-раз я использую не только для тестбенчей, но и для иерархических модулей смотреть /*AUTOINST*/ /*AUTOWIRE*/ и пр. AUTO UPD: там все на lisp-e, вобще-то покруче питона язык, так сказать, концептуально мощнее :) но по-мелочи можно и поправить, у меня когда больше энтузазизма было я вставлял какие-то дополнительные фичи

-

при аккуратной работе - стер старый *.hex файл сделал билд в Nios (hex обновился) запустил компиляцию глюков нет - сразу пускает фитер из "общечеловеческих" соображений, можно было бы и ассемблером ограничится, но у фитера при изменении файла памяти процесс быстро завершается ---------------------------------------------- глюки наверно у меня - сейчас окошко выскакивает Compile Design has already .... run the task again? раньше не было

-

написал несколько скриптов на питоне - может кому-то поможет я забросил это дело, так как то что я хотел (доступ к графике) в интерфейсе PowerLogic отсутствует или я не смог разобраться, а доступ к информации типа "нетлист", который обеспечивает интерфейс, гораздо проще осуществить по текстовым файлам, которые PADS умеет экспортировать и импортировать сам ПИТОН тут http://www.python.org/download/ виндовсный интерфейс тут http://python.net/crew/skippy/win32/Downloads.html рекомендую сделать MakePy для PowerLogic, тогда будет подсказка по методам и т.п. в PytonWin (ну и быстрее должно быть) также там есть немного недокументированых фич питон позволяет в интерактивном режиме работать - имхо, может пригодится --------------------- 1) скрипты закачивающие аттрибуты в Excel, а потом выкачивающий исправленную таблицу в схему (чего-то в тырнете не нашел ничего работоспособного) закачивает _ВСЕ_ атрибуты, а не по списку, если поле в таблице пустое - значит такого атрибута у данного компонента нету 2) скрипт демонстрирующий callback из PADS-а 3) всякая мелочь: убирание неименованных $$$ цепей, чистка атрибутов, статистика и т.п. --------------------- все это скорее заготовки, смотрите код (там немного), если рискнете применить xl.rar event.rar misc.rar

-

для платки на Латтисе (не поддерживается в готовых платформах) собрал и запустил все предельно просто и вообще собирается на "ура" (для Lattice), но генератор выдает HDL код, то есть можно прикрутить к АЗИКу или какой-то ПЛИС (я правда такой не знаю), где своего софт-коре нету большой плюс - процессор в открытом виде, исправить хардкоднутую память и можно использовать где угодно шина Wishbone --------------- понравилось простотой интерфейса - SOC собирается в том же эклипсе, где код и дебагер периферии (если не считать wishbone opencores) маловато, но вобщем вариант

-

да я сам могу объяснить (наверно) - там же, типа make а файл для загрузки в память один, если два софт проекта, то могут его и не обновить а ква, наверно, если нет никаких изменений считает, что нужно весь проект переделать

-

я так понял, что это для чтения/изменения в работающем кристалле, то есть не битстрим, а по JTAG сам кристалл

-

вроде бы использует эти задержки - то есть в зависимости от констрейнов при одинаковом RTL, задержки ставит разные

-

спасибо, галка помогла но правда не несколько секунд (S3 340), но значительно быстрее, чем было :) и зависит от того как кликать(?), почему-то иногда (может когда hex не поменялся(?)) все-равно синтез запускает]

-

я так понял, что рекомендуется перекомпиляция, но вроде бы достаточно просто заменить битики в битстриме у Ксайлинса есть специалная утилита для этого, может я чего-то не понял, как для Альтеры