Aleksandr_KPI

Свой-

Постов

321 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Aleksandr_KPI

-

Звание

Местный

Контакты

-

ICQ

Array

Посетители профиля

2 410 просмотров профиля

-

Вакансия для инженера

Aleksandr_KPI опубликовал тема в Предлагаю работу

WANTED: Required Professional skills: - BSc Electronic/Electrical Engineer - mandatory - Specialized with digital signal processing - mandatory - 2-5 years experience at developing and implementation for DSP - mandatory - Skilful at C/C++ (float point) and assembler (fix point) - mandatory - Fluent in English - mandatory - Knowledge with ARM / DSP processors - advantage - Background with audio processing - advantage Personality skills: - High motivated and willing to achieve goals. - Team working coordinated - Autodidactic and self oriented person who could work independently - System structure and layers understanding - Documentation capabilities SALARY? 1,5 $ City:Kiev. All questions about vacancy: [email protected] -

Да описка у меня получилась, на выходе значение синуса (или косинуса) естественно. А на вход не совсем угол, я так понимаю там фаза задается. А насчет остального все верно. Меня интересовало, почему расчеты на бумаге не сходятся с моделью. Разобрался. Если к примеру на вход корки подать значение 520, то переводить в радианы его нужно по формуле для чисел без знака (из datasheet): theta*2*пи/2^n. Соответственно 520*2*пи/1024 = 3.13 радиан. Взять от него косинус Cos (3.13) = -0,99998. Умножить на максимальную амплитуду выходного сигнала 511*-0,99998 это приблизительно равно -511. Если выход десяти разрядный то отрицательное число -511 в двоичном коде будет 1000000001. Что совпадает и с моделью и с расчетом.

-

IP Core Sine/Cosine Look Up Table

Aleksandr_KPI опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Интересует принцип работы IP Core Sine/Cosine Look Up Table в Xilinx ISE входной порт на 10 разрядов, выходной так же 10. Общий принцип понятен, на вход модуля IP Core подаем адрес с выхода снимаем соответствующий угол. В datasheet есть формула для перехода от входного значения к углу в радианах(для чисел со знаком): theta*2*пи/2^(n-1), где theta - значение на входе, n - разрядность входного порта. К примеру подаем значение 520, ему соответствует 520*2*3,14/2^9 = 6,3835 радиан, беру косинус получаю 0,9951. Поскольку выходной порт 10-ти разрядный, то максимальное значение на выходе 511 (10 разряд знаковый). Умножаю 0,9951*511 = 508,53. С помощью Excel просчитывают по вышеизложенному алгоритму результат для значений от 511 до 535, получаю результат от 510 до 490. На выходе значения падают. Моделирую работу IP Core Sine/Cosine Look Up Table, подаю на вход значения от 511 до 535 на выходе наблюдаю медленный рост от 513 до 518. Подскажите где ошибка в алгоритме расчета? -

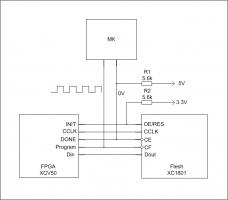

Реализован ведущий последовательный режим так как CCLK ПЛИС является выходом. Написано: Program - Initiates a configuration sequence when asserted Low. Если абстрагироваться от данного случая и рассмотреть схему из Datasheet. Правильно ли я тогда понимаю, что при логическом нуле на входе Program, очищается конфигурационная память ПЛИС, что является началом процесса конфигурации? Опишу чуть позже, сейчас в процессе осмысления.... Нигде не сказано и очевидно не нужно. Из ссылки выше: Я так понимаю у Altera nCONFIG, это у Xilinx Program, повторюсь, что же опускает в ноль линию nCONFIG? Флешь?

-

Режим : Master-Serial Mode. Входы М0, М1, М2 подтянуты к земле. Не понятно какой вариант подключения мне применить в Virtex-5 FPGA Configuration Guide, UG191.pdf (второй на рисунке) или тот который в XC18V00 Series In-System-Programmable Configuration PROMs (первый на рисунке) Загрузкой ПЛИС управляет микроконтроллер, пока он видит Done = 0 (ПЛИС не загружена), он посылает по Program меандр таким образом постоянно инициализируя загрузку ПЛИС. Вопрос: почему на Done не появляется единица? В принципе предполагаю что проблема не в подключении ( другая плата с подобной схемой включением работает нормально), наверное скрытый производственный дефект. Всем спасибо кто откликнулся.

-

Не уверен, по datasheet подтяжка нужна только на Reset. Да, пару раз наблюдал эффект: ПЛИС загружалась когда щупом касался контакта Program. Его обследовал - никаких дефектов. Сейчас больше так не получается.

-

Загрузка ПЛИС

Aleksandr_KPI опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Подскажите где еще искать причину неисправности при загрузке ПЛИС. На рисунке изобразил схему соединений для ПЛИС, МК, флешки. Должно работать так: МК анализирует сигнал Done c ПЛИС, если он "0" выдает сигнал загрузки Program (нулевой импульс). Схема зависает на процессе: Done всегда ноль, Program - меандр. Проверил: входную частоту для ПЛИС, питание ПЛИС, питание флешки, сигнал CCLK флеш все есть, на Dout флешки наблюдаю постоянный поток импульсов-данных, переменный сигнал на OE/RES. Все прозвонил и просмотрел под микроскопом, должно работать. Заранее благодарю за советы. -

Всем спасибо за ответы, микроконтроллер запрограммирован. Схема действительно не рассчитана на ISP программатор. Такую схему вижу впервые, привык к использованию кварца, но она работает, частота там порядка 10 МГц.

-

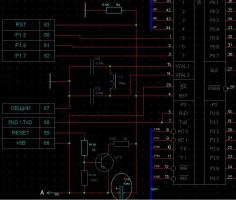

Так при такой схеме его не возможно запрограммировать, выдает ошибку: The RESET line(s) appear to be short-circued.... Выходит схема не правильна?

-

Есть подтяжка к земле через резистор на 15 кОм. Пользуюсь тем что есть. Проблема решилась, убрал конденсатор С14 (желтым). Он "съедал" положительный импульс на входе RST программатора. Я так понимаю тут пытались реализовать схему сброса МК при включении питания? А зачем это нада, разве простого передергивания питания не достаточно?

-

Программатор AVRISP MKII

Aleksandr_KPI опубликовал тема в MCS51, AVR, PIC, STM8, 8bit

Здравствуйте, подскажите в чем может быть проблема. Подключаю программатор AVRISP MKII к AT89S52. В AVR Studio (Version 4.18 build 700) пишет ошибку: There seems to be short circuit on the ISP connector. The RESET line(s) appear to be short-circued. The operation will be aborted. Проверил пин Reset, на землю он не закорочен, но потенциал на нем нулевой. Мигает красный светодиод. Заранее благодарю за ответы. -

ЦАП в ПЛИС

Aleksandr_KPI ответил Aleksandr_KPI тема в Языки проектирования на ПЛИС (FPGA)

А чем плох, модулятор для ЦАП на ПЛИС: ‘timescale 100 ps / 10 ps ‘define MSBI 7 // Most significant Bit of DAC input //This is a Delta-Sigma Digital to Analog Converter module dac(DACout, DACin, Clk, Reset); output DACout; // This is the average output that feeds low pass filter reg DACout; // for optimum performance, ensure that this ff is in IOB input [‘MSBI:0] DACin; // DAC input (excess 2**MSBI) input Clk; input Reset; reg [‘MSBI+2:0] DeltaAdder; // Output of Delta adder reg [‘MSBI+2:0] SigmaAdder; // Output of Sigma adder reg [‘MSBI+2:0] SigmaLatch; // Latches output of Sigma adder reg [‘MSBI+2:0] DeltaB; // B input of Delta adder always @(SigmaLatch) DeltaB = {SigmaLatch[‘MSBI+2], SigmaLatch[‘MSBI+2]} << (‘MSBI+1); always @(DACin or DeltaB) DeltaAdder = DACin + DeltaB; always @(DeltaAdder or SigmaLatch) SigmaAdder = DeltaAdder + SigmaLatch; always @(posedge Clk or posedge Reset) begin if(Reset) begin SigmaLatch <= #1 1’bl << (‘MSBI+1); DACout <= #1 1‘b0; end else begin SigmaLatch <== #1 SigmaAdder; DACout <= #1 SigmaLatch[‘MSBI+2]; end end endmodule Получить по DACout ШИМ последовательность и ее уже не фильтр. -

ЦАП в ПЛИС

Aleksandr_KPI ответил Aleksandr_KPI тема в Языки проектирования на ПЛИС (FPGA)

С Altera не работал, но на Xilinx можно, используя IP-Core осцилятор, сгенерировать 40 МГЦ, а дальше с помощью xapp154 Synthesizable Delta-Sigma DAC. -

ЦАП в ПЛИС

Aleksandr_KPI ответил Aleksandr_KPI тема в Языки проектирования на ПЛИС (FPGA)

Спасибо. Нашел вот описание на него. Как бы обозвать сам код на Verilog, ШИМ конвертор? Тут нашел интересную информацию по данному поводу. Цап-ом называется конструкция код+фильтр. -

ЦАП в ПЛИС

Aleksandr_KPI ответил Aleksandr_KPI тема в Языки проектирования на ПЛИС (FPGA)

Всем спасибо за ответы ))). Возникли вопросы. К примеру я имею ряд чисел выдаваемых генератором, по каждому такту опорной частоты (CLK) : 512, 512, 537, 537, 562, 562, 587, 587 ...., числа имеют диапазон от 1 до 1023. 1) Если суммировать числа по CLK, то какой величины должен быть аккумулятор? 2) Как выбирается его разрядность? 3) При переполнении двоичного аккумулятора на выходе появляется единица, а как быть с остатком. К примеру десяти разрядный аккумулятор переполнился значением: 11001001011, что дальше? Его обнулить или добавлять следующий число к 1001001011.