svalery

Участник-

Постов

59 -

Зарегистрирован

-

Посещение

Весь контент svalery

-

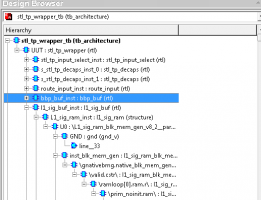

Active hdl 10.1

svalery ответил svalery тема в Среды разработки - обсуждаем САПРы

Похоже проблема в "вылеченной" лицензии. Есть у кого рабочая таблетка для этой версии (или 10.4) ? -

Active hdl 10.1

svalery опубликовал тема в Среды разработки - обсуждаем САПРы

Поставил ActiveHDL 10.1 не пойму что с Design Browser изменилось. Если симуляция не запущена -всё ок, вижу иерархию. Если сделать asim, иерархия пропадает. -

Как то можно обнаружить такое "плохое" соединение автоматически?

-

Всем спасибо за ответы. Заложено именно 0.25, тк это как раз подходит для 2х трасс по 0.1 между виа.

-

Есть такой параметр - расстояние от отверстия до меди во внутренних слоях. В pcbtech он 0.2 (http://www.pcbtech.ru/pages/view_page/94), где то видел 0.35. Какого значения стоит придерживаться, так что бы не переплатить на производстве ? BGA с шагом 1мм, хотелось бы протянуть 2 трассы 0.1 между via без использования глухих отверстий.

-

Layer stackup

svalery опубликовал тема в Изготовление ПП - PCB manufacturing

Практикуется ли запрос у производителя информации по готовому стакапу (толщина слоев, материал, параметры трасс под различные волновые сопротивления - для заданного кол-ва слоев)? Предполагаю что производителю будет удобнее дать правильный вариант, что бы не разворачивать проекты по тому что заказчик "намучал" там своих художеств которые нельзя сделать на производстве. -

Да, задача именно в этом и была, нужно выровнять ДДР без учёта терминации. Всё решилось установкой 16го альтиума (в 14м xsignals нет) и переходом на xsignals. Спасибо за наводку.

-

Altium: Interactive length tuning

svalery опубликовал тема в Altium Designer, DXP, Protel

Есть шина, каждый бит которой идёт по следующему пути : Pad1 -> Via -> Pad2 Нужно выравнять длины Pad1->Via, БЕЗ учёта отрезка Via -> Pad2. Проблема в том, что учитывается длина ВСЕЙ сети. Как это правильно сделать? Можно конечно развести Via -> Pad2 после выравнивания длин. Но кажется что должен быть другой вариант. -

Где компонент ?

svalery ответил svalery тема в Altium Designer, DXP, Protel

Вопрос в том как я мог это туда утащить если курсором туда не попасть ? Кстати компоненты (именно компоненты а не via) у меня часто туда проваливаются по непонятным причинам, причём по несколько штук сразу. Замечаю это после апдейта со схематика. Грешу на какой то глюк с алдеком. -

Где компонент ?

svalery ответил svalery тема в Altium Designer, DXP, Protel

Выделяю Outside Area , проверяю через F11 (PCB inspector) - ничего нет, то есть ничего не выделяется. Помог PCBLIST и сортировка по координатам, этот улетевший компоненты был Via ). Вообщем проблема решена всем спасибо за советы. -

Где компонент ?

svalery ответил svalery тема в Altium Designer, DXP, Protel

Edit->Select-> Outside area : выделяем всё что видим, то что за пределами должно быть Select Tools -> Component Placement -> Arrange Within Rectangle : ничего не происходит... видимо компонент НЕ выделился Проделывал то же самое но с компонентами в области видимости - всё работает как надо и Select и Placement in Rectangle. С "провалившимся" компонентом же - не работает. Что делаю не так ? -

Где компонент ?

svalery ответил svalery тема в Altium Designer, DXP, Protel

Забыл дописать - допустим я не знаю что это за компонент. Как спуститься за Y<0 и вытянуть его ? -

Где компонент ?

svalery опубликовал тема в Altium Designer, DXP, Protel

Бывает улетают компоненты за пределы PCB (в минус Y !!). Как его по нормальному его доставать оттуда? -

Вопросы начинающих 2015г

svalery ответил Uladzimir тема в Altium Designer, DXP, Protel

Делаю дифпару- обзываю (_P, _N), вешаю Place -> Derectives. При Update PCB Document вываливает ошибку: Net(s) Not Found in Differential Pair ETH1_MD1 : Positive Net [ETH1_MD1_P] & Negative Net [ETH1_MD1_N] in current PCB document Подскажите что не так делаю ? -

Altium PDF export

svalery опубликовал тема в Altium Designer, DXP, Protel

Вопрос по экспорту Altium Schematic в PDF и ссылки между страницами. Как сделать что бы в PDF по клику на порт - переходило на другой лист с которым он связан. Так же по клику на Sheet Symbol переходило на страницу с реализацией. Грубо говоря что бы была навигация в PDF похожая на ту, что в самой оболочке альтиума. -

Может перенос строки в конце "endpackage : definitions" поставить/убрать ?

-

Aldec 9.3 тормоза

svalery ответил svalery тема в Среды разработки - обсуждаем САПРы

Можно подробнее что именно отсутствовало в bin и какие косяки с лицензией. Может в моём случае тоже самое. Спасибо! -

Aldec 9.3 тормоза

svalery ответил svalery тема в Среды разработки - обсуждаем САПРы

Ничего особенного не используется. Причина перехода - либы, ну и ожидал прироста проиводительности, как ни как - новый тул. Придётся откатываться на 9.1 и компилить либы вручную. Удивляет криворукость разработчиков Aldec, где можно было так налажать? Сравнили 9.1, 9.2, 9.3. 9.2 тормознее чем 9.1; 9.3 до ужаса тормознее чем 9.1 и 9.2. -

2014.1, Clocking wizard 5.1 - вроде запускается, генерится.

-

Aldec 9.3 тормоза

svalery ответил svalery тема в Среды разработки - обсуждаем САПРы

Когда сигналов немного - не заметно. Но если их к примеру около 100 (1 -16 бит), то 9.1 сильно не замечает, тогда как 9.3 ложится на прочь. -

Aldec 9.3 тормоза

svalery ответил svalery тема в Среды разработки - обсуждаем САПРы

Достаточно наглядное сравнение 9.1 и 9.3 - открываем отсимулированный вейформ, и крутим быстро зумом (колесом мыши). 9.1 - успевает отрабатывать и диаграмки гармошкой увеличиваются и уменьшаются в реальном времени. 9.3 они тупо стоят на месте (не успевает отрабатывать). Тут как будто что то с гуи разработчики натворили. -

Aldec 9.3 тормоза

svalery опубликовал тема в Среды разработки - обсуждаем САПРы

Хочу поинтересоваться у одного меня одного так или как с этим бороться. Был 9.1 - всё летало (до сих пор стоит и всё гуд). С недавнего времени пришлось поставить 9.3. В итоге на пустом коде с момента нажатия F11 до конца компиляции проходит до 10 сек. Навигация по вейформам - тихий ужас: отработка зума опять же несколько секунд на каждый +/-, перемотка - слайдшоу. Симуляция , рестарт и тд - как будто алдек кто то за "задницу держит". Кто наблюдал такое ? -

Vivado ++ DDR3

svalery ответил svalery тема в Работаем с ПЛИС, области применения, выбор

Видимо проблема в распиновке(пытаюсь запихать 2 контроллера в HP банки 32,33,34 (XC7K410T-1FBG900) ). Если оставить распиновку автоматом - компиляция проходит. Странно что Validate в визарде на мою распиновку не ругается, возможно проверяется только валидность по одному контроллеру, а не по совместимости распиновки между обоими. -

Vivado ++ DDR3

svalery опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет. Хочу обратиться за советом по проблеме. Имеем Kintex7 и 2 чипа DDR3. В чистый проект запиливаю 2 контроллера на каждый чип (mig корка позволяет указывать в одном визарде параметры сразу для 2х контроллеров). В итоге при использовании example дизайна в качестве основы компиляция выдаёт следующее: Критикал варнинги: Implementation Design Initialization [Vivado 12-2285] Cannot set LOC property of instance 'example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c1_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phy_control_i', Instance example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c1_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phy_control_i can not be placed in PHY_CONTROL of site PHY_CONTROL_X1Y1 because the bel is occupied by example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c0_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_1.u_ddr_phy_4lanes/phy_control_i. This could be caused by bel constraint conflict ["d:/Work/prj/XT_modulator/FPGA/XTM_3/xtm.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/constraints/mig_7series_0.xdc":645] [Vivado 12-2285] Cannot set LOC property of instance 'example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c1_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phaser_ref_i', Instance example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c1_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phaser_ref_i can not be placed in PHASER_REF of site PHASER_REF_X1Y1 because the bel is occupied by example_top_ddr3_inst/u_mig_7series_0/u_mig_7series_0_mig/c0_u_memc_ui_top_std/mem_intfc0/ddr_phy_top0/u_ddr_mc_phy_wrapper/u_ddr_mc_phy/ddr_phy_4lanes_1.u_ddr_phy_4lanes/phaser_ref_i. This could be caused by bel constraint conflict ["d:/Work/prj/XT_modulator/FPGA/XTM_3/xtm.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/constraints/mig_7series_0.xdc":648] Фолты: Place Design [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phaser_in_gen.phaser_in' [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phaser_out' [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phaser_in_gen.phaser_in' [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phaser_out' [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phaser_ref_i' [Place 30-370] An unconstrained Phaser instance has been found. Phaser instances and their associated IO logic must be LOC constrained to a legal site locations for placement to succeed. Check to see whether all core constraints were properly used or manually add LOC constraints for the following instance(s). Unconstrained Phaser instance(s): Inst 'phy_control_i' [Place 30-99] Placer failed with error: 'Implementation Feasibility check failed, Please see the previously displayed individual error or warning messages for more details.' Please review all ERROR, CRITICAL WARNING, and WARNING messages during placement to understand the cause for failure. [Common 17-69] Command failed: Placer could not place all instances По фолтам видно что есть незаконстрейненые компоненты, хотя в xdc они указаны. XDC судя по 1м варнингам - находит и использует его. Возможно что фолты - следствие ошибки указанной в варнингах. Варниги выдаёт не спроста, если посмотреть в XDC (сгенерённый визардом, то есть руками я его не трогал) то там явно видно что один и тот же ресурс назначается 2 раза для каждого из контроллеров: для 1го set_property LOC PHY_CONTROL_X1Y1 [get_cells -hier -filter {NAME =~ */c0_u_memc_ui_top_std/*/ddr_phy_4lanes_1.u_ddr_phy_4lanes/phy_control_i}] set_property LOC PHY_CONTROL_X1Y2 [get_cells -hier -filter {NAME =~ */c0_u_memc_ui_top_std/*/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phy_control_i}] и для 2го set_property LOC PHY_CONTROL_X1Y0 [get_cells -hier -filter {NAME =~ */c1_u_memc_ui_top_std/*/ddr_phy_4lanes_1.u_ddr_phy_4lanes/phy_control_i}] set_property LOC PHY_CONTROL_X1Y1 [get_cells -hier -filter {NAME =~ */c1_u_memc_ui_top_std/*/ddr_phy_4lanes_0.u_ddr_phy_4lanes/phy_control_i}] То есть PHY_CONTROL_X1Y1 юзается 2 раза на что и указывает 1й варнинг (2й также но на PHASER_REF_X1Y1) Были ли у кого такие проблемы и как их решать ? Пробовал генерить отдельно для каждого чипа (для каждой группы пинов) 2 проекта, всё так же как и в смежном - используется один и тот же PHY_CONTROL_X1Y1 и PHASER_REF_X1Y1 -

Сравнить два цифровых сигнала

svalery ответил Oleg_Viktorovich тема в Алгоритмы ЦОС (DSP)

conv( a , b )