masha_belka

Участник-

Постов

49 -

Зарегистрирован

-

Посещение

Весь контент masha_belka

-

а можно ссылку на документ, где написано так?

-

диф. пара 150 Ом или один проводник 75 Ом

masha_belka опубликовал тема в Работаем с трассировкой

Здравствуйте, подскажите с разводкой трансформатора T-1062SCT для канала Fiber Channel. Есть документация одна http://productfinder.pulseeng.com/products...sheets/M105.pdf где ничего не сказано и другая http://datasheet4u.com/download.php?id=602499 на которой показано что передающие линии 75 Ом, Эти сигналы используются для кабеля с волновым сопротивлением 150 Ом. В документации на Altera(сигналы с трансформатора идут на микросхему семейства EP4CGX30) нет не одного слово про 75 Ом, зато сказано про 150 Ом в диф. паре. Может кто знает или уже сталкивался, как провести сигналы диф. парой 150 Ом или одиночным в 75 Ом? -

Вопросы начинающих

masha_belka ответил KA_ru тема в Altium Designer, DXP, Protel

Подскажите пожайлуста как записать плавило для выравнивания суммы двух проводников? чтоб выравнивать Автоматически через Interactive Length. до этого делали ручками, считали сумму двух проводников и выравнивали тоже ручками. -

гибко-жесткая ПП

masha_belka ответил masha_belka тема в Работаем с трассировкой

Извините, только увидела, можно я вам завтра позвоню. -

гибко-жесткая ПП

masha_belka ответил masha_belka тема в Работаем с трассировкой

Хорошо, диф. пары в лицевых слоях и экран между (т.е 3слоя). Но нужен хотя бы еще один слой для других сигналов. Как это сделать, я не могу понять? Склеить 3 слоя и отдельно один через воздушную прослойку. -

гибко-жесткая ПП

masha_belka ответил masha_belka тема в Работаем с трассировкой

в сумме 60 пар -

гибко-жесткая ПП

masha_belka ответил masha_belka тема в Работаем с трассировкой

Диф пар в каждом слой около 30, с экранированием с двух сторон. Но разработчик разрешил уменьшить число слоев до 2, т.е в гибкой части всего 6 слоев. Сконструкцией все сложней, длина и радиус не меняются. -

гибко-жесткая ПП

masha_belka ответил masha_belka тема в Работаем с трассировкой

Да, конечно можно. Радиус изгиба 20. Через гибкую часть проходят 3 слоя диф. пар с волновым сопротивлением 100 Ом. -

гибко-жесткая ПП

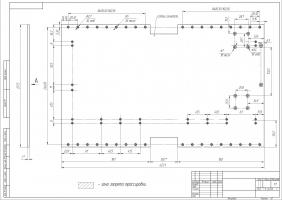

masha_belka опубликовал тема в Работаем с трассировкой

Прошу помощи знающих людей, задали с проектировать ГЖПП, это мой первый опыт в ГЖПП. Прочла статьи (http://www.pcbtech.ru/pages/downloads/200 , http://www.pcbtech.ru/pages/downloads/202, http://www.pcbtech.ru/pages/downloads/203) и возникли не которые вопросы: Какую сделать конструкцию гибко-жесткой ПП, если нужно 3 сигнальных слоя с диф. парами и к ним экраны в гибкой части платы? -

Вопросы начинающих

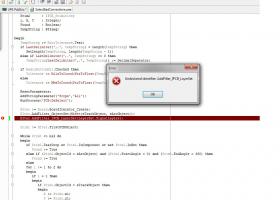

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Владимир, подскажите, скрипт запускаю, он не работает. 1. Этот скрипт для Altium Summer 09? или для 10? 2. а вот сама ошибка, которую я не понимаю см.рисунок 3. и как избежать в дальнейших платах этой ошибки(не доводит до центра проводник)? -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

можно подробнее, где этот скрипт -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

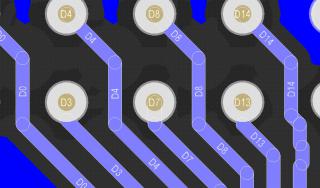

Помогите, разводка платы сделана, ошибки на ширину проходит(ширина провода 0,1мм) Глазами видно что соединение плохое D3(см. рисунок) Как это поймать автоматически, не глазами??? -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

снимите галку в preferences- schematic-graphical editing- Mark manual parameters -

Работа с полигонами

masha_belka ответил masha_belka тема в Altium Designer, DXP, Protel

Direct connect применять нельзя к паяльным элементам, получается только ручками править??? -

Работа с полигонами

masha_belka ответил masha_belka тема в Altium Designer, DXP, Protel

Меняю настройки не помогает, ставлю значение Remove Necks when Copper widht less than = 0,15мм, он все равно подводит полигон проводниками толщиной меньшей чем стоит в условии. Может я что-то не то делаю? или еще где нибудь надо настроить? -

Работа с полигонами

masha_belka ответил masha_belka тема в Altium Designer, DXP, Protel

Где в настройках??? -

Работа с полигонами

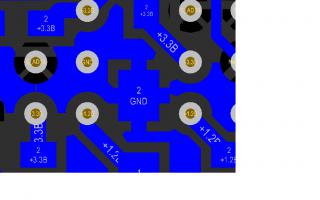

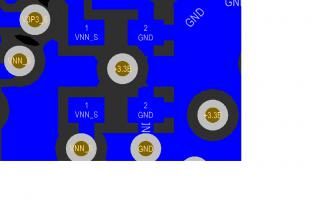

masha_belka опубликовал тема в Altium Designer, DXP, Protel

Есть плата, залитая полигоном по правилу от всего 0,2мм. В узких местах подводка к контактным площадкам ПЛОХАЯ (см. рисунки). Как этого избежать, только не в ручную, т.к этих мест много, все не углядишь. -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Спасибо помогло, только заработало с условием isPoly -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Владимир, если убираем условие комнаты из правил, то правило работает, как добавили НЕТ. А нужно чтоб это условие работало только на этой контактной площадке. Меняла размер комнаты, и это не помогло. -

Вопросы начинающих

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Помогите пожайлуста, надо залить полигон земли, со сплошным соединением, написала правило как на картинке, все равно не работает. как быть? это вообще возможно в Альтиуме? -

Как в Altium сделать...

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

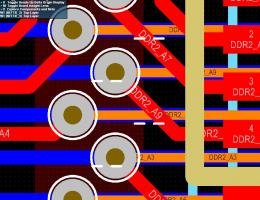

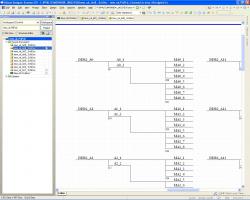

Использую элемент Tie Net для выравнивания DDR2. Элемент Tie Net создан по статье Владимира Пранович, 3 планарных площадки диаметр 0,45 и переходное отверстие 0,2/0,45. Вопрос: 1. В файле платы вижу в свойствах элемента Nie Net только площадки и не вижу переходное отверстие. Разношу площадки на 3 внутренних слоя. Пытаюсь на верхнем слое Top, подсоединить резисторную сборку. При проверке на ошибки вижу антенну, т.к. площадки фактически нет на лицевом слое, но если переходное стоит в паттерне значит площадка на лицевом слое должна быть? 2. Переделала Tie Net (4 площадки + переходное отверстие), одну площадку оставила на Top под резисторную сборку. Проверила на ошибки, получила не разведенную связь, т.к связь на TOP и на одном из внутренних имеет одно имя. Получается что фактически нет соединения через переходное отверстие, которое заложено в элемент Tie Net , между лицевым и внутренним слоем. -

Как в Altium сделать...

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Подскажите пожайлуста, вся шелкография написана шрифтом Stroke - Sans Serife высота 1,5мм, толщина 0,15. По сравнению с P-cad(настройки шрифта одинаковые) смотрится шрифт Altium'а намного больше и шире. Площади выделенной под шелкографию не хватает. Каким вы шрифтом пишите шелкографию? или как этот шрифт сделать компактнее? -

Как в Altium сделать...

masha_belka ответил Uladzimir тема в Altium Designer, DXP, Protel

Подскажите что это за белая сетка на проводниках? и как ее убрать? __________.bmp -

Владимир, а можно по подробнее про пункт 1 и 2. Или подскажите где почитать про них.

-