En_Serg

Свой-

Постов

84 -

Зарегистрирован

-

Посещение

Весь контент En_Serg

-

Настройка LVDS на Cyclone V

En_Serg ответил Петр Юркевич тема в Программирование

прошу прощения, найдите Pin Planner, скажите что у вас стандарт LVDS на выбранных пинах по входу, может полегчает? На приемном конце LVDS как можно ближе должен стоять 100 ом (обычно 0402), программа про него знать не знает (если LVDS, значит должен стоять), внутреннего такого нет. И еще конечно сигналы должны быть разведены дифференциальными парами. Информация про дифф пары - в PIn Planner слева пиктограммы вертикальные -

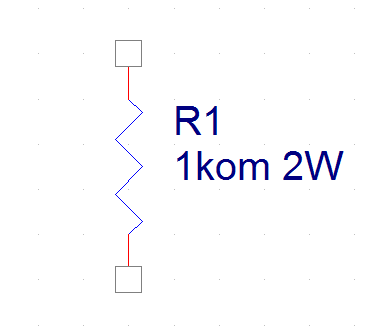

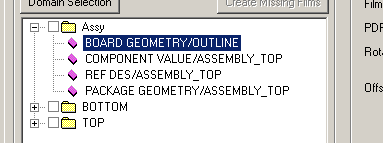

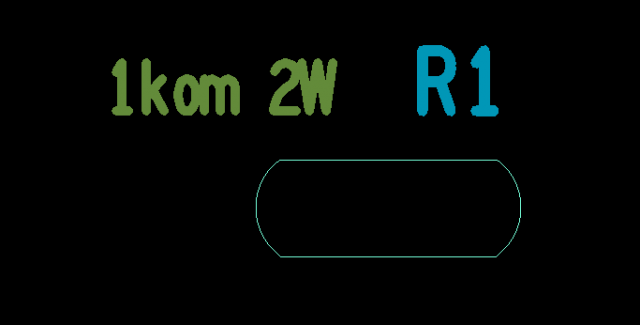

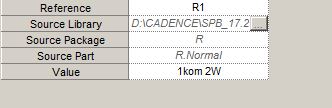

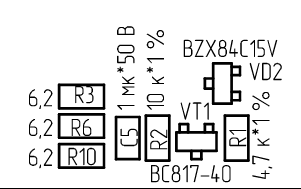

Спасибо, помогло. Действительно, если у резистора на схеме заполнить Value например вот таким 1kom 2W то на схеме будет отображаться Далее импорт элемента на плату и Manufacture/Artwork Затем при создании гербера ASSY зададим такие слои Видно, что в ASSY попал COMPONENT VALUE/ASSEMBLY TOP Соответственно, смотрим что получилось на сборке То, что хотели

-

Интересует, есть ли возможность, чтобы на гербере сборки появились надписи из схемы, типа 1мк*50в смотрим на то, что должно получаться Спасибо.

-

добрый день. Интересует, к какому блоку подключить IBIS модель ds90lv012 LVDS- приемника в программе Keysight ADS Shematic И вообще, тема целостности сигналов, она здесь или в другом месте?

-

Смотрю на плату Xilinx ZCU208. Вижу там QSFP. Это design reuse modules (.mdd). Это если бы я сам делал, сделал бы PLACE REPLICATE CREATE, получился бы QSFP.mdd Вопрос: Есть ли возможность уже сделанный кем-то .mdd записать себе на диск? Спасибо.

-

17.4

En_Serg ответил KAlexander тема в Cadence

Установил 17.4QIR1 (HF007). Все стало темным в PCB Designer. Как вернуть старую серую тему всех окон? Хочется все-таки надписи меню были черным по-белому(серому) а не наоборот (белым по черному). Спасибо. -

Спасибо. Птички не стояли на FAB -> L9...L12 в настройках

-

Добрый день. Может кто подскажет, плата PCB, разведена в Xpedition с 12 слоями L1..L12 (c 4 слоями GND) при конвертации в ODB++ теряет последние 4 нижних слоя (L9..L12) и предстает 8-слойной в CAM350 Причем слои маски, шелкографии, монтажа на BOT присутствуют. Весьма неприятная неожиданность. В чем закавыка, копать где? Спасибо.

-

Спасибо, помогло

-

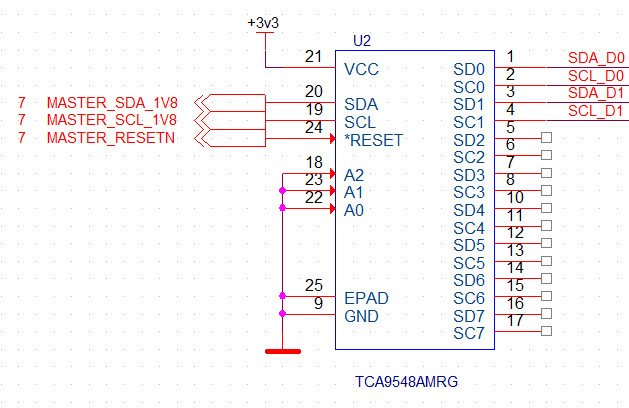

Добрый день. Подскажите, pls, что случилось с резинками неразведенных еще цепей Смотрим, видим резинка RATSNEST MASTER_SDA_1V8 превратилась в квадратик, имеет статуc UNPLANNED Вторая рядом, такая же MASTER_SCL_1V8 так не сделала, обычная резинка. Цепи эти - обычные переходные с листа на другой лист Что за напасть такая, как резинке вернуть обычный вид? (не UNPLANNED) Это в Capture или на плате беда? Спаибо.

-

Добрый день. В 17.2 появилась возможность в Capture CIS иметь Constaraint Manager. И в PCB Designer он тоже есть, но другой (а может и не другой). Подскажите, plz, как происходит передача, например статической фазы дифф пары из схемы в PCB? И, наооборот, как например в схему попадает дифф пара, заданная из PCB? Где то спряталась синхронизация этих двух Constraint Manager туда и обратно. Спасибо.

-

Хотелось бы Вашу библиотеку сконвертировать в PCAD?

En_Serg опубликовал тема в Эремекс, Delta Design

Хотелось бы Вашу прекрасную библиотеку сконвертировать в PCAD (Altium). Нет ли способа? Импорт же есть из PCAD. Это дало бы многим людям возможность на платах применять компоненты "Электродеталь" там, например. Спасибо. -

спасибо, не использовал пока

-

Добрый день. Сегодня смотрел вебинар по Altium по поводу двух полезных команд (начиная с версии 20) 1. GLOSS - это когда помечаешь дорожку или дифф пару или группу, Route-Gloss и проводники перепрокладываются без лишних изгибов по кратчайшему пути, выглядит красивее. Есть ли в Allegro такая мощная команда ?? 2. RETRACE - это если, например, для дифф пары поменялись констрейнты, и теперь надо по той же дороге перепровести дифф пару с другими толщинами. Есть ли в Allegro такая команда ?? Спасибо.

-

Добрый день. Я вижу, что размер моего файла .BRD увеличивается, когда я добавляю STEP-модель к footprint. Вопрос: Содержатся ли в BRD все STEPы и, если да, может ли другой человек, имея BRD, вытащить оттуда STEP?

-

Да вот не запоминается, все время надо папку allegro выбирать, а это уже не пара движений

-

Добрый день. Можно как-то автоматизировать команду в PCB Editor ЗАГРУЗИТЬ НЕТЛИСТ ИЗ ЗАДАННОЙ ДИРЕКТОРИИ из Capture и присвоить ее пиктограмме или на кнопку клавиатуры положить ? Может скрипт какой надо написать и выполнять его? Спасибо.

-

Организаторам -респект. На семинаре упоминалась книга. Смотрим ссылку. mitzner2.RAR

-

Ok, спасибо

-

Пытаюсь сделать свою плату с Lattice iCE40UP5K- SG48. Разбираюсь как устроена отладочная плата iCE40_ULTRAPLUS_BREAKOUT_02-11-2016. Возник вопрос: - поскольку iCE40UP5K - это SRAM-based FPGA + one-time programmable NVCM (Non-volatile Configuration Memory) , то на плате есть еще FLASH SPI N25Q032A13ESC40F для загрузки из нее FPGA. У FPGA - тоже 2 режима загрузки (Master b Slave SPI). Вопрос вот в чем: - можно ли программатором просто в SRAM FPGA записывать прошивку для отладки (понятно, что прошивка потеряется при сбросе питания); - можно ли потом готовую прошивку тем же программатором в SPI FLASH записать и кнопку питания выкл/вкл, чтобы прошивка из SPI загрузилась? Или надо какой-то джампер все время переключать? - как потом тем же программатором в однократную память совсем готовую прошивку записать? И что сделать, чтобы FPGA из нее (NVCM ) грузилось , а не из SPI Flash? Наверное, люди работали с этой микросхемой, подскажут Спасибо.

-

Спасибо. Поставил Hmin=Hmax=0. Помогло.

-

Всю голову сломал. Цилиндры все время появляются. Может кто умеет показать их в STEP? Спасибо.

-

На C_V два NOIS?

En_Serg опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Надо сделать на Cyclone V систему с двумя NIOSами. Н одном - ethernet, на другом - GPS протокол Подскажите, plz, где что почитать, надо понять как у них данные становятся общими, и как стартует такая система. Откуда ELF грузятся. И как адресуется все. Спасибо. -

Сам нашел, смотри pdf Всем спасибо, тема закрыта stack_2260.pdf

-

Надо сделать заглушку на плате SATA M.2 ngff 2260. Проверяем коммуникацию в железе. RX -> TX . Подскажите стек для 4-слойной платы и общую толщину ПП, чтобы в разъем входила. Все-таки SATA, должно работать. Спасибо.