dimone

Участник-

Постов

117 -

Зарегистрирован

-

Посещение

Весь контент dimone

-

-не , лишь самописный колхозить, самые ходовые USBD варианты либо СDC-эмуляция СОМ-порта, -либо MSC накопител, на который просто кидают прошивку..

-

Это не тот Федот. Диапазоны ,как было упомянуто для 96-bit chip ID То что вы советуете (DEV_ID) абсолютно идентично у STM32F103 и АРМ32 и GD32, поле REV_ID лишь у GD свое

-

Позвольте не согласиться, форкать один и тот-же функционал из-за девиаций чип на той-же 6орде не идея не очень, как по мне. Да и сервис проклянет.. В крайнем случае в меню пункт можно добавть, но хтелось бы сделать красиво) Да, но где найти диапазоны.. -Приглянулся вариант чтения Для STM32F103: OTG_FS core ID register (OTG_FS_CID) Reset value:0x0000 1200 Для GD32 : Core ID register (USBFS_CID) Reset value: 0x0000 1000 Правда чтения по адресу: USB_BASE + не приводит к жлаемому результату, более того регистр присутствующий в RM0008 файле напрочь отсутствует в stm32F103xb.h Кубом предоставленным...

-

Может кого-то сталкивался. Имеется stm32F103 , GD32 и АРМ32 Вопрос, как лучше в программе различать, на каком она чипе запущена , что-б корректно работала?

-

Буду пробовать, но это же в Вивадо придется делать, а потом переносить в ISE навигатор, в проект для 6-го Спартана.. Как вариант сделать все в EDK, но по какой-то причине из-под EDK не работает прогрмматор, Impact шьет отлично, а Platform std. не видит программатор ..

-

наверное будет проще свой модуль между сделать, "оригинальный" имеет всего 6-Lut-ов ))

-

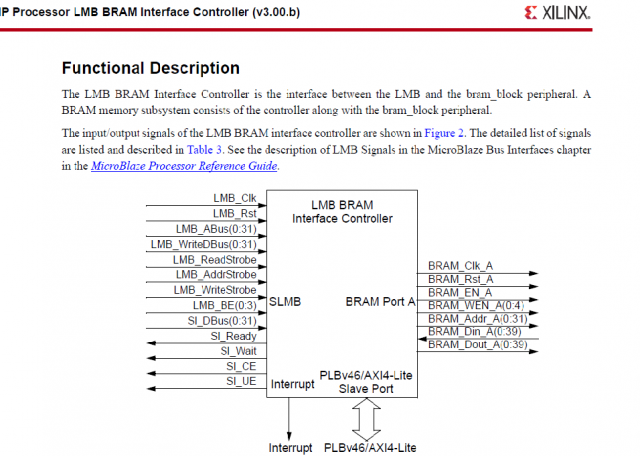

хотелось из МCS иметь доступ ко второму порту памяти bram, используемой HDL модулем, прорчел что такое возможно, IP CoreGen сделал mcs, bram модуль, а вот контроллер ,чтоб поставить между ними он уже не пакует(

-

Но у MCS есть IO-шина, с которой ,если правильно понимаю, присутствовавший ранних версиях CoreGen - контроллер умеет работать? "

-

-

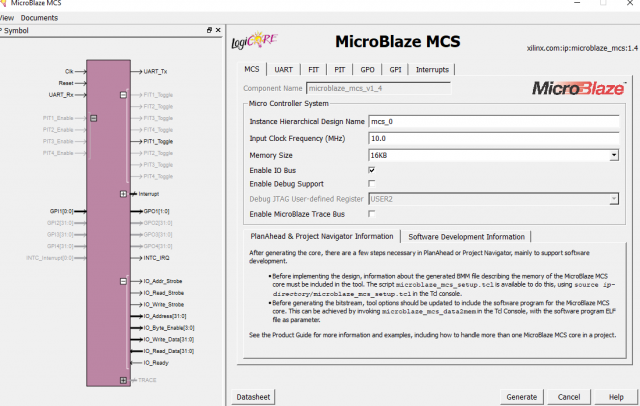

В LogіcСore ІР -генераторе ,покрайней мере в версии что у меня, при конфигурации Микроблейза нет прямой возможности организовать отдельную AXI -шину, хоть, как понимаю ,они встроены для работы mcs с контрллерами памяти инструкций и данных.. Ксожалению для меня это еще пока сложновато, посему хотел воспользоваться IO-шиной и BLM , ума не приложу, зачем надо было выпиливать контроллер, который уже был..

-

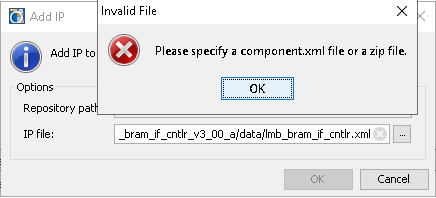

-Необходимо связать модуль "внешней" ВRAM с Мicroblaze , и то и то есть в Logicore, а вот отдельного BLM контроллера там уж нет, понимаю, что для памяти софт-микроконтроллера он присутствет , но как его использовать пока не знаю.. - ни в ISE ,ни в Planahead-е ХМL файл присутствующий в указанной папке файл не генерится в хсо, проект в ISE не в EDK. P.S. Перевел проект в PlanAhead , попытка "прикрутить корку" тоже не увенчалась успехом, несмотря на наличие файла ,появляется сообщение об отсутствии необходимого

-

-Cпасибо огромное, но LogіcСore отказывается его принимать, пишет : Unable to import non-IPXACT metadata file

-

LMB BRAM Controller is absent today

dimone опубликовал тема в Среды разработки - обсуждаем САПРы

ISE 14 7 LogіcСore нет LMB BRAM контроллера.., в ISE 13.2 он был, а теперь только в Vіvadо, которыи не поддерживает 6-ю серию.. Подскажите как быть.. -

Вполне рационально и интерес обоснован, что кроме TPS62xx используется, раз у каждого свой, и запас -мешок..) mov TLV62568 не имеет встроенного делителя, собственно такую-же, только более дешевую NCP1529на "фиксированную" заменить и хотелось(

-

https://www.digikey.com/products/en/integrated-circuits-ics/pmic-voltage-regulators-dc-dc-switching-regulators/739 -спасибо за подсказку, но кроме выше перечисленного лишь экзотика : SC46х,SC189,XC926, неужто от известных производителей в корпусах WSON или SОТ нет ничего? -лопатил MIC,ON(FC),AD.. пусто(

-

Выбор синхронного DC\DC стабилизатора

dimone опубликовал тема в Силовая Преобразовательная Техника

Подскажите пожалуйста может есть "ходовой" низковольтовый (входное до 5.5-6В) синхронный стабилизатор на фиксированные 3.3 , на максимальный ток 1А и более, частотой 2МГц и выше, и главное не в "ВGA" подобном корпусе ,или покрайней мере больше чем 0.4мм межвыводным, т.е. LM3281, FAN5361 не подходят, tps62хх как крайний , но вдруг есть альтернатива? -

Как объединить два простых проекта в ISE

dimone опубликовал тема в Среды разработки - обсуждаем САПРы

Есть два простых отдельных проекта , каждый со своим топ модулем на Верилоге и ucf -файлом , подскажите как объединить их в один проект, ибо простое добавление приводит к тому, что компилируется лишь файл топ-модуля, а второй игнорится, оба ucf при этом подвязываются к топ-у, и соответственно один из них ругается, что нету таких сигналов.. Понимаю, что это тривиально, но все-же.. -

вынужденно портируюсь с Атмега1281 на 2561, соответсвенно поменялся режим с -v3 на -v5, на простом тестовом коде , который работает на 128-й ,линкер выдает ошибку : struct my_str{char *str_pnt;}; struct my_str my_ins[]= { "strng_1" , "strng_2" , "strng_3"}; void *p ; #pragma type_attribute=__nearfunc void main(void) { p=(int *)&my_ins; } Error[e133]: The output format intel-extended cannot handle multiple address spaces. Use format variants (-y -O) to specify which address space is wanted подскажите, что не так?

-

UPD:таки да,-заменил кварц , было 18,4295 и все пошло.. Ситуация вполне куръезная. -Имеется стадо J-link-ов (клонов).. Не секрет, что их прошивке своиственно иногда "слетать".. Такие окирпиченные экземяры собираются в ящике, по достижении критического кол-ва которых выделяется человек, который нехитрой процедурой стирания и восстановления заводского загрузчика , с последующей загрузки J-link-овской прошивки Самбой, приводит их в рабочее состояние, с последующим обновлением прошивки до текущей. Таквот есть один экземляр , который при обновлении, а оно предлагается повидимому всегда, при исользованнии Сеггеровских драйверов , начинает обновляться, и не вкладываятся в отведенный на эту процедур таймаут буквально на несколько миллисекунд, обратно окирпичивается.. Причем ,если не обновлять его прошивку, то он работает нормально, но окно о необходимом обновлении появляется при каждом обращении к программатору, и если по-запарке нажать не "no", то результат -предсказуем( Может кто подскажет, что можно сделать, чтоб он не выбивался из "стада"?.. ,-кварц менять что-ле?

-

в EmWin-е вроде свои RLE есть, крупных шрфтов избыточность очевидна, со шрифтами то я управлюсь , мне было интересно решение вопроса мегапрошивки в принципе.

-

-это разрешение ОЛЕД индикатора. Попробуйте растеризовать кириллицу+латинницу и указаный вами диапазон для одного лишь нежирного Аrial 48 для LCD естесственно понадобятся значительно большие, если на пол-высоты крана цифири, а хотя бы на треть сообщния.. Естесственно соглашусь , что технически это всё тем или иным способом решается, просто было интересно, как можно обоити ограничения

-

интересно, когда придется работать с трехбайтовыми адресами, в мегах выше 64-й, из-за 16-ой флеш адресации, и побайтовой Озу, при описании движения констант меж ними потребуют работу с модификаторами generic (IAR) ,куча мата от линкера, и прочая..

-

В существующем дивайсе, на растеризованыйи Arial шести минимально необходимых размеров, где лишь кириллица и цифры, причем большие размры лишь цифры, для оледа 256х 64 , уже тянет на 1Mб.. для LCD этого явно не хватит.. аналог https://www.systecnet.com/en/products/IT3.html

-

..ну, к примеру ,раз про шрифты зашло, -движок распаковки ttf, кодеки, микропитон, ТСР\ІР все протоколы..

-

как бородатый вариант, допаять линейку памяти, таки да, СД -шку, запустить на (лучше 20Мгц) Мег виртуалку, и поднять Линуху)))) https://habr.com/post/177425/