snayperAlfa

Свой-

Постов

126 -

Зарегистрирован

-

Посещение

Весь контент snayperAlfa

-

Трилатерация и Мультилатерация

snayperAlfa ответил snayperAlfa тема в Математика и Физика

Хм. Спасибо за ответ, но я хочу найти алгоритм выбора ;) Сейчас у меня реализован полный перебор: строятся все возможные комбинации треугольников. -

Трилатерация и Мультилатерация

snayperAlfa опубликовал тема в Математика и Физика

Всем привет. Известно что в GPS приемниках используется мультилатерация, но я пока не смог найти в интернете ее алгоритма. Интересует каким образом происходит выбор точек для определения своего местоположения. Ведь если есть много спутников, то из них выбираются для расчетов спутники с некими "лучшими" характеристиками (мощность сигнала) ? -

Таже проблема. Я из архива запускаю win2000.inf и получаю сообщение "Установка не выполнена" Проблема решена подробным следованием инструкции Альтеры

-

Это там LGA2011 сокеты? :blink:

-

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Это диплом специалиста. А у меня диплом магистра -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Не потянет эта тема на магистерскую работу. Нет в ней науки и актуальности,как мне сказали преподы. Вот улучшение некоего параметра в трансляторах потянет на научность, но все же среды разработки закрыты для ПЛК. Так что надо срочно придумывать другую тему диплома :( -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Что конкретно понимают под SCADA системой. Насколько я понял из описания, это универсальная программа-конструктор в которой создается нужный интерфейс взаимодействия с пользователем. Что-то по типу WindowsForms из Microsoft Visual Studio. -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Точно...Программируется на С. tyro Я изначально под Windows и нацелился, так что есть поле для работы! -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

http://www.mikroe.com/eng/products/view/53...-v6-plc-system/ Вот по этой ссылке приведен проект ПЛК на Атмеге. МДааа... Актуальность диплома уменьшается с каждым новым ответом в этом топике Попробую реализовать это лучше! -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Среда эта будет уровня "Made by Student". Времени до конца года.Диплом магистра. Нужно будет разработать алгоритм переноса программы из графической схемы "LD" в С-шный код. Задачка еще та... -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Хм, чистый ассемблер! -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

У меня пока мысли такие: Написать собственную среду, которая будет генерировать код на С, а этот код будет компилироваться WinAVR или другим каким нибудь компилятором. Но это пока предположительная мысль. Язык думаю использовать Ladder Diagram -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

У меня будет бюджетная версия ПЛК на Атмеге B) -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

Выходит, ПЛК и программное обеспечение к ним "создаются" в CoDeSys ? Я уже начинаю разочаровываться в теме своего диплома -

ПЛК и их внутренности

snayperAlfa ответил snayperAlfa тема в В помощь начинающему

CoDeSys - это некая общая среда разработки для программ ПЛК? -

ПЛК и их внутренности

snayperAlfa опубликовал тема в В помощь начинающему

Приветствую всех! Хотелось бы узнать про внутренности ПЛК (PLC). На основе каких контроллеров/ПЛИС/x86-компьютеров/одноплатных компьютеров строятся. Желательно приводить конкретные модели, например : на основе LPC3222 или на базе Tion S931 ну и так далее. А если еще и ссылки на сайты, торгующими ими - то вообще замечательно! Мне тут по учебе нужно будет реализовать ПЛК на Атмеге, написать среду разработки для LD. На готовый проект с атмегой можете не кидать - я его уже нашел. И одним из пунктов диплома есть обзор конкурентов и существующих решений, поэтому мне надо узнать на основе чего строятся промышленные ПЛК. Всем заранее спасибо. -

Кажеться разобрался. Надо перестать использовать слово байт, а перейти на бит. И использовать термин - поток битов. Тогда всё становится более понятно :) Спасибо, SFX :)

-

Вот запустил это на С: //слева в выводе младший бит #include <iostream> using namespace std; unsigned long data_in=0; unsigned long counter=31; //5-bit counter; Initial value unsigned long reg=1048575; //(2^20)-1 20-bit register; Initial value unsigned long a; unsigned long b; unsigned long c; unsigned long d; unsigned long e; //Функция которая возвращает значение бита в слове unsigned long bit10(unsigned long data,unsigned long bit_number); //Процедура которая возращает 1 если Счетчик==30 //или 0 если Счетчик!=30 unsigned long outc(void); //процедура которая инкрементирует счетчик void counter_inc(void); int k=0; int main() { cout << "!!!Hello World!!!" << endl; // prints !!!Hello World!!! //Initial values counter=31; //5-bit counter; Initial value reg=0b11111111111111111111; //(2^20)-1 20-bit register; Initial value a = bit10(reg,0) ^ bit10(reg,8); a=bit10(a,0); b = ~(bit10(reg,2) ^ bit10(reg,19)); b=bit10(b,0); c = outc(); d=~(b^c); d=bit10(d,0); e=~(data_in ^ d); e=bit10(e,0); for(int i=0;i<64;i++){ //State 0 e=~(data_in ^ d); e=bit10(e,0); reg=reg<<1; reg=reg|e; counter_inc(); c = outc(); a = bit10(reg,0) ^ bit10(reg,8); a=bit10(a,0); b = ~(bit10(reg,2) ^ bit10(reg,19)); b=bit10(b,0); d=~(b^c); d=bit10(d,0); //e=~(data_in ^ d); //e=bit10(e,0); cout<<e; k++; if(k==8){k=0;cout<<'\n';} } return 0; } //Функция которая возвращает значение бита в слове unsigned long bit10(unsigned long data,unsigned long bit_number) { if((data & (1<<bit_number))>0) {return 1;} else{return 0;} }; //Процедура которая возвращает 1 если Счетчик==30 //или 0 если Счетчик!=30 unsigned long outc(void) { if(counter==30){return 1;}else{return 0;}; }; void counter_inc(void) { if(a==1){ counter=31; } else{ if(counter==31){ counter=0; } else { counter=counter+1; } }; }; Баг в том,что сначала выводится младший бит. То есть, слева младший бит. В результате выдало следующее: Слева МЛДАШИЙ бит! !!!Hello World!!! 11111111 =0xFF 11111111 =0xFF 11111111 =0xFF 11111110 =0x7F 11011011 =0xDB 01101101 =0xB6 10100110 =0x65 10011010 =0x59 Теперь надо понять почему слева младший бит, а не старший. Или так и должно быть. В стандарте там описано последовательность байтов, а не битов.

-

Завтра на работе проверю

-

Насчет дублирования: 1) e=d_in xnor d; // тут значение до всех операций 10) e=d_in xnor d; //тут значение после всех операций xor,xnor. Оно ведь может отличаться от значения до операций сдвига,счетчика.... 11)Вывести значение "e" //Поэтому принимаем вот это значение за результат Данный скремблер я буду реализовывать на C, а на VHDL пока моделирую что-бы понять правильность работы. Да и с битами на VHDL удобней работать. В конечном итоге у меня будет полностью последовательный код.

-

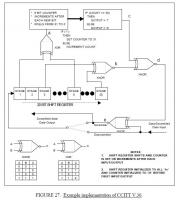

Напишу на смесе C и VHDL Правильно ли я понимаю: Инициализация: REG="11111111111111111111"; Counter=31; a=REG(0) xor REG(8); b=REG(2) xnor REG(19); c=0; d=c xnor b; e=d_in xnor d; Рабочий режим: 1) e=d_in xnor d; 2) REG = REG << 1; //сдвиг влево = умножение на 2 3) REG(0)=e; 4) if(a='1') then Counter=31; else Counter=Counter+1; end if; 5) if(Counter=32) then Counter=0; end if; 6) if(Counter=30) then c='1'; else c='0'; end if; 7) a=REG(0) xor REG(8); 8) b=REG(2) xnor REG(19); 9) d=c xnor b; 10) e=d_in xnor d; 11)Вывести значение "e" 12)Перейти к пункту п.1

-

Я смотрю по диаграмме, что ваша последовательность выходная отличается: По стандарту:0xFF,0xFF,0xFF,0x7F,0xDB..... А у Вас: 0xFF,0xFF,0xFF,0x7F,0xBF....

-

Спасибо, буду разбираться. Можете написать пожалуйста, какова последовательность действий. Сдвиг регистра, увеличение счетчика, вычисление функций XOR, XNOR. Также мне кажется странным описание счетчика.

-

Scrambler

snayperAlfa опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Хочу вот реализовать скремблер. Есть документ, описывающий его работу. Но мутный немного. особенно в планек счетчика. Я создал модель на VHDL, но выходная последовательность отличается от той что задана в документации. Подскажите где может быть баг пожалуйста. library IEEE; use IEEE.std_logic_1164.all; entity Scrambler_1 is port ( CLK: in std_logic; data_in: in std_logic; data_out: out std_logic; CLK_out:out std_logic ); end entity; architecture Scrambler_1 of Scrambler_1 is signal STATE:integer:=0; begin process(CLK) variable reg:std_logic_vector(19 downto 0):=(others =>'1'); variable a:std_logic; variable b:std_logic; variable c:std_logic; variable d:std_logic; variable e:std_logic; variable counter:integer; begin if(CLK'event and CLK='1' ) then CASE STATE is when 0=> CLK_out<='0'; --Initial values; reg(19 downto 0):=(others =>'1'); counter:=31; a:=reg(0) xor reg(8); b:=reg(2) xnor reg(19); c:='0'; d:=b xnor c; e:=data_in xnor d; data_out<=e; STATE<=1; when 1=> e:=data_in xnor d; CLK_out<='0'; --sdvig registra reg(19 downto 1):=reg(18 downto 0); reg(0):=e; a:=reg(0) xor reg(8); b:=reg(2) xnor reg(19); counter:=counter+1; if(a='1') then counter:=31; end if; if(counter=32) then counter:=0; end if; if(counter=30) then c:='1'; else c:='0'; end if; d:=b xnor c; e:=data_in xnor d; data_out<=e; STATE<=2; when 2=> CLK_out<='1'; STATE<=1; when others => null; end case; end if; end process; end architecture; У меня получается последовательность: 0xFF,0xFF,0xFF,0xFD,0xB6,0xDB -

О чудо!!! Перевод неиспользуемых пинов в Z состояние помог! Спасибо за подсказку :)