-

Постов

9 579 -

Зарегистрирован

-

Победитель дней

4

Весь контент des00

-

Говина у меня конечно нет, но ЕМНП, все такие штуки делаются через AND-OR мульиплексор, в управлении которого стоит синхронизатор в домен. И он требует двух тактов частоты, чтобы перещелкнуться. А некоторые ещё требуют наличия всех тактовых частот для переключения. А вот почему он у вас включается по умолчанию, да, интересный вопрос.

-

По идее он же тикл поддерживает из коробки, добавить пару сигналов, а дальше по образцу?

-

Работа сайта и сервера

des00 ответил admin тема в Новости и обсуждения сайта и форума

У вас нет одной кнопки. В элеганте там есть кнопка Show My Online Status (у меня английская версия настроек, без русификации). -

Работа сайта и сервера

des00 ответил admin тема в Новости и обсуждения сайта и форума

прикольно, я статус сам ставил, но думал что это только снимает статус онлайн(и не показывает в статистике онлайн пользователей на форуме), а не время последнего посещения) -

Работа сайта и сервера

des00 ответил admin тема в Новости и обсуждения сайта и форума

заметил забавный баг/фичу: там где у обычного пользователя, при наведении на аватар, написано когда он был последний раз, у модератора написано когда он пришел на форум) Ну т.е. у модератора не указано Last Visit. Тема elegant -

Setup Transfers

des00 ответил _sda тема в Работаем с ПЛИС, области применения, выбор

а временной анализ сколько путей показывает? -

Инициализация вектора

des00 ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

вот первая строка из гугла, там про агрегаты в контексте одного бита https://stackoverflow.com/questions/60330923/assigning-initial-value-to-vhdl-vector сверится со стандортом и передалать агрегат на несколько бит. а вот шестая строка из гугла https://stackoverflow.com/questions/16593125/vhdl-how-to-initialize-my-signal где разобраны случаи еще более сложных назначений. -

Инициализация вектора

des00 ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

а стандарт читать сейчас вообще не принято? ну ладно, читать это сложно, но банально погуглить по ключевым словам "VHDL vector initialization" вообще никак? -

емнп, они требуют синхронного снятия сброса и гарантированной минимальной длительности.

-

-

появилась типизация, появились к ней инструменты, коммитет по 1800 довольно гибок в этом вопросе)

-

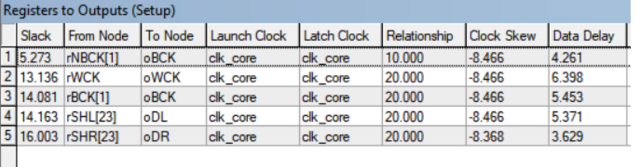

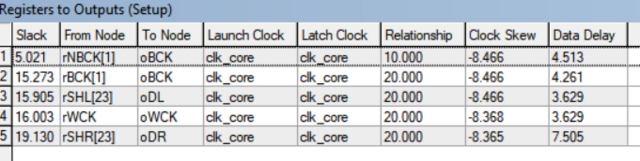

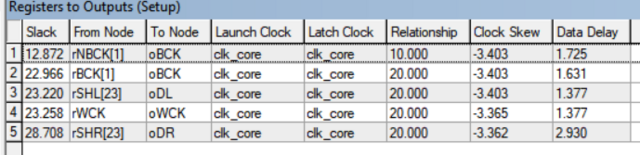

ну да, просили 7-8нс на пин, он сделал 3.6нс и 5.3нс, когда попросили 15 и 7 он сделал 7.5 и 3.6. Причем это только один coner case(slow) из двух-четырех который проверяется, в других другие задержки и другие разбросы) вот например что будет в fast при запрошеных 7-8 по oDL и 14-15 по oDR Одним словом К - качество) PS. Вы же сами писали " Типа если надо задержка, то просто добавляется пара инверторов и готово." не добавляется, не умеет он так)

-

да нет между ними разницы, просто $signed это системная функция появилась в ревизии стандарта 1995 года (тут я ошибся), в 2001 году. IEEE Std 1364-2001, а signed'() квалификатор приведения типов это SystemVerilog IEEE-1800-2009 (хотя сам SV пошел с 2005 года) с учетом того что вивада идет с 2014 года, скорее просто программисты забили на новые фенечки, а вот старые должны работать) Но вообще как бы 2018 вивада в 2023 году это уже очень старо.

-

ну еще бы, функция с 1995го года не может не работать, это не модные свистопляски))

-

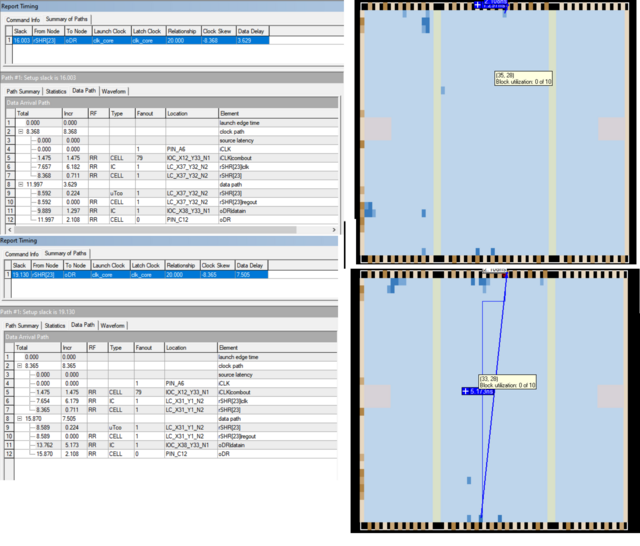

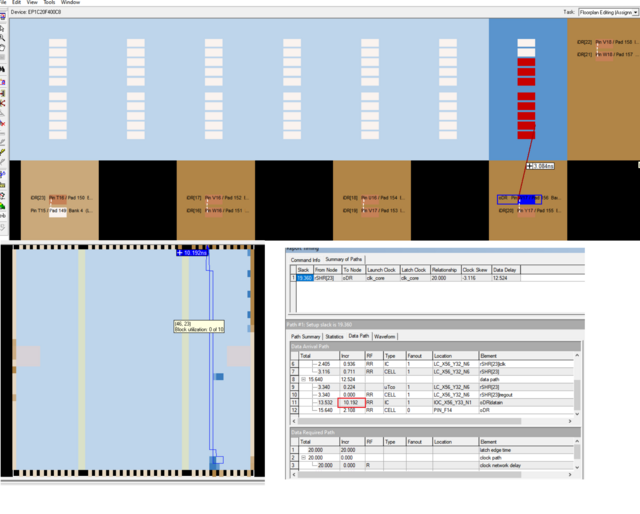

Ну собственно чуда и не произшло (а то я уж было подумал что мне приснилось). Если прибить пины гвоздями, то результат как получится так получится) да, он пытается что-то сделать получше, но чисто за счет расстановки регистра источника, никаких добавить/поелозить по чипу круги и прочего он не умеет) Сверху решение когда ставим 8/7, снизу 15/14. И да, все это за счет того что стоит запрет на размещение триггера в ячейке ввода-вывода. Если поставить регистр туда (Fast output = on), то все его шаги это те самые 0.5нс задержки в режиме вкл-выкл.

-

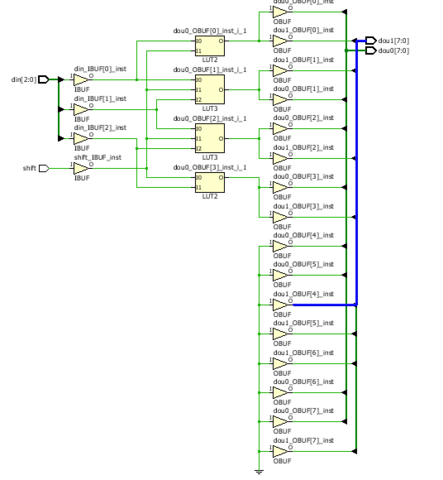

такс, покрутил выложенный проект, да, стоит запрет на использование регистров в портах ввода-вывода, но, никаких вставок не замечено, пины не прибиты, ква делает задержки размещая их куда хочет. На скрине сверху то что при задержках 8/7, ниже 15/14. Но это тоже своего рода выравнивание. Прибью пины посмотрю что получится.

-

спасибо посмотрю, лет 15 плотно работал с альтерой, от первого сыклона до пятой арии, у меня он никогда их не двигал в таком диапазоне. зайлинкс тоже не двигает, даже модули задержек не крутит, там все надо в ручную делать и констрейны там только что бы убедиться что все выполняется.

-

Очень интересный экспиремент. Особенно если учесть что set_output_delay задает временное окно параметров, для выполнения временных ограничений tsu/th внешнего (вне плис) триггера, подключенного к портам, работающего на заданной тактовой, а не задержку сигнала как таковую. В частности -max и -min заданные у вас означают tsu = -15нс и th = 14нс у внешнего триггера тактирующегося на тактовой clk_core вне плис. В проекте стоит Fast output register = off? Report Full path -detailed надо сделать в отсчетах временного анализа, тогда он покажет как именно и через что он вел сигнал. Вы можете дать этот проект покрутить? Первый раз такое вижу, что-то тут не то.

-

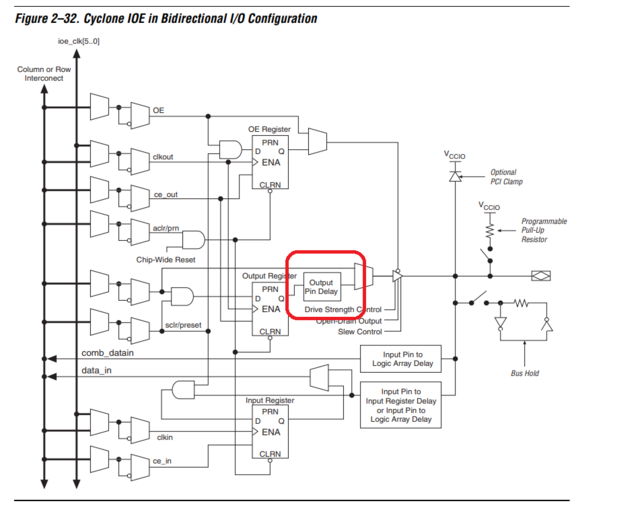

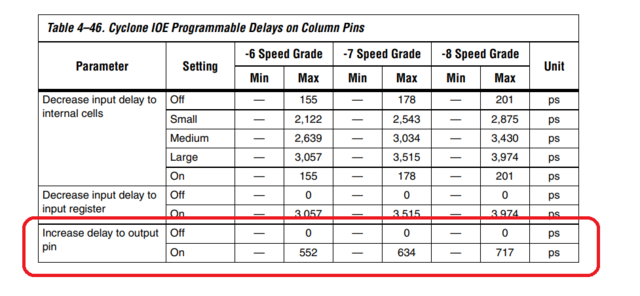

Полагаю что надо было с даташитами на сыклон и латекс ознакомиться, а потом Resource property Editor посмотреть Но величина этой задержки, на сыклоне, всего лишь Поэтому что там у вас хорошо двигается (тем более на 10нс) не ясно. Плис это же не асик, не умеют софты регулировать внешние задержки вставкой LCELL ов, максимум подвигать модули в IO delay, да и то не во всех плис. Вставлять LCELLы в ручную надо, но повторюсь, почему нельзя использовать DDR выход для передачи битового клока? synthesis keep/noprune атрибутов или других, которые запрещают удалять модули с логическим bypass в этом софте нет?

-

1. а вы вообще уверены что в этом семействе плис есть аппаратные блоки что бы двигать задержку выходных сигналов? 2. почему не вывести bitclk как сигнал данных на той же тактовой частоте? В чипе нет выходных DDR регистров?

-

Алгоритм CIRC, CD, Red Book

des00 ответил repstosw тема в Алгоритмы ЦОС (DSP)

"Мазать" - размазывать вашу ошибку на как можно больший блок. Если это не применимо, и нельзя поставить второй тракт, ну значит нет других вариантов. ЕМНП если прыгать за пределы полосы когеретности то состояние канала в другой частотной точке будет отличаться. Если прыгаете из нуля туда где нуля нет и добавите перемежение данных согласованное с прыжком то может быть что-то можно будет выиграть. типичное значение 1000 скачков частоты в секунду. Это 1мс. Но это похоже не для вашего радиотракта. Это не частотное резервирование. Частотное резервирование это у вас два тракта RX-TX, один на 438МГц, другой например на 832 МГц, информация ходит одинаковая, по приему вы декодируете оба и выбираете пакет из того канала, который не битый. Вот например тут https://habr.com/ru/articles/480124/ на графиках чел показывает как работает частотное резервирование каналов БПЛА -

Алгоритм CIRC, CD, Red Book

des00 ответил repstosw тема в Алгоритмы ЦОС (DSP)

У него процессор мелкий, от такого БЧХ он подохнет. На плис да, 3-5к логики и будет летать -

Алгоритм CIRC, CD, Red Book

des00 ответил repstosw тема в Алгоритмы ЦОС (DSP)

ИМХО, при такой структуре ошибок(у вас тупо теряется пакет в некоторых точках), никакой код не поможет. Облегчить, вы сами к этому пришли: большой блок и мазать, мазать, мазать. Прыжки по частоте можно попробовать, как выше упоминалось. Есть системы которые прыгают по частотам + изучают куда прыгать не стоит. Ну и опять же значение прыжка определяется свойствами канала (какой смысл прыгать из замирания в замирание). Но это наверное все же больше в сторону кастомного радиотракта. Но и может уже пришло время смотреть в сторону частотного резервирования: одновременная прием-передача на существенно разных частотах? поставить 2/4 антенны как в сотовом телефоне. Или они у вас строго внешние? -

Алгоритм CIRC, CD, Red Book

des00 ответил repstosw тема в Алгоритмы ЦОС (DSP)

таких тонкостей, за давностью лет, я уже не помню, парни делали свои реализации 264 для embedded. Единственная цифра которую помню что стандартный диван 25фпс, без каких либо ухищрений укладывается в 2 мегабита, CIF в 4 раза меньше, а у выложенной выше игрушки разрешение еще меньше CIF. Это без дополнительных оптимизаций. -

Алгоритм CIRC, CD, Red Book

des00 ответил repstosw тема в Алгоритмы ЦОС (DSP)

Вам конечно виднее, но еще лет 10 назад, знакомые ребята приносили модуль с 264 для БПЛА, который на CIF ЕМНП требовал порядка 100кб/с.