-

Постов

278 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные dm_mur

-

-

On 8/26/2022 at 12:09 PM, ASN said:

Напряжение питания банков IO (для 074)

Озвучил. 2.5V

-

1

1

-

-

On 8/25/2022 at 6:07 PM, ASN said:

Особенно шикарно выглядит тезис, про "...ТС064, ТС084, ТС094, ТС104 - больше их не будет". То есть, деньги освоили и "всем спасибо, все свободны".

Дословно - "вопрос по размещению заказа в производство кристаллов не решен". То, что их не будет, думаю понятно. Вопрос про освоение денег, доверие и.т.д - наверное в большей степени флуд. Мне лично интересна чисто техническая информация.

-

По информации из Воронежа:

5576ХС1, ХС4, ХС7 - корректируется документация для размещения заказа на производство кристаллов (переносят на Микрон?)

5576ХС6 - кристаллы производит Микрон, поставляться эти ПЛИС будут

5578ТС024, ТС034, ТС044, ТС054, ТС074 - кристаллы производит Микрон, поставляться эти ПЛИС будут

5578ТС064, ТС084, ТС094, ТС104 - больше их не будет.

-

1

1

-

-

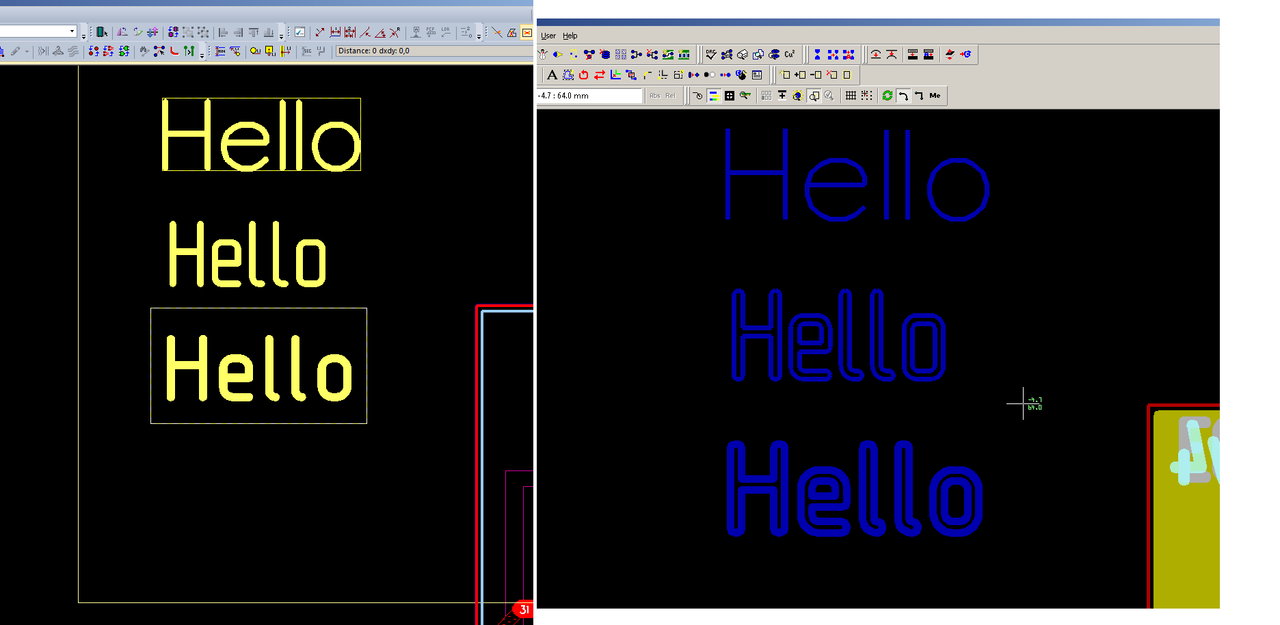

On 3/3/2016 at 10:07 PM, Александр_2003 said:

Нужно прописать, как фонт виндовс, и выбрать его в менторе.( расширение поменять на ttf)

Спасибо за внимание.

Спасибо, работает

-

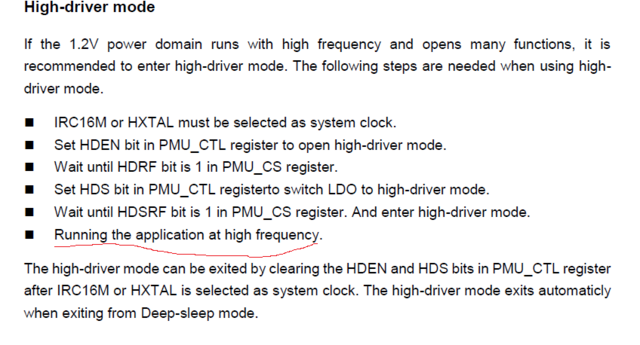

On 7/13/2022 at 5:41 PM, Сергей Борщ said:

Нет. Там строчкой выше написано "following steps are needed...", следовательно это и есть один из тех шагов, которые нужно выполнить для перехода в данный режим.

Я имел ввиду предложение: If the 1.2V power domain runs with high frequency...

On 7/13/2022 at 5:55 PM, 0men said:у вас ошибочное понимание. High-driver mode только для тактирования системного клока от IRC16M или HXTAL. Для тактирования от PLL хайдрайв мод не нужен.

Хорошо. Что тогда я делаю не так? Могу прислать свой проект в Keil

-

On 7/13/2022 at 12:45 PM, Сергей Борщ said:

Это же алгоритм запуска режима, а не перечень условий для его запуска.

Для толкования смысла этого краткого абзаца лучше вообще пояснительную бригаду вызвать. Первое предложение - это разве не условие для переключения в данный режим? Ну и анализ исходников от GD как бы тоже намекает... Но суть в том, что не работает у меня

-

On 7/12/2022 at 5:35 PM, 0men said:

я кажется понял в чем у вас проблема. У вас тактирование системного клока идет от кварца напрямую, в этом случае нужно устанавливать эти биты, у меня же кварц идет на плл, а потом уже на системный клок, в этом случае биты High driver mode не нужны

Из сего документа на мой взгляд как раз следует, что в High-driver mode следует переводить при использовании PLL (то есть запуска приложения на высокой частоте тактирования).

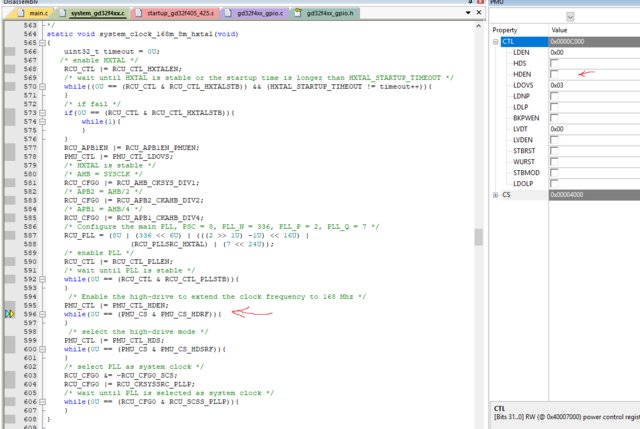

Мое понимание прочтения этого кусочка UserManual соответствует и порядку инициализации системных клоков (функция system_clock_config) в файле system_gd32f4xx.c из пака от GD:

зависает он как раз в цикле ожидания бита готовности (строка 596). При этом бит HDEN не взвелся, хотя его установка была в 595 строке Если переключение в High-driver mode здесь вообще убрать, то проц непонятно куда вылетает (от жтаг просто отрубается и виснет).

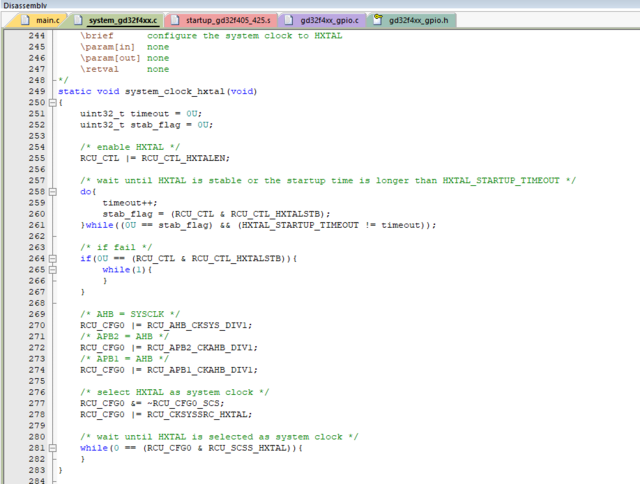

Если выбрать тактирование от внешнего кварца на частоте кварца (без PLL), то проц запускается нормально. При этом в исходниках инициализации системных клоков от кварца без PLL нет и переключения в High-driver:

чето голову сломал уже. Хотя скорее всего в трех соснах блуждаю

-

On 7/6/2022 at 1:18 AM, 0men said:

GD32F405 спокойно заработал с прошивкой от стм32ф405 без изменений. Юсб девайс, уарты, таймеры, спи, тви, дма

Скажите, от чего у вас тактируется GD32? При тактировании от PLL внутренний регулятор GD32 нужно переключать в High driver mode (биты 16, 17 регистра PMU_CTL). У STM этого нет. У меня GD32 виснет в цикле ожидания бита HDRF, причем судя по отображаемым значениям регистра PMU_CTL в отладчике, бит PMU_CTL_HDEN остается нулем после записи туда 1. Тактирование PMU включено. При этом если не заводить PLL и оставить тактирование на частоте кварца, проц заводится и ножками дрыгает.

-

On 6/19/2022 at 4:12 AM, FeodoR said:

Если я не прав и SignalTap заработает у кого-либо на ТС064, ТС084, ТС094, ТС104 при их, наконец-то, доступности, будет просто замечательно, правда!

Заработал. C SignalTap все не так печально, с доступностью хуже)

-

Коллеги, работает ли с 5578TC064 SignalTap? У меня не запускается(( Кто подскажет?

-

Подскажите, коллеги.

Осваиваю маршрут проектирования для 5578ТС064. Столкнулся с тем, что в Quartus 13.0 во вкладке Back-Annotate Assignments отсутствует пункт «Pin, cell, routing & device assignments»

Подскажите, я не той версией Quartus пользуюсь, или в чем может быть проблема?

-

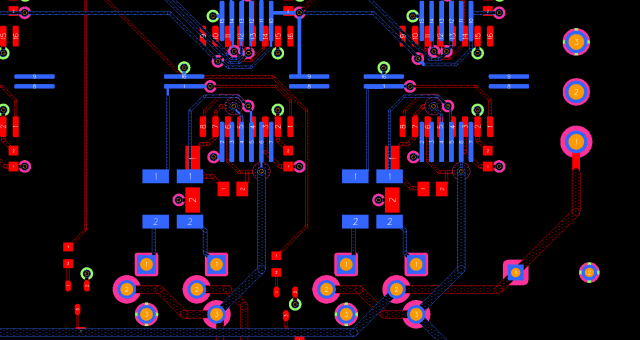

16 minutes ago, Plain said:

Вопрос тот же, что и её автору — без разводки ответ невозможен.

Разводка платы? В аттаче. Макет сделан "универсальным" - с одной стороны можно впаять IR, с другой - 1308. С IR работает корректно, в 1308 при некоторых условиях наблюдаются сбои. Вы использовали когда-либо это драйвер?

-

4 hours ago, Plain said:

На какие? Что процесс импортозамещения увеличил минимум питания логики с 3 В до 5 В? Потому что тема, вообще-то, о другом.

На некорректную работу драйвера по всей видимости, по той же причине что и у ТС. На картинке во вложении синий канал - управление верхним ключем, желтый - в средней точке полумоста, между стоком и истоком транзисторов. Причем, проблема вылезла на "полигоне" у заказчика. На столе в лаборатории явления не наблюдалось У вас есть что по теме?

-

On 12/21/2021 at 10:09 PM, __Sergey_ said:

Использовали почти такой шим-оконечник, только на 27 В, совершенно успешно. Наш программист, тертый калач, сам выставляет мертвое время на VIH-VIL, не рассчитывая на 1308УЕБУ.

Нас тут всех трясет от импортозамещения!!!

1308ЕУ3 сама не генерит "мертвое" время, как и ее прототип. Поэтому в любом случае его нужно формировать контроллером.

-

On 11/21/2018 at 2:27 PM, Zuse said:

это при питании цифровой части 15 В

а при меньших питаниях лог. 1 ~ 0.7*Udd

Добрый день! Скажите, вам удалось побороть проблему? Какие рекомендации дал производитель? Тоже наступили на эти грабли.

-

8 minutes ago, PBO said:

Сами вы врядли создадите так как слишком много параметров описывать

Главное - понимать, что именно, как и где описывать, а такого понимания нет(

-

Коллеги, есть ли у кого-либо положительный опыт по созданию библиотечного элемента ПЛИС из тех, что не поддерживаются MG, чтобы с ним корректно работать в FPGA I/O Optimizer? Есть ли вообще такая возможность? Я имею ввиду Российские ПЛИС производства ВЗПП.

-

-

On 1/5/2019 at 8:23 PM, ProfessorF said:

Помогите, пожалуйста, советом, как лучше всего решить проблему подключения одного пина на схеме к нескольким пинам на печатной плате?

К примеру, есть SOT233, у которого 3 обычных пина и 1 большая площадка (итого: пины 1,2,3,4). И есть линейный регулятор с тремя пинами на схеме. Так вот в зависимости от вариации, большая (четвёртая) площадка подключена дополнительно либо к GND, либо к VOUT. Проблема в том, что хотелось бы сохранить все 4 пина по номерам в cell для универсальности, и в то же время, сохранить в схематике 3 пина и не добавлять дополнительные тоже для универсальности. К примеру, использовать этот же символ для других линейных регуляторов, как и использовать этот же SOT233 для других компонентов, не меняя номеров пинов.

Нашёл тему "Несколько выводов Cell на один вывод Символа", но не совсем понимаю, как совет об иерархии может помочь.

Можно подключить пины, которых нет в УГО символа при создании Part используя вкладку Supply and NC. Такой вариант вас не устраивает?

-

Пока работаем в старой EE 7.9.5, но скоро переедим. Производство хочет в эксельной форме видеть что должно быть куплено и отправлено на монтаж в первую очередь а с чем можно еще пару дней не рвать когти. Пока нашлась только одна идя - перепахать всю библиотеку добавляя всем партнамберам пользовательское свойство SMT или TH. Может можно воспользоваться чем то готовым? Например на основе футпринтов?

Можно воспользоваться VBReport Writer, в одном из отчетов там будет свойство тип монтажа - SMD или TH

-

-

Вопрос может существуют какие нибудь скрипты которые помогаю нормаль переносить название пинов и обозначение (может самих сигналов)?

А то в ручную, это очень заморочено при больше 100 таких соединений. Может еще есть какие варианты.

Писал скрипт, который правит имена выводов, но только в библиотечном символе имена должны быть прописаны в User Property, соответствие имени и номера так же User Property. Eсли у вас нет возможности править библиотеку, тогда не вариант.

-

Добрый день!

Ответьте, пожалуйста, на такой вопрос. Предположим, хочу нарисовать рамку в Symbol Editore. Каким образом отмерить размеры листа в DxDesigner и такие же размеры отмерить в Symbol Editor? Инструментов вроде линейки ни в DxDesigner, ни в Symbol Editor замечены не были. В Альтиуме для этого достаточно нажать Ctrl+M. Тут же приходится подгонять размер, изменяя его "на глазок" в Symbol Editor и используя Tools→ Uptade Symbols в DxDesigner.

В строке статуса SymbolEditor (в правом нижнем углу) отображаются координаты курсора. Отмерить нужные размеры можно по ним.

-

Добрый день. Столкнулся в Xpedition xPCB Layout (версия VX.1.2) о следующим моментом: Имеется на плате цепь ($12N6642), при выделении на принципиальной схеме (в xDX Designer)

она подсвечивается в Xpedition xPCB Layout. Но при этом в среде Xpedition xPCB Layout её невозможно выделить и соответственно ничего с ней сделать.

Использование утилиты: SetFixedAndLockedToLocked.vbs не помогло. Не подскажите как можно с этим побороться?

Она не запрещена Net Filter 'ом?

Обсуждение Xpedition/PADS Designer

в Siemens EDA - Xpedition, PADS (ex. Mentor)

Опубликовано · Пожаловаться

Можно попробовать пины сделать покороче, а в DxDatabook выбрать - Add component with Net Stubs. Тогда компонент будет добавляться с отрезками цепей.