-

Постов

279 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент dm_mur

-

Можно попробовать пины сделать покороче, а в DxDatabook выбрать - Add component with Net Stubs. Тогда компонент будет добавляться с отрезками цепей.

-

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

Озвучил. 2.5V -

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

Дословно - "вопрос по размещению заказа в производство кристаллов не решен". То, что их не будет, думаю понятно. Вопрос про освоение денег, доверие и.т.д - наверное в большей степени флуд. Мне лично интересна чисто техническая информация. -

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

По информации из Воронежа: 5576ХС1, ХС4, ХС7 - корректируется документация для размещения заказа на производство кристаллов (переносят на Микрон?) 5576ХС6 - кристаллы производит Микрон, поставляться эти ПЛИС будут 5578ТС024, ТС034, ТС044, ТС054, ТС074 - кристаллы производит Микрон, поставляться эти ПЛИС будут 5578ТС064, ТС084, ТС094, ТС104 - больше их не будет. -

Спасибо, работает

-

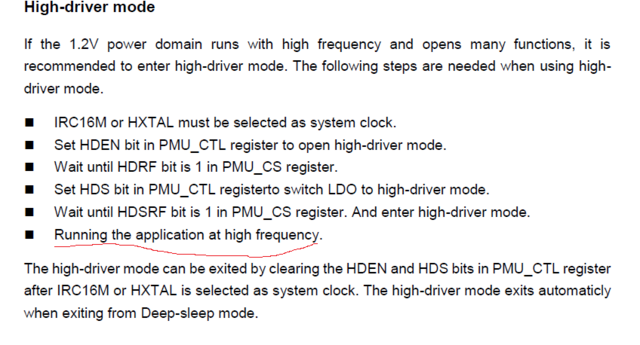

Я имел ввиду предложение: If the 1.2V power domain runs with high frequency... Хорошо. Что тогда я делаю не так? Могу прислать свой проект в Keil

-

Для толкования смысла этого краткого абзаца лучше вообще пояснительную бригаду вызвать. Первое предложение - это разве не условие для переключения в данный режим? Ну и анализ исходников от GD как бы тоже намекает... Но суть в том, что не работает у меня

-

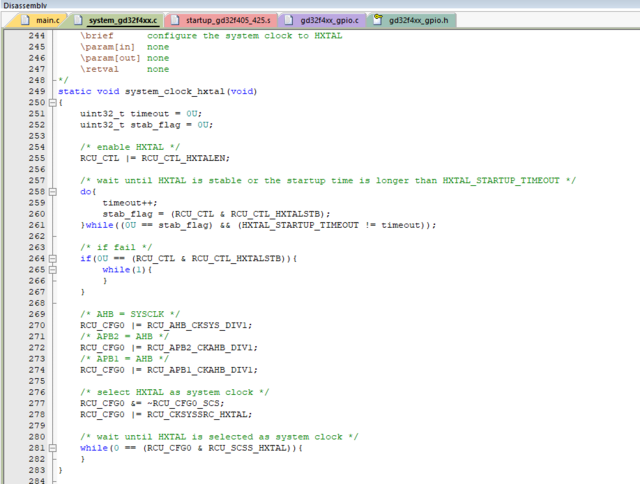

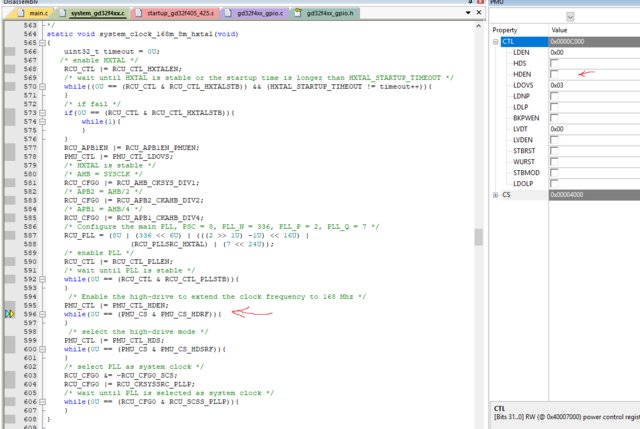

Из сего документа на мой взгляд как раз следует, что в High-driver mode следует переводить при использовании PLL (то есть запуска приложения на высокой частоте тактирования). Мое понимание прочтения этого кусочка UserManual соответствует и порядку инициализации системных клоков (функция system_clock_config) в файле system_gd32f4xx.c из пака от GD: зависает он как раз в цикле ожидания бита готовности (строка 596). При этом бит HDEN не взвелся, хотя его установка была в 595 строке Если переключение в High-driver mode здесь вообще убрать, то проц непонятно куда вылетает (от жтаг просто отрубается и виснет). Если выбрать тактирование от внешнего кварца на частоте кварца (без PLL), то проц запускается нормально. При этом в исходниках инициализации системных клоков от кварца без PLL нет и переключения в High-driver: чето голову сломал уже. Хотя скорее всего в трех соснах блуждаю

-

Скажите, от чего у вас тактируется GD32? При тактировании от PLL внутренний регулятор GD32 нужно переключать в High driver mode (биты 16, 17 регистра PMU_CTL). У STM этого нет. У меня GD32 виснет в цикле ожидания бита HDRF, причем судя по отображаемым значениям регистра PMU_CTL в отладчике, бит PMU_CTL_HDEN остается нулем после записи туда 1. Тактирование PMU включено. При этом если не заводить PLL и оставить тактирование на частоте кварца, проц заводится и ножками дрыгает.

-

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

Заработал. C SignalTap все не так печально, с доступностью хуже) -

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

Коллеги, работает ли с 5578TC064 SignalTap? У меня не запускается(( Кто подскажет? -

ПЛИС наши (Россия)

dm_mur ответил White тема в Работаем с ПЛИС, области применения, выбор

Подскажите, коллеги. Осваиваю маршрут проектирования для 5578ТС064. Столкнулся с тем, что в Quartus 13.0 во вкладке Back-Annotate Assignments отсутствует пункт «Pin, cell, routing & device assignments» Подскажите, я не той версией Quartus пользуюсь, или в чем может быть проблема? -

Защелкивание драйвера 1308ЕУ3

dm_mur ответил Zuse тема в Вопросы аналоговой техники

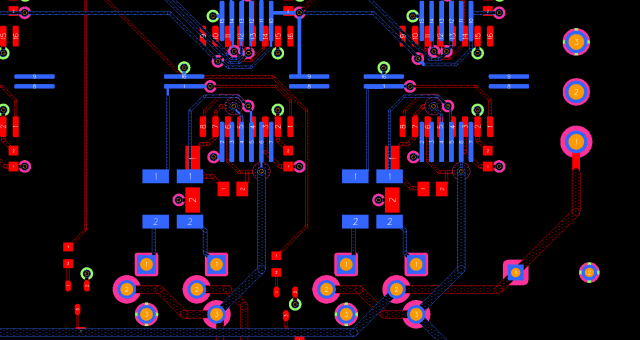

Разводка платы? В аттаче. Макет сделан "универсальным" - с одной стороны можно впаять IR, с другой - 1308. С IR работает корректно, в 1308 при некоторых условиях наблюдаются сбои. Вы использовали когда-либо это драйвер? -

Защелкивание драйвера 1308ЕУ3

dm_mur ответил Zuse тема в Вопросы аналоговой техники

На некорректную работу драйвера по всей видимости, по той же причине что и у ТС. На картинке во вложении синий канал - управление верхним ключем, желтый - в средней точке полумоста, между стоком и истоком транзисторов. Причем, проблема вылезла на "полигоне" у заказчика. На столе в лаборатории явления не наблюдалось У вас есть что по теме? TEK0082.BMP -

Защелкивание драйвера 1308ЕУ3

dm_mur ответил Zuse тема в Вопросы аналоговой техники

1308ЕУ3 сама не генерит "мертвое" время, как и ее прототип. Поэтому в любом случае его нужно формировать контроллером. -

Защелкивание драйвера 1308ЕУ3

dm_mur ответил Zuse тема в Вопросы аналоговой техники

Добрый день! Скажите, вам удалось побороть проблему? Какие рекомендации дал производитель? Тоже наступили на эти грабли. -

Главное - понимать, что именно, как и где описывать, а такого понимания нет(

-

FPGA I/O optimizer - добавление ПЛИС

dm_mur опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Коллеги, есть ли у кого-либо положительный опыт по созданию библиотечного элемента ПЛИС из тех, что не поддерживаются MG, чтобы с ним корректно работать в FPGA I/O Optimizer? Есть ли вообще такая возможность? Я имею ввиду Российские ПЛИС производства ВЗПП. -

Экспорт в DXF из DxD

dm_mur опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Добрый день, уважаемые! После экспорта в DXF схемы из DxD не вижу "точек" соединений. Глюк экспорта? Кто сталкивался? -

Можно подключить пины, которых нет в УГО символа при создании Part используя вкладку Supply and NC. Такой вариант вас не устраивает?

-

Можно воспользоваться VBReport Writer, в одном из отчетов там будет свойство тип монтажа - SMD или TH

-

Без костылей вроде бы никак. При увеличении толщины линии получается тоже ерунда. Пользуйтесь Gerber compatible fonts

-

swapping

dm_mur ответил full41 тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Писал скрипт, который правит имена выводов, но только в библиотечном символе имена должны быть прописаны в User Property, соответствие имени и номера так же User Property. Eсли у вас нет возможности править библиотеку, тогда не вариант. -

В строке статуса SymbolEditor (в правом нижнем углу) отображаются координаты курсора. Отмерить нужные размеры можно по ним.

-

Она не запрещена Net Filter 'ом?