Egor-ka

Участник-

Постов

36 -

Зарегистрирован

-

Посещение

Весь контент Egor-ka

-

Ищу книги, материалы, модели

Egor-ka опубликовал тема в Метрология, датчики, измерительная техника

Добрый день, Ищу книги Горенштейн И.А. Гидростатические частотные датчики первичной информации. Основы теории. М. Машиностроение 1976г. 184 с. Эткин Л. Г. Виброчастотные датчики. Теория и практика. — М .: Изд - во МГТУ им . Н . Э . Баумана , 2004. — 408 с . а также другие материалы по теме вибрационных датчиков с частотным выходом (в частности циллиндрическим) Интересует также их математические модели для реализации в matlab (simulink), в идеале еще бы с ANSYS разобраться) Подскажите, пожалуйста, ресурсы или поделитесь материалами. Спасибо. -

2 вакансии НИИ ПОЛЮС

Egor-ka опубликовал тема в Предлагаю работу

В НИИ "ПОЛЮС" (Москва, м.Калужская) в НПК-660 (оптоэлектроника) требуются специалисты: 1.Инженер-программист Вид деятельности: создание программного обеспечения для ПК. Требования к соискателям: знание языка программирования С++, основных архитектурных особенностей современных операционных систем; опыт работы в средах разработки Microsoft Visual Studio, Digia Qt Creator, с Win32API, с интерфейсами USB, Ethernet. Заработная плата от 60тыс. руб. по результатам собеседования. 2.Инженер-электроник Вид деятельности: разработка схемотехнических решений и программного обеспечения для устройств на микроконтроллерах. Требования к соискателям: знание архитектур RISC и ARM; языков программирования С, С++; современной элементной базы и интерфейсов передачи данных. Заработная плата от 60тыс. руб. по результатам собеседования. Контактная информация: [email protected] тел. +7(925)372-49-42 (Александр) тел. +7(495)333-91-33 (Александр, Сергей) Все вопросы - по телефону, резюме - на e-mail -

Проблема решилась переустанокой с 13.2.5 на 13.3.4

-

После перехода с AD10 на AD13 перестали отображаться (пустые поля) компоненты и библиотеки в панеле Library, хотя в Installed Libriaries все интегрированные и обчные библиотеки подключены... Подскажите, в чем может быть дело?

-

Здравствуйте, Wic. Вы хотели выложить компонент для FT245... Мне сейчас очень актуальна эта тема - как раз разбираюсь с FT245 и хочу приспособитье его под ниос.. Если можете поделитесь HDL-описаниями?

-

Разработчик РЭА (Москва)

Egor-ka опубликовал тема в Предлагаю работу

В НИИ ""ПОЛЮС" (Москва, м.Калужская) в отдел оптоэлектроники требуется разработчик РЭА. Знание схемотехники и программирования МК. Оклад от 30 000р. Контактная информация: [email protected] тел. +7(903)500-21-70 (Александр) -

TCD1304

Egor-ka ответил НЕХ тема в Оптика и оптоэлектроника

Добрый день, хочу возобновить тему. Разбираюсь с этой линейкой. Не могу понять как управлять временем интегрирования - Делаю два импульса SH -один постоянный, другой перемещаю по периоду ICG, но чувствительность ПЗС зависит как от длительности SH, так и от положения импульса. Подскажите однозначный способ управления временем засветки. Может я вообще не так делаю? Частоту подавать на SH не пробовал - еще не разобрался . Что вы имеете ввиду под одноразовым интегрированием? -

2Gate Спасибо за документы, у меня как раз что-то похожее получается. Я пытаюсь усовершенствовать управляемую линию задержки, для этого хочу использовать TDC. Так как устройства такие уже произведены, работаю на имеющейся эл.базе. Поэтому пока GPX не рассматриваю. По поводу разводки межсоединений: нашел, где Quartus это прописывает - файл .rcf - routing constraint file - но пока не понял, можно ли как-то его в этих целях использовать? К тому же, этот файл создается при использовании back-annotation, а как с этим работать тоже пока не понял.

-

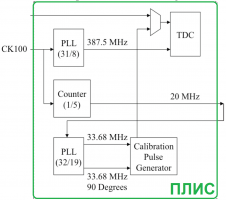

Gate, огромное спасибо - в самую точку. Просто и понятно. :cheers: Что какается Если вы не видели, то я как раз в своем первом сообщении и спрашивал как это сделать... Точность в 10 пс - относится к внутренним сигналам (то что показано на рисунке). Моя задача - задерживать внешний асинхронный импульс на Nое количество времени с максимальной точностью на ПЛИС. Исследую способы повышения точности. Пока добился джиттера выходного задержанного импульса, равного 80% периода внутернней тактовой частоты (от PLL). Если кто-то встреячался с такими заданиями, какой вообще точности следует ожидать? Кстати, кто-нибудь знает как создать генератор кореллированных импульсов, как на рисунке , но с помощью одного PLL?

-

Возможно я ошибаюсь, но как понимаю, констрейны и timequest analysis предназначены в основном для синхронных проектов (в общем то как и ПЛИС в целом). Их основная задача проследить, чтобы сигнал данных соотвествовал определенному клоку во избежание неправильной передачи данных (между регистрами или даже смежными чипами). Поэтому, как мне кажется, с помощью этих инструментов невозможно так точно ( 10 пс) задать время распространения сигнала. В основном таймквест отслеживает, чтобы данные приходили раньше периода тактовой частоты, так что точность получается в пределах 1нс. Из статей des00 вижу только вариант использования set max/min delay, но пока не понимаю как, ведь ячейки у меня зафиксированы, а если убрать фиксацию, то как написал выше, вряд ли получится такая же точность. Меня больше интересует, почему в почти одинаковых проектах квартус располагает межсоединения по разному?

-

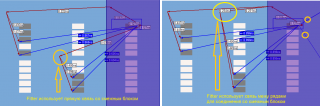

Во-первых, я как раз и хочу понять из каких соображений Quartus раскидывает межсоединения? Во-вторых, мне важно не минимальное время задержки между ячейками, а именно одинаковое. Я пытаюсь сделать задержку асинхронного сигнала с точностью меньше периода тактовой, для этого я использую чертыре фазы частоты для оцифровки асинхронного сигнала и их же - для формирования задержанного импульса. Quartus не позволяет размещать ячейки тактичуемые частотыми с разными фазами в одном LAB'е(те 0 и 180 можно в одном, а 90 и 270 - в другом) FPGA_ADC_TDC.ppt Определяю фазу асинхронного сигнала, как описано в статье, но кроме определения времени прихода асинхронного сигнала, я пытаюсь аналогичным способом сформировать задерженный импульс. Для этого как раз очень важно равное время распространения. Просто в версии, где задержки равные, у меня все получилось. Чуть изменил проект и уже точность получилась меньше..

-

Форумчане дорогие, ну неужели никто даже прокомментировать и на пути решения направить не может?

-

Altera: manual routing

Egor-ka опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день, уважаемые ПЛИСоводы. Столкнулся со следующей проблемой: Fitter по-разному размещает межсоединения, хотя ячейки назначены одинаково. Разница в двух проектах лишь в том, что левом - больше логики (расширен проект), а в правом - у ячейки больше выходов (Fan-out) Подскажите, пожалуйста, если кто-то встречался, как указать fitter'у использовать межсоединения для рядов, а не смежные? Мне требуется максимально выровнять задержку (как на правом рисунке). Возможно, есть другие способы? Использую EP1C3T100C6. PS. Прошу прощения - ошибся немного темой, нужно было в САПР... -

Спасибо, изучаю. Думал, может, кто-то из отечественных плисоводов это делал...

-

Здравствуйте, уважаемые ПЛИСоводы. Раз уж тут обсуждаются трюки на плис, Решил написать свою задачу Кто-нибудь пробовал использовать аналоговые свойства плис? Например, как ацп с помощью компаратора портов LVDS, формирование импульсов с точность меньше периода макс. тактовой частоты с помощью линии задержки. Сейчас пытаюсь сделать задержку сигнала с точностью меньше периода, в симуляторе получается, а в железе нет, хотя уже замучился вручную ячейки расставлять и времена распространения сигналов подбирать. Кто-то встречался с такими задачами? Спасибо.

-

Мне тоже, пожалуйста, производителя напишите?

-

А можно для тупых пояснить, что такое multicycle или falthpath констрейны и где о них почитать?:) Спасибо

-

Спасибо) Буду читать) Видимо, единственный источник - это мануал)

-

Варнинги есть и достаточно много) Я еще новичок в этих делах, поэтому не очень понимаю, как работает синтезатор и как управлять размещением. Поведение я смотрю по осциллографу.С SignalTap ни разу не работал(( Вот такие варнинги появляются: Warning: Found pins functioning as undefined clocks and/or memory enables Warning: Found node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew Warning: Can't achieve timing requirement Clock Setup: 'altpll1:inst|altpll:altpll_component|_clk1' along 242 path(s). See Report window for details. Warning: Can't achieve minimum setup and hold requirement clk along 1 path(s). See Report window for details. Critical Warning: Timing requirements for slow timing model timing analysis were not met. See Report window for details.

-

У меня похожая проблема (та что в сабже), только с пинами. Один и тот же сигнал вывожу на ножки с разных банков - на одном все хорошо работает, а на другом - то есть сигнал, то нет. И в зависимости от компиляции и размещения - такие проблемы, то появляются, то исчезают. Как быть?Что почитать?Может где про размещение хорошо написано? Спасибо) PS. Работаю на Cyclone

-

Verilog, RAM и Cyclone

Egor-ka ответил Egor-ka тема в Языки проектирования на ПЛИС (FPGA)

Спасибо огромное за советы! :a14: Буду разбираться))) -

Verilog, RAM и Cyclone

Egor-ka ответил Egor-ka тема в Языки проектирования на ПЛИС (FPGA)

А можно немного понятнее выразиться или дать ссылочку,где можно с этим корегенратором разобраться? PS. мне как начинающему, трудно понять этот сленг((( Вот упрощенный код: bit [11:0] memory [3647:0]; always @ (negedge ClkToADC) begin if((CountADC > 12'd133)&&(CountADC < 12'd3782)) memory[CountADC] = D; if (CountADC[11:0] == 12'd3782) Rdy = 1'b1; CountADC++; end always @(posedge ClkFromMC) begin DataToMC = memory[CntOutWord][CntOutBit]; CntOutBit++; if (CntOutBit[3:0]==4'd12) begin CntOutBit[3:0] = 4'b0; CntOutWord++; if (CntOutWord[11:0]==12'd3648) CntOutWord[11:0] = 12'b0; end end Буду очень признателен,если укажите на общие ошибки в коде. Есть ощущение, что вообще подход не правлильный...и кривой((( -

Verilog, RAM и Cyclone

Egor-ka ответил Egor-ka тема в Языки проектирования на ПЛИС (FPGA)

В настройках копмилятора точно стоит SystemVerilog-2005. А по поводу блочной памяти - я точно ее описываю не так, как требует кристалл...((( Просто я надеялся,что есть какие-нибудь еще методы описания блочно памяти)))) -

Verilog, RAM и Cyclone

Egor-ka опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день, помогите разобраться со следующей проблемой. Задача - принять данные с ПЗС ,слегка обработать их и отрпавить на микроконтроллер. Так как данных достаточно много, я хочу сохранить их в RAM, а затем обрабатывать. Проблема в том что, когда я создаю массив на verilog - bit [11:0] memory [3647:0]; - синтезатор (пользуюсь Quartus 7.2) очень долго все это дело обрабатывает, анализ и синтез проходят успешно, а во Fitter выдает ошибку, что в Cyclone 2,910 логических ячеек, а проект требует намного больше. Хотя в Cyclone 13 M4K RAM blocks (в общем 59,904 бита) - и этого должно хватить. Насколько я понял, проблема в том, что синтезатор хочет возпользоваться обычными регистрами логических ячеек, а не блоками RAM. Помогите, пожалуйста разобраться... Возможно, для использования M4K RAM blocks нужны специальные конструкции verilog? :smile3046: И еще... Почему когда я хочу сделать packed memory: bit [3647:0] [11:0] memory; компилятор выдает ошибку в этой строке: Error (10170): Verilog HDL syntax error at CCD1.v(15) near text "["; expecting an identifier Спасибо. -

Манчестер на Verilog

Egor-ka ответил Egor-ka тема в Языки проектирования на ПЛИС (FPGA)

Спасибо за пояснения. А не могли бы вы посоветовать книги начального уровня по верификации на Veriog, а также рекомендовать что-нибудь для понимания процесса синтеза HDL в ПЛИС? Было бы замечательноэтими документами еще и поделиться)))) Заранее Спасибо!