bedrive

Участник-

Постов

20 -

Зарегистрирован

-

Посещение

Весь контент bedrive

-

Вы знаете, поиск был вполне успешный. Просто, те кто хотели общаться по делу, писали в ЛС, а кому просто поговорить - сюда... Всем спасибо, тема закрыта.

-

Именно туда и нужно попасть.

-

Отправил информацию на почту.

-

Требуется разработать встраиваемое приемопередающее устройство (радиомодуль). Рабочий диапазон частот 120-170МГц Модуляция - АМ/ЧМ Прием и передача речевых и тональных сигналов Выходная мощность до 1Вт Чувствительность не хуже 0,2мкВ Размеры, не более 50х40х5 мм Радиомодуль должен быть выполнен в виде печатной платы с экранированной ВЧ частью. Все выводы с платы должны быть сделаны в виде торцевых полуотверстий, для дальнейшего монтажа модуля на другую плату по технологии SMT. Подробное ТЗ готов выcлать по запросу. Находимся в СПб. Связь через ЛС.

-

да, именно так

-

-

Давно это было... Я помню, что мне так и не удалось полдружиться с ALTLVDS, в результате я сам сделал сериалайзер и никаких проблем с DS90CF386 уже не испытывал. Микросхема работала без нареканий. Если есть необходимость могу покапаться - может найду свой сериалайзер.

-

Требуется опытный разработчик, СПб

bedrive ответил bedrive тема в Предлагаю работу

В первую очередь интересует работа в пределах Транзаса. Никаких "наездов" и "допусков" в "Транзас-Вижн". -

Требуется опытный разработчик, СПб

bedrive опубликовал тема в Предлагаю работу

Компании "Транзас-Вижн" (Санкт-Петербург, м. Василеостровская) требуется разработчик для создания устройств цифровой обработки видео для БПЛА. Задачи: - сжатие видео - стабилизация видео - сопровождение цели Необходимые знания и навыки: - опыт разработки устройств цифровой обработки сигналов - опыт работы с DSP не менее 3 лет - опыт работы с интерфейсом Ethernet - приветствуется опыт цифровой обработки видео - приветствуется опыт проектирования ПЛИС Дополнительные требования: - опыт работы 3-5 лет Обязанности: - подбор комплектации - разработка принципиальной схемы - разводка платы или руководство разводкой - перенос разработанного для РС программного продукта на DSP - тестирование и отладка - участие в испытаниях БПЛА Мы можем предложить: - конкурентную зарплату - комфортные условия работы - медицинскую страховку Резюме направлять по адресу: [email protected] -

Вы правы, кроме шуток... Магнитная буря мне все попортила, не иначе...

-

Проблема самоустранилась... Ничего не менял. Странно :07:

-

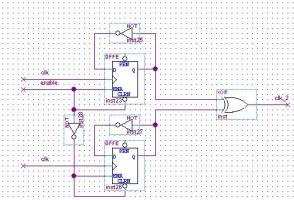

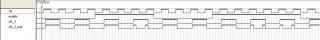

Синхронизован по заднему фронту, как на картинке. Просто я это на схеме не указал, извиняюсь.

-

Почему не работает схемка?

bedrive опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Может быть подскажете, почему в железе может не работать схемка (в приложении), которая прекрасно симмулируется. Смысл схемки в независимом делении входной частоты попалам при различных значениях сигнала enable. Т.е. если за время, когда сигнал enable = '1' случилось нечетное число тактов clk, то на выходе схемы при enable = '0' это не должно никак отразиться. Каждый раз при изменении сигнала enable деление должно начинаться сначала. Так вот. После прошивки наблюдал следующую картину (в приложении) - когда enable = '0' то все хорошо, а когда enable = '1' процесс деления может сбиваться, как будто происходит сброс триггера или изменяется частота clk. НО ни того ни другого я не вижу... Как так? =) Все тренировки на первом Cyclone -

Поглядим, спасибо =)

-

Спасибо, Vladimir, вы направили на путь истинный. Мы действительно толком не оценили задачу... Займемся сейчас этим, а после я надеюсь сформулировать вопрос конкретнее Спасибо большое всем.

-

Нашел на сайте Xilinx такое предолжение: Spartan-3E Display Development Kit На первый взгляд кажется подходящим. Буду изучать подробнее...

-

Для первоначальной реализации планируется взять алгоритмы без использования нейронных сетей.

-

есть задачи! на чем делать?

bedrive опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Есть интересная задача, а точнее целый круг задач, основой для которых является распознование объектов на видеоизображении в реальном времени. Хочется подступиться к этим задачам с помощью ПЛИС. Кто-нибудь брался за подобное? И какими средствами, есть ли подходящие для таких задач evolution board у Altera или Xilinx? Может посоветуете литературу? К сожалению, пока обпыт работы с ПЛИС ограничивается разработкой простого видеоконтроллера для небольшого ЖК-монитора на первом Cyclone, поэтому мне трудно сразу оценить сложность стоящих задач (понятно, что сложно, но насколько). Стоит добавить, что сами алгоритмы распознования разработаны и работают в качестве программных продуктов на PC. Теперь хочеться перенести это в "автономное" железо. Заранее спасибо за любые советы и подсказки. -

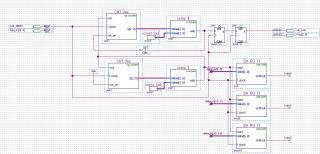

Вобщем пока ответов не последовало, опишу куда я продвинулся. Схема сейчас работает следующим образом: Одна PLL задействована для формирования сигналов развертки для экрана, вторая PLL дает "быстрый" и "медленный" клоки для altlvds_tx. Данный по 3 каналам выходят из altlvds_tx, клок для них беру со второй PLL (медленный). Временные диаграммы в симуляторе Quartusa вполне совпадают с теми, которые "хочет получать" вышеупомянутая микросхема, но .... Получить картинку удается далеко не всегда. Пока загружаю проект по JTAG, и желаемая картинка появляется один раз за 4-5 загрузок... Честно сказать не знаю что и делать, и где искать ошибку. :( PS Экран соединен с платой шлейфом шагом 1.27 длиной примерно 15 см. На выходе Cyclona стоят необходимые резистроры.

-

передатчик LVDS на Cyclone

bedrive опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Сущетвует необходимость организовать передачу данных (18 бит цвет + 3 сигнала синхронизации) с Cyclona по LVDS на следующую микросхему DS90CF364A (http://fulcrum.su/Read/CDROMs/NS/DS90CF32.pdf). Потенциально это кажется возможным, но при попытке реализации возникли проблемы. При использовании стандартной функции altlvds_tx не получается выбрать подходящую частоту tx_outclock (fitter пишет, что желаемая настройка для Cyclona недоступна ). Можно ли попытаться передовать данные (LVDS_DATA[2..0]) с выхода altlvds_tx, а тактирующий сигнал (LVDS_CLK) при этом брать со второй PLL? параметры передачи: data rate - 280Mbps deserialization factor - 7 LVDS_clk - 40 MHz