Lehin_05

Свой-

Постов

183 -

Зарегистрирован

-

Посещение

Весь контент Lehin_05

-

Altium Designer + 1С

Lehin_05 ответил uriy тема в Altium Designer, DXP, Protel

Не смогу, т.к. с меня только BOM в виде экселевской таблицы, а в 1С спеку заносят уже специально обученные люди. Просто как раз со слов этих людей, они просто импортируют таблицу, которую я им даю... -

Altium Designer + 1С

Lehin_05 ответил uriy тема в Altium Designer, DXP, Protel

Все видимо рано или поздно к этому приходят :) Мы тоже так хотим, но пока IT наши хотелки не реализовали. -

Altium Designer + 1С

Lehin_05 ответил uriy тема в Altium Designer, DXP, Protel

У нас это решено следующим образом: у компонента есть параметр (пусть DataBaseCode), значение которого берется из 1С. Значение этого параметра присваивается в нашей БД для Альтиум (DbLib). Поэтому при выгрузке BOM спецификация в 1С создается простым импортом таблицы из Альтиум. -

Проблема с backdrilling

Lehin_05 ответил Lehin_05 тема в Altium Designer, DXP, Protel

видео по этой теме -

Работает такой вариант! Спасибо!

-

Использование variants в multiboard

Lehin_05 опубликовал тема в Altium Designer, DXP, Protel

При сборке проекта multiboard все дочерние платы передаются без учета вариантов исполнения (variants). Может кто-то уже разобрался, возможно ли использовать в multiboard проекте конкретные варианты исполнения дочерних плат? -

Altium Designer 21

Lehin_05 ответил toshas тема в Altium Designer, DXP, Protel

Нет :( Теперь разделитель постоянно отображается (точка или двоеточие) даже если его не должно быть. Вот рукожопы :( -

Altium Designer 21

Lehin_05 ответил toshas тема в Altium Designer, DXP, Protel

-

Калькулятор импеданса для Альтиум реализован на основе софта Simbeor. Можно погуглить по этому софту и станет понятно, что это весьма продвинутый софт. Еще один "+" в сторону Альтиум, что результаты почти идентичны расчетам в софте Polar, а этим же софтом пользуются, например, в Резоните, поэтому расчетные данные должны быть максимально близки к реальным на плате.

-

Layer Stack Manager

Lehin_05 ответил Skat-pro тема в Altium Designer, DXP, Protel

Как бы приемственность должна быть между версиями. Если в 19 версии коэффициент положительный, то почему он в 20 стал отрицательным? Так то согласен, что это условность, но хотя бы можно было сделать акцент на этом, что "сейчас надо отрицательный". И если использовать именно профиль импеданса при положительном коэффициенте, то уже ерунда выходит. Это же элементарно делается "защита от дурака" - чтобы можно было вводить в это поле только отрицательное значение и все... А так сравнивал расчеты с поларовским калькулятором Cist25 (на Резоните именно Polar используют для проверки импеданса) - очень близкие результаты (в пределах допустимой погрешности) -

Layer Stack Manager

Lehin_05 ответил Skat-pro тема в Altium Designer, DXP, Protel

так вот как раз это и ошибка на скриншоте! Обратите внимание на Etch (inv) фактор. Он отрицательный, а должен быть положительный. На совместном форуме Альтиум и Резонит озвучивали этот фактор подтрава 2.4 для внешних слоев, 1.5 для внутренних. Если поставить положительный коэффициент, то W2 > W1 :) А ширина по профилю используется именно W1 И да, в 19 версии все правильно в этом плане, можно сравнить. -

Layer Stack Manager

Lehin_05 ответил Skat-pro тема в Altium Designer, DXP, Protel

вот спасибо :) Теперь буду дальше эти функционалом пользоваться. -

Layer Stack Manager

Lehin_05 ответил Skat-pro тема в Altium Designer, DXP, Protel

в LSM версии 20.0.9 встроенный функционал расчета импедансов не юзабелен, т.к. перепутаны значения W1 и W2 и, соответственно, при назначении профиля ширина проводника берется неправильная. А так из замечаний: не смог найти, как подгружать готовые заготовки стекапов. В 17 версии было удобно: сохранил наиболее часто используемые стекапы и подгружаешь их... -

2018 Вопросы начинающих

Lehin_05 ответил Sanchosd тема в Altium Designer, DXP, Protel

я так понимаю, что это для версии 20.0.9 (т.к. в 19 версии такого не было) ? Тогда предложенный способ не помогает. Так же искал, как избавиться от этого, но способ пока не нашел. -

Altium Designer 20

Lehin_05 ответил toshas тема в Altium Designer, DXP, Protel

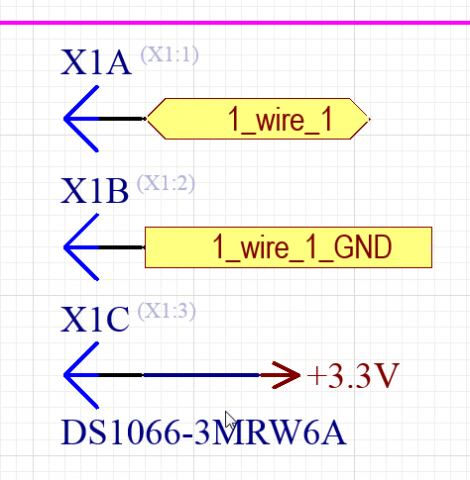

У кого как в схематике отображается сетка в виде точек? На скрине пример, как это у меня: сверху 20.0.8, снизу 19.1.8 У версии 20.0.8 точки не четкие и с каким-то сдвигом. Просто глаза в кучу от такой сетки :( Можно как-то настроить или что-то сделать с этим? (лучше отдельно открыть скрин, так понятнее) -

Спасибо :) На разных страничках состав ограничений отличается. Для Резонита, действительно, есть ограничение со скриншота )(0.35 и 0.25). Посмотрел несколько плат, которые в Китае делали (HDI), у всех зазор заливки 0.2 мм до металлизированных переходных без падов на внутренних слоях. Поэтому надо уточнять у конкретной фабрики ограничения.

-

Даже мысли не было кому-то что-то доказывать, просто передал слова технолога... А вот по табличке - очень интересно, т.к. сейчас в разделе техограничений на страничке Резонита нет ни слова про обведенное рамкой... Это какой-то старый скриншот или где можно найти данную таблицу?

-

Он вполне ясно выразился и говорил именно про техпроцесс изготовления таких отверстий. Т.е. именно для их завода не проблема сделать МПП с переходными, у которых нет неподключенных поясков на внутренних слоях и это не приводит к переводу платы в более высокий класс сложности. При использовании Tool - зазор прописывается в правилах. Например, для заливки при отступе 0.2 мм именно эти 0.2 мм и будет до металлизированного отверстия а не 0.2мм+поясок виа. По крайней мере AD19 сам перезаливает при отключении неиспользуемых падов до отступа 0.2 мм, а не оставляет заливку так, как будто этот поясок есть. А вот если сам завод удаляет в CAM350 не подключенный поясок, то да, заливка остается и просто увеличивается зазор до отверстия.

-

Главный технолог Резонита, отвечая на вопрос, нужны ли для переходных пады на внутренних слоях если они не подключены, ответил примерно так: "это вопрос больше религии, мы спокойно делаем переходные отверстия без падов в таких случаях"

-

Есть специальный инструмент: Tools - Remove Unused Pad Shapes... Удаляет все неиспользуемые пады как для Via, так и для Pads. Только потом, чтобы вернуть пад обратно, надо выделить такое Via/Pad и применить Restore unused - Selected only

-

Панель Properties раздел Selection Filter активировано Polygons ?

-

DDR3 flight time

Lehin_05 ответил MadMan M тема в Работаем с трассировкой

Наш программист перепробовал много разных способов вывода из Вивадо инфы про package length и во всех случаях генерится именно задержка (что на самом деле более правильно), а не длина выводов Это решение лежит "на поверхности". Пока так и сделано через перевод пс в мм используя значение 6.5 пс/мм. И данная инфа внесена на уровне паттерна простым действием "умная вставка" из Excel. Вопрос в другом: значение 6.5 пс/мм вряд ли соответствует действительности и получаем "относительные" длины внутри корпуса. Если бы Альтиум умел выравнивать трассы не в мм, а в пс, то вопросов бы вообще не было... Вряд ли тут требуется большая мощность вычислений. Стекап задан, Dk проставляется, скорость распространения сигнала в зависимости от материала можно запросить на фабриках. Типовых материалов не так и много, чтобы один раз сделать эту работу. А сейчас получается надо выровнять длину, потом симулировать и получать пс, а потом снова ровнять длину и т.д. -

DDR3 flight time

Lehin_05 ответил MadMan M тема в Работаем с трассировкой

Про Оркад и Экспедишн согласен, но речь именно про Альтиум (без вариантов). Про стек, слои, переходные и виа, сам материал платы и его свойства - все понятно. Вопрос больше по юзабельности этого самого Pin package length. Есть же проекты, например, тот же Zedboard, в которых эти длины внутри корпуса вообще не учтены и как-то платы работают :) Скажем так: стОит использовать хотя бы "относительную" длину или нет? Эта "относительная" длина делает примитивное выравнивание по длине всей трассы более точным или наоборот вредит? -

DDR3 flight time

Lehin_05 ответил MadMan M тема в Работаем с трассировкой

Подниму тему :) Сразу отмечу, что можно просимулировать время прохождения в том же Hyperlynx, но интересна именно метода и юзабельность в разрезе Altium Designer. Например, если взять Zynq XC7Z030SBG485, то из Vivado можно вывести список, где для каждого пина (кроме power разумеется) указывается Min Trace Delay (ps) и Max Trace Delay (ps). Для пинов DDR эта разница может составлять до 67 пс. Если брать DDR3-1600 от Micron, то рекомендуется разбег не более 10 пс. Пусть данный разбег взят с большим запасом и для 800 МГц разностью трасс внутри Zynq можно пренебречь, но сейчас речь немного о другом. Для Altium Designer можно учесть это время flight time, но только не в пс, а в мм/mil в виде параметра Pin package length. Допустим, все-таки необходимо учесть длину трасс внутри Zynq, как это сделать используя имеющиеся данные по задержкам? Для FR4 известно примерное время распространения сигнала - 6.5 пс/мм, а как вычислить длину внутри Zynq не зная скорости распространения? Можно, конечно, сделать очень оценочный расчет типа среднее между Max и Min Trace Delay поделить на 6.5 пс/мм и получить "относительную" длину трасс внутри Zynq, но насколько эти значения будут близки к реальности? -

Да мне просто даже интересно стало, человек зачем-то сделал данную работу. А вдруг были аргументы. Но скорее всего это связано с ограничениями среды разработки (для выравнивания длины учитывается полная "физическая" длина трассы, включающая участок до терминатора). Повторение никогда не помешает :) В данном случае было интересно, вдруг что-то изменилось в стандартах и теперь надо делать так. Спасибо за отклик :)