-

Постов

317 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные McSava

-

-

Скорее всего дальше будут зажимать гайки ещё больше, так что пора придумать на чём работать дальше. Можно приобрести лицензию на что-то свежее.

Правда лицензия на тот же Altium или PADS для себя одного довольно дорогие.

как вариант http://diptrace.com/ua/buy/online-store/ даже в Фулл версии вполне подъёмная цена, если её по кусочкам заложить в каждом проекте сразу.

Правда переходной период может навести на мысль бросить фриланс и уйти туда где работодатель будет думать где брать лицензию. Ну и с ним вместе можно думать, что вот эта опция в лицензии нам нужна всего один раз на десять плат, поэтому мы её возьмем в плавающем варианте, а на каждый день подпишемся только на самое необходимое. Это экономит хорошо экономит бюджет отдела. А к просьбам "выйди на минутку, ты захватил лицензию Pro/Plus" быстро привыкаешь. Зато всё по честному.

-

а вот об остальных ограничениях где можно почитать?

в документации на микросхему, или в предупреждениях об ошибках компилятора.

Альтера, к примеру, не позволяет использовать LVDS интерфейсы рядом с обычными контактами, но там это дело можно обойти. Не каждый банк в Альтере имеет внутренние резисторы и ещё много чего там может быть.

Поэтому только методом проб и компиляций, с поиском по документации.

-

Да подсоединять 1,8 к банкам с 2,5 и 3,3 можно. Но лучше откомпилируйте проект в этой части, чтоб не оказалось, что можно только при условии, что у вас остальные контакты используются для входа или только для выхода, или при таком напряжении питания банка вы не сомжете задействовать внутренние согласующие резисторы 100 Ом. И ещё полно там всяких ограничений может быть.

-

А как же данные по mgt/pci с AC-связью?!

Для mgt/pci-e с AC-связью используется специальное кодирование передаваемых данных типа 5b/6b, 8b/10b, 128b/130b или другое.

Закодированный сигнал будет с меняющимися состояниями на линии передачи, без длинных последовательностей 0 или 1.

Существуют АЦП/ЦАП с интерфейсом для подключения к mgt - JESD204 - SERIAL INTERFACE FOR DATA CONVERTERS. На данный момент есть ревизия В этого стандарта. За более новые версии не знаю.

-

Добрый день.

Возникли вопросы по использованию IOD и Altera.

1. CLOCK сигналы. У Altera есть CLK и DCLK.

Сигналы с контактов CLK-типа, можно завести на PLL. Сигналы с контактов DCLK-типа завести на PLL не возможно. Но и те и другие сигналы можно завести на глобальные тактовые цепи внутри ПЛИС.

В IOD контакты обеих типов (для Cyclone IV E) указаны как CLOCK. В проекте есть несколько сигналов которые заведены на вход CLOCK, но не всем необходима возможность заведения сигналов на PLL.

После SWAP'a сигналов и автоматических unravel сигнал с входа CLK попал на DCLK, при проверке глазами я это упустил. Теперь, в уже сделанной плате, я не могу (без перепайки и проводочков) завести основной сигнал на PLL.

Вопрос как можно защитится от этого в будущем, задавая параметры сигнала в IOD, но с вожностью разрешить делать SWAP в случае необходимости между сигналами CLK, но с запретом на DCLK?

2. У Altera есть сигналы GND с типом сигнала GND и GNDAALT с типом сигнала AnalogGND.

Можно ли их объединить в одну цепь GND, так чтобы при обновлении схемы из IOD контакты GNDAALT автоматически не отрывались от цепи GND и не назначались на цепь GNDAALT? Снятие галочки в установках проекта "Автоматического подсоединения оставшихся контактов к цепямь PCB" не помогает.

Назначение сигнала GND на контакты GNDAALT так же не помогает.

И попутный вопрос по Xilinx. Для некоторых неиспользуемых контактов Xilinx рекомендует подсоединять их к цепи GND, например для гигабитных приемопередатчиков: "• If a receiver is not used, connect the associated pin pair to ground." Просто взять и назначить эти контаткы на цепь GND в IOD не получается. Приходится доделывать руками, но если в схему вносятся обновления, то эти цепи снова ставноятся неподключенными к цепи GND.

Существует ли способ задания неиспользуемости контакта и подсоединения его на цепь GND? "Резисторы + имя цепи" использовать не хочу.

-

Насколько я знаю, то у мастера на шине на шине не обязательно должно быть несколько клоков.

Про много клоков скорее всего речь идёт для системного устройства.

И у системного устройства действительно может быть несколько клоков, сигналов прерывания и других, которые идут к каждому слоту (устройству) на шине отдельно.

Если речь идёт о Master/Target устройстве то оно все равно тактируется от системного контроллера шины, и если при загрузке оно правильно не ответит, то системный контроллер PCI может снять с этого слота клок.

-

На Интуит.ру был курс по WEC. Там основы, но по старой версии в основном.

Для написания програм и компиляции нужно дополнение к Visual Studio в виде Windows Embedded Compact 7 или Windows Embedded Compact 2013.

Версию Visual Studio нужно подбирать под ту весию WEC которую вы хотите использовать.

Дополнительно почитать можно на msdn.

-

В приведенном даташите используется режим LVDS c удвоением частоты следования данных (изменение по обоим фронтам) при той же частоте тактового сигнала с АЦП.

Мы использовали многоканальные АЦП где частота следования данных в 6 или 7 раз больше частоты дискретизации. Так вот у некоторых младших микросхем ПЛИС невозможно завести клок такой частоты на цепи тактирования. Это нужно учитывать.

Если мне не изменяет память, то был случай с невозможностью работать на указанной частоте микросхем первой ревизии, о чем производитель выпустил позже ERRAT'у, но платы были спаяны.

Ну и в наших платах почти всегда был клок с PCI, PCIe или отделный внешний, а уже внутри делались согласования клоковых доменов.

-

В стандарте PCI Local Bus Specification Revision 3.0 в самом начале есть перечень изменений в стандарты.

2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed add-in cards 3/29/02

3.0 Removed support for the 5.0 volt keyed system board connector 8/12/02

Основное отличие от PC104+ тип разъёма (геометрия плат). На софтоовом уровне не могу сказать.

-

Можно. Но если АЦП нужно конфигурировать, а вы собираетесь подавать тактовую частоту АЦП в ПЛИС на PLL, то могут быть проблемы.

Если в ПЛИС после конфигурации АЦП делать сброс PLL/DCM, то все проблемы решаемые.

Если используемая АЦП с последовательным выходом и выдает тактовую частоту не входную, а выходного потока, то нужно смотреть, чтобы её можно было запустить на клоковые цепи внутри ПЛИС.

-

Мы использовали эпоксидку и в качестев наполнителя вольфрамовый порошок. Резины и мягкие полиуретаны не использовали, скорее из-за их отсуствия.

Причем у нас было несколько помолов вольфрамового порошка. Вольфрам выбирался из-за его большой плотности. Порошок - для рассеивания.

Соотношение подбиралось эмперически. Но когда подобрано, то потом делали "по рецепту" на 1 кубик смолы, Х.Х грамм порошка.

Когда стали применять "равномерную" керамику, то датчики получались примерно одинаковые. На некачественной керамике (с неравномерными характеристиками от пластины к пластине) датчики выходят неравномерные. У нас даже был самопалный стенд с входным контролем креамики и сортировки по праметрам.

На сколько помню ставилась задача для дефектоскопии отдельно, для толщиномера отдельно. Для измерения малых толщин нужно было более сильное демпфирование.

-

Мы решаем подобную задачу с помощью шлюзов и устройства SIM-банк.

Если у нас есть задача просто отправлять сообщения, то необязательно, чтобы количество портов соответствовало количеству SIM карт. Мы просто перебираем карточки на несколько шлюзов (GSM-модемов). В ПО можно ограничить, на какие номера можно отправлять СМС, на каие нет (по оператору или по стране).

Можно задать ограничение количества минут и сообщений для каждой SIM карты. Остальных фишек я не знаю, так как занимался только железной частью.

-

У вас, скорее всего, все компоненты с одной стороны. У меня для всех элементов на верхней стороне в колонке указано NO, а для нижней YES. Может быть это для точки с клеем, а может что-то ещё.

Я точно не знаю, а документация далеко.

-

У них был с DigiKey совместный проект, но вот под PADS или xPedition не скажу.

А так да нужно всё делать самому.

-

В 8b/10b кодировании есть признаки старта / стопа сообщения и синхронизирующие сообщения. Там это сделано для того чтоб подстраивать PLL для извлечения синхросигнала из данных, и получаем сигнал из неповторяющихся длинных последовательностей из "1" или "0".

Но этот принцип можно использовать для выбора протокола и по UART.

За счёт избытоного кодирования, все вариации восьмибитных данных закладываются внутрь 10 битных посылок. У нас появляются никогда не встречаюся комбинации, в них и вкладываются служебные признаки.

Удобно ли конкретно этот протокол, вкладывать в скорости UART - не пробовал, всё таки разработан он немного для других вещей.

-

... но если я с AVR хорошо знаком, и на ARM (STM32,NRF51) кое-что писал, то c MPS430 прийдется изучать с нуля. Не хотелось бы, если честно ...

MSP432 - ARM, RTOS + плюшки ввиде низкого энергопотребления и прочего

-

Если точность не требуется, то можно взять СС3200: Wi-Fi + MCU в одном флаконе. У него есть возможность включения АЦП и управление реле.

Некоторые измеряют потребляюмую мощность со всего дома одной отладочной платой.

-

Если загрузчик не стартует, проверьте поднимается ли питание 1,2 В, и 1,9 В, которое делается внутренними преобразователями.

Запускаются ли генераторы, 32 кГц и 40 МГц.

Если их нет, то скорее всего проц на замену. По крайней мере у меня так было. Я доигрался с отсладкой, после чего проц перестал стартовать и прошиваться (не отвечает на запрос в UniFlash).

Были варианты или спаленные преобразователи по цепям от FTDI или процессор. Оказалось процессор, который после перпайки - заработал.

По-поводу восстановления loadera не скажу, так как не стали с этим возится. Может быть можно сформировать все питания внешними источниками и зашить его через JTAG, но этот вопрос скорее всего нужно на e2e.ti.com спрашивать.

-

Там дальше в даташите есть схемы для других видов схем согласования с ОУ и вообще без ничего. И описание преимуществ той или иной схемы.

Мы для 904 ставили один ОУ.

-

Если устройство присутствует на шине, то да должны видеть устройство без драйвера. И при загрузке BIOS должно присутствовать устройство в перечне устройств.

Проверьте не перепутались ли стороны Aх и Вх разъёмов пока вы ставили переходник. И не перепутаны ли Rx/Tx (Rx одной платы должны приходить на контаткы Tx другой платы). Если это стартер кит, то там есть возможность выбирать сигнал CLK с разъёма PCIe (100 MГц), 125 МГц с генератора на плате или с пары SMA разъёмов.

Если в проекте вы тактируетесь от разъёма PCIe попробуйте перключится на 125 МГц с генератора. И посмотреть, что и как.

-

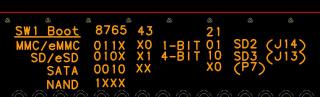

Если вы имеете ввиду аппаратные вещи, то в этом процессоре можно выбирать откдуа грузится, то это выбирается значением на контатктах во время загрузки процессора.

Есть два контакта BOOT[1:0] которые отвечают за выбор, того откуда идёт выбор загрузочного устройства - из внутренних электрических прожиагемых "предохранителей", SERIAL или задается отдельной группой контактов на плате.

Мы на своей плате делали надписи на слое шелкографии, что за что отвечает.

По отличию запуска процессоров у Freescale/NXP был документ по правильному подключению питания процессоров. И Для Q и D есть отличия в схеме питания.

Но в графе для iomux tool указано что регистры настройков выводов для Q и D идентичны.

Правда сборкой проекта загрузчика я не занимался и подводных камней не знаю.

-

У Тexas Instruments есть документ Using the TPS62150 as Step-Down LED Driver With Dimming

62150 он одноамперный, но можно взять 62130 - он 3А.

У других производителей также есть подобные доукументы.

Плюсы - меньше греется, минусы - нужна индуктивность (это доп размеры).

-

Раньше начало рекламного блока можно было искать в служебных строках вместе с телетекстом. Его использовали для вставки региональных рекламных блоков.

Передается ли эта информация сейчас, а тем более доходит ли она до трансляции по HDMI - не знаю.

-

На оверах есть тесты блоков питания.

Там есть стенд и вы можете посмотреть как примерно всё сделано. И там же где-то был обзор самого стенда.

MG Expedition ликбез ...

в Siemens EDA - Xpedition, PADS (ex. Mentor)

Опубликовано · Пожаловаться

уменьшили ширину дорожки на 0,1 мм и увеличили зазор на 0,1 мм. Положение центров трасс не должно изменится.

При увеличении ширины трасс можем не пройти по зазорам другим трассамили компонентам.

У самого сейчас стоит подобная задача.