beles

Участник-

Постов

14 -

Зарегистрирован

-

Посещение

Репутация

0 Обычный-

После нескольких опытов с разными PHY от MARVELL, SMSC, AMD выяснилось что ни одна из них не реагирует на запросы с нулевым адресом (PHY_addr), при этом команды формировались как с FPGA (Spartan3E, Virtex5) так и с помощью процессора. При этом если задать адрес физики. заданный с помощью конфигурационных ножек (отличный от нуля), то все работает правильно. Может быть PHY не должна отвечать на нулевой адрес, если её назначен другой адрес?

-

> при включении phy по умолчанию на 10Мбит настроена при включении у физики по умолчанию вытавлен режи опрделения скорости текущего соединения, как раз с помощью конфигурационных ног, по этому и выставлял скорость 10Мбит, т.к. подключал к 100 или 1000 Мбитной сети. Все, разобрался, но не совсем. Физика реагирует на запосы подаваемые только с её адресом "00111", а на запрос с адресом "00000" не отвечает. Хотя в документации "Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide.pdf" (UG194) указано следующее: The PHYAD field for an MDIO frame is a 5-bit binary value capable of addressing 32 unique addresses. However, every MDIO slave must respond to physical address 0. Почему в данном случае физика не реагирует на нулевой адре пока не понятно, буду разбираться...

-

Использую отладочную плату от Xilinx ML507, физика Marvell 88E1111, плисина Virtex5 FX70T. Так же пробывал на плате "Spartan-3E Starter Kit" с физикой SMSC LAN83C185, результат такой же, то есть реакции на команды не наблюдается.

-

Попробывал сделать как вы предложили, но конфигурировал на 10Мбит, не получилось. И зачем вы два раза подавали команду? первый на конфигурирование 100Мбит, а втрой на Reset + 100Мбит, разве после ресета все настройки физики не сбросятся? И производили ли вы чтение регистров?

-

да, для этого нужно выставить сигналы на REV_SEL[1:0] 00 - 1 прошивка 01 - 2 прошивка 10 - 3 прошивка 11 - 4 прошивка

-

Здесь все написано Platform Flash PROM User Guide (UG161). Можно использовать до 4 прошивок, выбор которых осуществяется по сигналу REV_SEL[1:0]. Желательно по нулевому адресу хранить заведомо правильную прошивку, тогда если прошивка с другого адреса (1,2,3) не загрузится по какой то причине, то автоматически будет загружена прошива с нулевого адреса. Насколько я знаю переконфигурирования части FPGA не возможно.

-

Управление PHY через MDC/MDIO

beles опубликовал тема в Работаем с ПЛИС, области применения, выбор

Необходимо сделать проет, который бы читал/записывал данные из внутренних регистров PHY, при этом использовался бы интерфейс MDC/MDIO. При подачи этих сигналов в режиме чтения физика ни как не реагирует. Сигналы формировал согласно стандарту. Тактовый сигнал менял от 25кГц до 3МГц, но реакции ни какой. Смотрел осциллографом, сигналы до физики доходят такие какие я подовал, после перехода в Z состояние и начало приема, на сигнале MDIO постоянно весит "1", т.к. на плате этот сигнал подтянут к питанию. Адрес физики использовал 0 (стандартный) и 7 (таким она хардово сконфигурирована), адрес регистра ставил любой (менял), реакции тоже ни какой. Подскажите в чем может быть проблема? -

to Doka попробуй очистить проект "Cleanup Project Files", пересохрани ucf-файл и запусти имплементацию заново

-

Кто работает в Xilinx ISEv10.1 ?

beles опубликовал тема в Среды разработки - обсуждаем САПРы

При добавлении в проект ядра ChipScope время имплементации сильно увеличивается, может, кто знает, как решить эту проблему? -

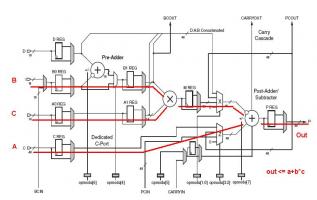

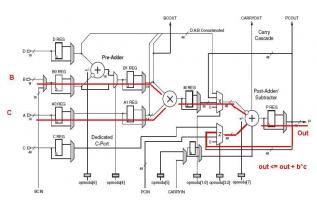

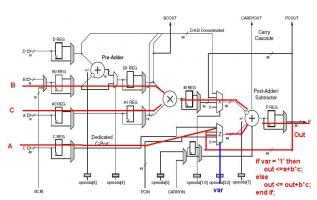

to atlantic попробовал приведенный вами пример, ничего не изменилось, сумматор и умножитель синтезируются на одном DSP, а мультиплексор на Lut. to des00 интересный вариант, но не очень универсальный, придется создать какую нить библиотеку или пакет, в которых разместить эти компоненты, и эту библиотеку необходимо будет подцеплять к новым проектам. К тому же структура DSP блоков отличается, так на DSP48A можно реализовать out <= c + a*(b+d), (в нем 2 сумматора и 1 умножитель), а вот на одном DSP48 такое реализовать не получиться (1 сумматор и 1 умножитель). Думаю, что кодом полностью описать возможности DSP нереально, например, если создавать умножитель 16х16: if rising_edge(clk) then p <= a*b; end if; то синтезатор заменит его одним DSP, но при этом задержка от входа до выхода (latency) будет 1 такт, если же использовать DSP в явном виде, то эту задержку можно выставить равной 2 или 3, при этом тактовая частота проекта значительно возрастет. Внутри DSP сигнал проходит через сумматор(торы) умножитель и мультиплексор(соры), и желательно эти внутренние блоки отделить друг от друга триггерами. Думаю самый практичный вариант использовать все же коргеновские блоки + внешнюю логику, во-первых, удобно переносится, а во-вторых, проекты, в которых используются все 100% Slices, редко встречаются, и практически всегда есть свободное место.

-

Немножко не понял к чему этот ответ. Приведенные вами примеры вообще не реализуемы на ОДНОМ DSP блоке. (может я и не прав). Мне нужно узнать как не используя вставки примитивов, можно описать эти примитивы на VHDL, а потом уже синтезатор сам заменил их на нужные, в зависимости от типа плисины. Для пояснение приведу три примера, первые два синтезатор заменяет DSP без доп.логики, а с третьим этого делать не хочет, обязательно вставляет дополнительные slices, хотя по картинке видно что это можно реализовать и без них. out <= a + b*c; out <= out + b*c; if var = '1' then out <= a + b*c; else out <= out + b*c; end if;

-

Как описань на VHDL блок DSP48 ?

beles опубликовал тема в Языки проектирования на ПЛИС (FPGA)

При реализации проекта интенсивно используются DSP блоки, при этом в модули они вставляются ручками, потому что алгоритм их работы не получается создать в коргене. После завершения проекта на Virtex4 необходимо его перенести на Spartan-3AD. Блоки DSP48 в этих плисинах разные и придется подгонять новые блоки (DSP48A) вручную. Может есть способ точного описания DSP с помощью VHDL. Пробовал следующие примеры: out <= a + b*c; -- синтезируется нормально, с использование одного DSP out <= out + b*c; -- тоже все в порядке а вот такую конструкцию он синтезирует с применением дополнительной логики if var = '1' then out <= a + b*c; else out <= out + b*c; end if; хотя если описывать DSP блок руками, то эта конструкция умещается в один DSP без дополнительной логики, просто сигнал var задает правильный opmode. В настройка синтезатора принудительно ставил использование DSP побывал использовать атрибут attribute use_dsp48: string, тоже не повлияло на результат -

Я бы тоже не отказался от ссылок на такую информацию. Может у кого есть.

-

Здравствуйте, не подскажите где можно скачать МИЭТовские лекции, точнее иститута созданного совместно с cadenc, список предметов которых там читаются расположен гдето выше. У кого есть чтото подобное пошу откликнуться