slawikg

Свой-

Постов

144 -

Зарегистрирован

-

Посещение

Весь контент slawikg

-

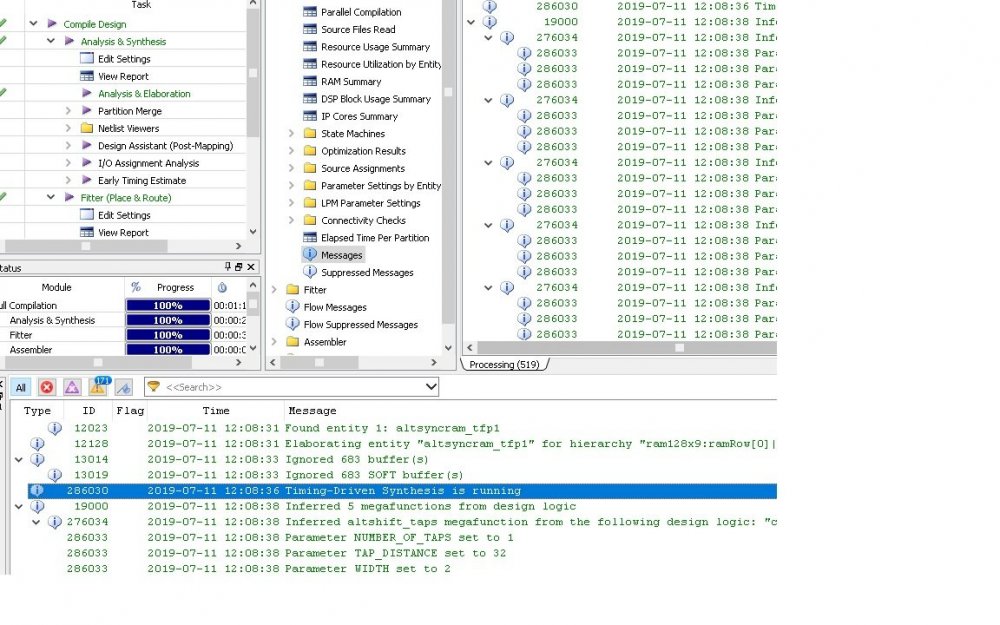

П очистил и удалил, всё осталось по прежнему. Но попробовал констрэйн set_max_skew в другом проекте, заработал, прошла компиляция нормально.

-

Несколько раз стирал и даже помогало, завтра попробую ещё раз. Вообще то кто пробовал set_max_skew и в какой версии квартуса?

-

Не работает констрэйн set_max_skew

slawikg опубликовал тема в Среды разработки - обсуждаем САПРы

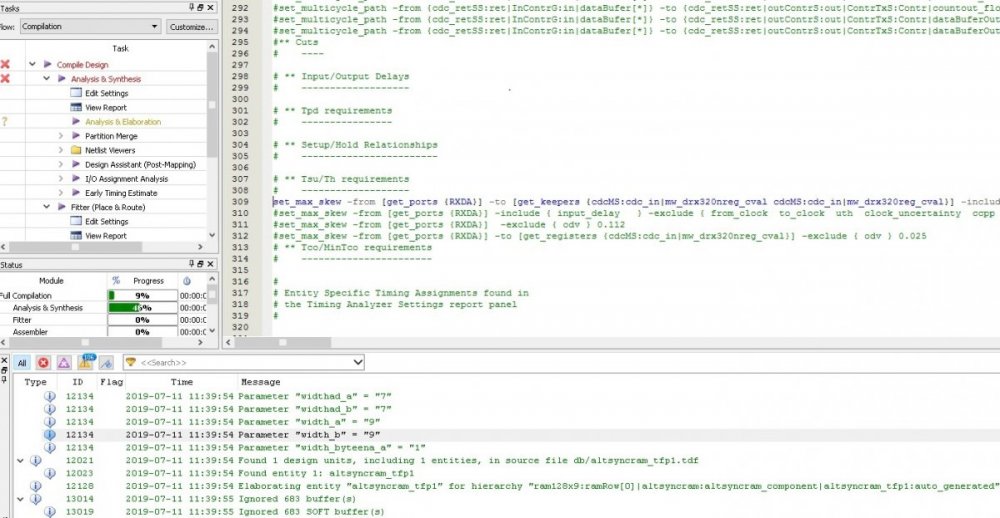

При установке в sdc файл констрейна set_max_skew . который был проверен, таймквестом ( старт таймквест) : set_max_skew -0.070 0.000 0.070 [get_ports {RXDA}] [get_keepers {cdcMS:cdc_in|mw_drx320nreg_cval cdcMS:cdc_in|mw_drx320reg_cval}]-include { input_delay } -exclude { from_clock to_clock uth clock_uncertainty ccpp odv }, quartus завершает анализ и синтез с внутренней ошибкой. Если закомментировать констрейн, то quartus выполняет с компиляцию до конца. На рисунке ниже выделена строка на которой прервался синтез с установленным констрэйном. Quartus 13.1 в виндовс 10. Циклон 3. Как заставить Quartus работать с констрэйном set_max_skew?. Собственно мне нужно объяснить Quartusу , чтобы выровнять задержку от входа RXDA до триггеров mw_drx320nreg_cval и mw_drx320reg_cval. Триггера синхронизируются от заднего и переднего фронта клока частотой 320 Мгц. -

Ещё раз,спасибо!

-

А в какой это версии Гиперлинукса, у меня 8.21

-

Большое спасибо Fill!

-

Извиняюсь, Гиперлинкс.

-

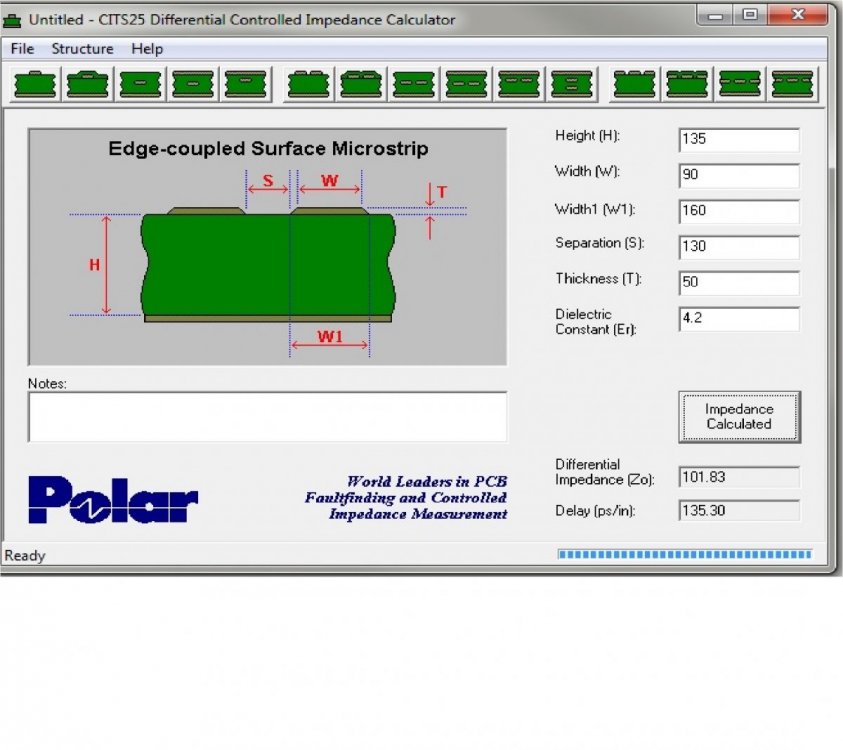

Спасибо, не понятно какой etch factor в Гиперлинуксе и как его там поменять? В POLAR он определяется соотношением W , W1 и Т.

-

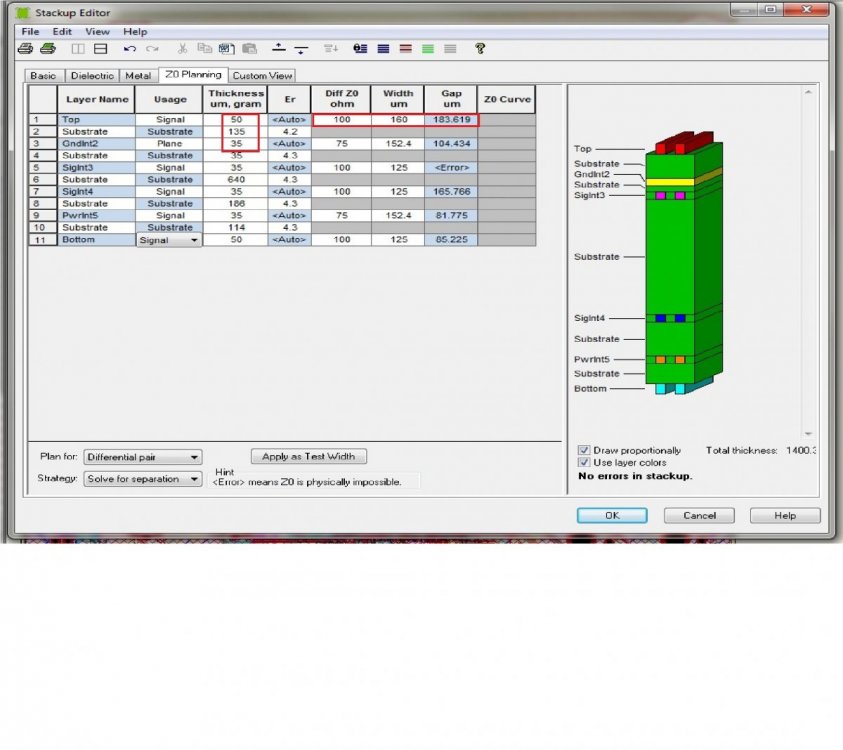

Добрый день! Почему получается разность в расчётах диф пары между POLAR, и Гиперлинукс. На первом рисунке (Гиперлинукс) 100 Ом получается при толщине линии 160 мк ипри промежутке мжду линиями 183 мк. На втором рисунке (POLAR) 100 Ом получается при толщине линии 160 мк ипри промежутке мжду линиями 130 мк. Кому верить?

-

Спасибо, вы меня выручили! Я думал что эти скрипты запускаются автоматом. Сейчас запустил скрипт и, после компиляции ОСТ отключились! Там ещё есть скрипты может их тоже надо запускать отдельно?

-

Всем здравствуйте ! На плате установлены терминирующиие резисторы + OCT, получается слишком болольшой номинал последовательного резистора. OCT ставиться автоматом, а в ассигмент едиторе отключить не получается. Каким образом можно ещё отключить последовательный резистор?. Заранее благодарен!

-

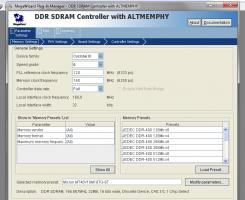

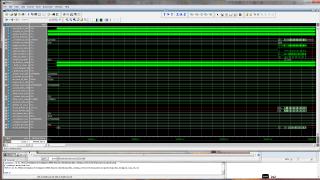

Всем здравствуйте ! Из example_top, сгенерированного мегавизард, создал проект в quartus 13.1. Проект успешно скомпилировался и разведён. Далее линком из quartus запускаю на симуляцию в questasim. Test_bench, сгенерированн в мегавизард. В симуляции иницализации вроде бы выполняется, я так понимаю проходит инициализация памяти, тестовая запись и во время тестового чтения всё переходит в неопределённое состояние, в результатене не вырабатывается сигнал init_done. 1. Так нормально, больше ничего не добьёшся и нужно продолжать работать дальше или это признак неработоспособности корки?. 2.Может это связано с опеределённой версией корки и квартуса , 13.1 у кого как. 3. Как можно исправить поведение корки?. Заранее благодарен! С Рождеством!

-

Приветствую! Всех с новым годом! Заменил стандарт IO С sstl на 2.5 V для синхросигналов mem_clk, mem_clk_n, сообщения пропали ну а на входе микрона сигналы посмотрел с помощью осциллографа, вроде соответствуют стандарту sstl-2.

-

Ошибка корки ddrsdram контроллера.

slawikg опубликовал тема в Среды разработки - обсуждаем САПРы

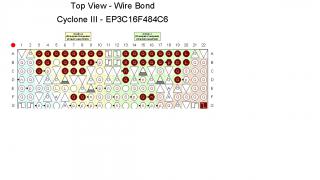

Всем здравствуйте ! При компиляции example проекта с коркой DDR SDRAM Controller with ALTMMPHY CYCLONE3 получаю собщение об ошибке QUARTUS13.1. 16 бит данных DQ0-DQ15 и DQS размещены в банке 8. Адресные и контрольные сигналы размещены в банке 7, в котором размещен VREF pin, указанный в сообщение. 16 бит данных DQ0-DQ15 и DQS размещены в банке 8. Адресные и контрольные сигналы размещены в банке 7, в котором размещен VREF pin, указанный в сообщение. Я так понимаю, VREF pin появились в этом банке появились из-за синхросигналов mem_clk, mem_clk_n, которые которые номинально bidir , в проекте же они используются как выходы . А выходы sstl вроде не требуют VREF. Искал во всех мануалах, но нигде не нашёл ограничений на размещение в зависимости VREF! Как можно избавиться от этой ошибки не изменяя расположения сигналов? -

Скрипта моделирования в папке нет: конечно можно из проекта квартуса создать такой скрипт, я раньше так и делал, возможно воспользуюсь вашим советом. Без процессора

-

Скрипт собственно формирует HDL Disainer, он приведён на первом рисунке в сообщении 1.Там под красными сообщениями об ошибках компиляции из за отсутствия "ieee", приведено сообщение ошибке выполнения скрипта. Чтобы посмотреть диаграмму входных сигналов в корку и её ответов контроллеру, прежде чем вставлять в проект.

-

Библиотека "ieee" в HDL Disainer

slawikg опубликовал тема в Среды разработки - обсуждаем САПРы

Всем здравствуйте ! Для моделирования альтеровской корки DDR SDRAM, квартус 9.1, из файлов полученных при генерации корки в мегавизарде собираю проект в HDL Disainer HDS_2015.1b, файл верхнего уровня "ddr_example_top_tb", но при попытке запустить на симуляцию, и на стадии компиляции получаю соообщение о том что библиотека "ieee" отсутствуеет, хотя в проекте HDL Disainer она есть. При этом проект ddr_example_top в квартус полнустью проходит. Как скормить библиотеку "ieee" HDL Disainerу и questasim_10.1b!? -

-

Пытаюсь сделать отладчик ULINK 2 из девборды MCB2140 с процессором LPC2148. З агрузил прошивку ULINK2-V2.01 , взятую на форуме Easyelectronics.ru • с помощью FlashMagic. Keil MDK-ARM 5.21a пытается обновить прошивку и зависает. Толи нельзя вообще нельзя так делать , толи прошивка не та? Может есть у кого та прошивка? Если установить CMSIS-DAP адаптер вроде определяется, правда не знаю будет ли работать с контроллером 1986ВЕ3, пока нет платы и проверить не на чем. ULINK2_V2.01.rar

-

Подключая кабель вы соединяетесь с землёй компьютера, поэтому проверьте нули и питание.

-

Лечиться откаткой проекта, вообще надо создавать больше архивов.

-

Большое спасибо вам Fill! Цепи разводятся!

-

Дико извиняюсь но ни в роутере и ни в layout pads 9.5 такой команды не нашёл

-

Не понятно как это сделать , не нашёл термина Rescedule в падс