Костян

Свой-

Постов

690 -

Зарегистрирован

-

Посещение

Весь контент Костян

-

я был не уверен, что это правильно.

-

частичная выборка индесков на Verilog.

Костян опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Дано регистр reg [40*8-1:0]dataPacket Необходимо перебрать следующие его биты [7:0] [15:8] и т.д. как записывать эту комбинацию понятно for (i = 0; i <= 39; i = i + 1) какойТоРегистр <= dataPacket[8*i+:8]; Как записать другие комбинации ? [3:0] [11:8] [19:16] и т.д. Верно ли решение ? for (i = 0; i <= 39; i = i + 1) какойТоРегистр <= dataPacket[8*i+:4]; И совсем не понятно мне, как сделать последную комбинацию [7:4] [15:12] [23:20] и т.д. for (i = 0; i <= 39; i = i + 1) какойТоРегистр <= dataPacket[4+8*i+:4]; -

это только пины двойного назначения. вы еще с алтерой не работали , там половина портов не имеет терминаторов.

-

-

спасибо , именно подобная статья и интересовала.

-

Подскажите литературу или схему деления на полином с параллельной загрузкой входных данных произвольной разрядности. Классическая последовательная побитовая схема не подходит.

-

Обнаружение в канале связи битовых ошибок

Костян ответил Костян тема в Математика и Физика

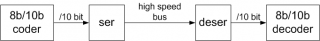

верно, второй источник ошибок - импульсные помехи в данном случае не пройдет. так как 1 бит ошибки в закодированном при помощи 8b/10b превращается в целый байт ошибки, в этом то и вся проблема, что в канале передачи не чистая информация, а пройденная через кодер 8b/10b и я не могу подсчитать четность в каждом слове. решение прежние - ловить пачку ошибок длинной 2 байта. Хитрость со структорой 8b/10b не пройдет, в патенте есть связь кодера 3b/4b на всю схему 8b/10b :-( -

Обнаружение в канале связи битовых ошибок

Костян ответил Костян тема в Математика и Физика

спасибо, с возможностями кода разобрался. Но в процессе появилась другая идея. В данном случае возможно прийдется обнаруживать пакет не 8бит ошибочной информации, а всего лишь 5, так как 8b/10b является по своей сути суммой между 5b/6b и 3b/4b. Но для окончательного выяснения этой идеи, мне нужно еще раз пересмотреть патент на 8b/10b весьма верное замечание. -

Обнаружение в канале связи битовых ошибок

Костян ответил Костян тема в Математика и Физика

т.е может показать как отсутствие ошибок , так и неверно указать ошибочный байт ? -

Обнаружение в канале связи битовых ошибок

Костян ответил Костян тема в Математика и Физика

8b/10b может определить только неверную полярность . разве он может определять символьную ошибку ? кодер на логике(не табличный) даст неверную комбинацию и будет разбирать следующий байт как ни в чем не бывало. Кроме того, я пока затрудняюсь , как вычислить вероятность правильного обнаружения декодером 8b/10b неверной полярности сигнала. Подозреваю она будет всего ~75%, что есть очень плохо. достаточно определить битый байт. исправлять пока не планирую. дело в том, что хоть один, что 2 бита ошибки в канале в 8b/10b кодеровке приведет к ошибочному байту после декодирования. поэтому достаточно найти код, котрый будет определять (не исправлять) 1 байт . более точное название не подскажите ? Либо подскажите название литературы. Решение впринципе нашел - код Файра. циклический и простой в реализации ээ..не, слишком просто, да и не хочется терять целый пакет, при потере всего 1 бита !. Передавать заново пакет не имею возможности, канал связи и так на пределе своей пропускной способности, могу выделить только 2..3 байта на кодировку. Будте добры, поясните ключевой момент, который я не до конца понимаю. Что скажет декодер в данном случае, если количество ошибок будет больше 2 ? Какова вероятность необнаружения ошибок при их кол-ве более 2 ? -

Обнаружение в канале связи битовых ошибок

Костян опубликовал тема в Математика и Физика

Итак дано: Канал связи между двумя устройствами, в котором допускаются единичные битовые ошибки (1..2 бита на пакет длинной 128 бит). Канал является высокоскоростной последовательной шиной со скоростями передачи ~3ГБит/с. Данные передаются пакетами по 64 байта. Для защиты от единичных ошибок требуется обнаруживать их и указать тот байт, в котором произошла ошибка. Выход кажется простым - применить код Хэмминга, который обнаруживает 2 бита ошибки. Но для последовательной передачи данных применяется кодер 8b/10b, для которого изменения одного бита информации приводит к изменению целого байта. Есть ли решение, для защиты от единичных битовых ошибок в данном случае ? -

а проше тем, что чипскопом иногда нужно тыкнутся в сигналы, находящиеся в разных модулях. как IP в этом случае вставлять не удобно ибо: 1. Нужно тянуть все до топ модуля 2. Вставлять несколько IP и тянуть контролы до топа

-

Шифрование HDL-описания

Костян ответил scorp тема в Языки проектирования на ПЛИС (FPGA)

1. Уберите все комментарии и переименуйте сигналы на sig1, sig2 и т.д. Черт ногу свернет. 2. Передавайте нетлист и модель для симуляции (создается после синтеза) -

спасибо. жаль осцилла нету (вот такие суровые инженеры сейчас в РБ) оценить изменение фронта.

-

я полагаю достаточно только фронты CLK c выхода ПЛИС завалить. Фильтровать данные смысла нету, так как они выставляются по срезу CLK, а вдвигаются по фронту в сдвиговый регистр (от среза до фронта они успевают устаканится и перекрестных помех уже нет).

-

2 Kuzmi4 спасибо, разбераюсь. для ПЛИС slave идея хорошая. для ПЛИС master не пойдет.

-

pullup действительно внесет небольшую доп емкость. А что физически происходит при переключении SLEW с fast на slow ? Так же не понятно, что физически делает Drive

-

Как увеличить фронты на Spartan3 ?

Костян опубликовал тема в Работаем с ПЛИС, области применения, выбор

Дано Spartan3, готовая плата, на которой установлена ПЛИС и устройство с SPI интерфейсом. Из-за малых фронтов сигнала создаются перекрестные помехи между сигналами SPI. Пролазят иголки и , в результате, ложные срабатывания. Схемотехника платы паршивая, мало земли. В своих платах я зачастую ставлю последовательные резисторы или емкость на CLK линию. Но в данном случае готовая плата , в которую лесть не хочется. Можно ли несколько увеличить фронт сигнала CLK настроив пины ПЛИС ? Как ? -

в первом случае не поможет, во втором работает. Знаю про этот атрибут. В общем решение следующее. Создается отдельный модуль , куда заводятся все сигналы , нужные для чипскопа, внутри модуля по или на единственный выходной пин они идут. И обязательно атрибут о строгой сохранении иерархии (я работаю с синплифаем, xst вроде по-умолчанию его выставляет) Вот тестовый пример: //---------------------------------------- // Основной модуль //---------------------------------------- module testScope( input clk, output [7:0] dout, output reg test1, output test2, output test3, output test4 ); wire [7:0] count/*synthesis syn_keep = 1*/; CountMod CntMod ( .clk(clk), .count(count) ); reg [7:0] dataToScope; Black BlackMod ( .test(test4), .dataIn(dataToScope) ); always @(posedge clk) begin test1 <= count[1]; dataToScope <= count + 2; end assign test2 = ~count[7], test3 = count[2]; assign dout = count; endmodule //---------------------------------------- // Модуль счетчика //---------------------------------------- module CountMod( input clk, output reg [7:0] count )/*synthesis syn_hier="hard"*/; always @(posedge clk) count <= count + 1; endmodule //---------------------------------------- // Модуль Тестовый //---------------------------------------- module Black( output test, input [7:0] dataIn )/*synthesis syn_hier="hard"*/; assign test = |dataIn; endmodule Сигналы для чипскопа count и dataToScope из верхнего модуля. Если есть другие предложения - пишите.

-

не совсем. 1. Иногда требуется промежуточный результат. Например , у меня есть два сигнала sig1 и sig2, мне нужно получить их промежуточную сумму sig1+sig2 и вывести это дело на чипскоп. ествественно синтезатор выкинет регистр, где будет хранится сумма. 2. Зачастую сложно найти сигнал, который нужен, так как синтезатор его переименовывает или инвертирует. Еще более неприянто, когда он делает это в шине данных (часть цепей переименовывает, часть инвертирует). Второй способ, который я вижу, это добавлять сигнал в чипскоп не посредством GUI, а использовать компонент чипскопа и заводить на него сигнал, но это куча лишних сигналов тянуть через модули.

-

ISE, как оставить регистр для chipscope, чтобы синтезатор его не выкинул ? Каким атрибутом его обозвать ? Сейчас пользуюсь следующим методом, все регистры, предназначенные для чипскоп по ИЛИ и на выходной пин. Но зачастую синтезатор меняет название некоторых пинов, что не удобно.

-

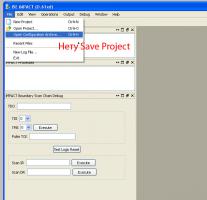

нет... не появляется, картинка с не созданным проектом показана просто для того, чтобы было понятно о чем идет речь.

-

В IMPACT ISE 13_2 пропал "Save Project"

Костян опубликовал тема в Среды разработки - обсуждаем САПРы

В IMPACT ISE 13_2 пропал пункт меню "Save Project". Переустановка не помогает. При запуске "Configure Target Device" загружается какой-то дефолтный старый проект. Вероятно путь берется где-то из переплетений Windows. Не удобно работать, приходится постоянно переконфигурировать JTAG цепочку и добавлять файл конфигурации. Кто-нибудь боролся ? -

спасибо.. работает :) кликал много уже куда, по ресету не догадался.

-

ISE не показывает Design Summary/report

Костян опубликовал тема в Среды разработки - обсуждаем САПРы

При использовании проекта в ISE через некоторое время пропадает информация с окошек Design Summary/report после сборки. Как это победить ? Пока решение - создавать новый проект и добовлять старые source файл.