djhall

Свой-

Постов

225 -

Зарегистрирован

-

Посещение

Весь контент djhall

-

Взрыво и пожаро безопасность

djhall опубликовал тема в Вопросы надежности и испытаний

Есть требование обеспечить взрыво и пожаро безопасность электронного модуля. В состав модуля входят несколько печатных плат с ПЛИС, АЦП и пр. Подскажите как это сделать? -

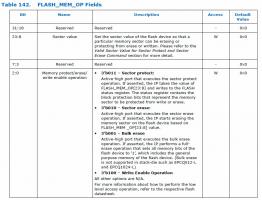

Да, так и делаю. Смещение 12. Короче, разобрался. Спасибо всем кто пытался помочь. Пришлось сделать простую систему с процессором NIOS. Дело в следующем: в функции int alt_epcq_controller2_erase_block(alt_flash_dev *flash_info, int block_offset); есть ошибка. Не знаю во всех версия Quartus или нет, у меня 17.0 Перед тем как стирать сектор, т.е. перед тем как записывать в регистр FLASH_MEM_OP[2:0] значение 3'b010 необходимо записать команду для разрешения записи, т.е. FLASH_MEM_OP[2:0] = 3'b100 Например, если нужно стереть сектор с начальным адресом 0x10000 (это первый сектор, не нулевой) сначала записываем FLASH_MEM_OP = 0x104, затем FLASH_MEM_OP = 0x102. Дополнительный код для в функции int alt_epcq_controller2_erase_block в файле altera_epcq_controller2.c выглидит так: /* calculate current sector/block number */ sector_number = (block_offset/(epcq_flash_info->sector_size)); /* sector value should occupy bits 23:8 */ mem_op_value = (sector_number << 8) & ALTERA_EPCQ_CONTROLLER2_MEM_OP_SECTOR_VALUE_MASK; /* write enable command */ mem_op_value |= 0x04; /* write sector erase command to EPCQ_MEM_OP register to erase sector "sector_number" */ IOWR_ALTERA_EPCQ_CONTROLLER2_MEM_OP(epcq_flash_info->csr_base, mem_op_value); То же самое касается и доступа к EPCQ32 с помощью любого другого мастера.

-

Нет. Я записываю в регистр FLASH_MEM_OP (Offset = 0x03) значение равное 0x02. В документации Embedded Peripherals IP User Guide -> 16. Intel FPGA Serial Flash Controller and Controller II Core сказано что это команда для стирания сектора. Т.е. я пытаюсь стереть нулевой сектор. Система у меня такая:

-

"просто SPI/QSPI" это Generic QUAD SPI Controller II ну если так то по описанию они идентичны. Я так понимаю, что в ячейку памяти нельзя записать 1 если там 0, её нужно стереть. А вот стереть не получается.

-

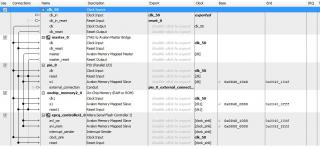

В системе не будет процессора, будет самописный компонент, который должен записывать данные в EPCQ32 являясь мастером. А отлаживаю я пока с использованием System Console и JTAG to Avalon Master Bridge, т.е. JTAG to Avalon Master Bridge пока является мастером.

-

EPCQ и Serial Flash Controller II

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Пытаюсь записать данные с помощью мастера непосредственно в EPCQ32, используя Serial Flash Controller II Если я правильно понимаю, то сначала нужно стереть сектор. Как указанно в документации Embedded Peripherals IP User Guide -> 16. Intel FPGA Serial Flash Controller and Controller II Core просто записываю 0x02 в регистр FLASH_MEM_OP чтобы стереть нулевой сектор. В результате ничего не происходит, сектор значений не меняет. Делаю я это с помощь System Console и JTAG to Avalon Master Bridge с помощью команды: master_write_32 $claim_path $offset $value Подскажите в чём может быть проблема? -

MAX10 + AFE5803

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Подскажите есть ли у кого-нибудь опыт приёма данных с помощью MAX10 от такого устройства - AFE5803. Как это делать? С помощью SERDES? -

Разобраля. Процедура следующая: - Создаём .jam файл из .jic файла - Открываем .jic файл - Заходим File -> Create / Update -> Create JAM, JBC, SVF, or ISC File... - Выбираем создание .jam файла и жмём OK. - Заходим в консоль и выполняем - quartus_jli -c1 -aconfigure -edo_epcs_unprotect <filename>.jam - quartus_jli -c1 -aprogram -edo_epcs_unprotect <filename>.jam

-

EPCQ protected sectors

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Ситуация следующая - вдруг перестала программироваться микросхема флешь памяти EPCQ32. При попытке запрограммировать .jic файл выдаёт следующую ошибку: Error (209077): Can't erase or program protected sectors in the EPCS/EPCQ device Может я что-то не так нажал или галку где-то случайно поставил. Подскажите как это исправить? -

В принципе я так и сделал, но ощущение такое что проблемы ещё будут. Например, Nios записывает настроечные параметры в регистры, затем настраивает DMA, затем запускает внешнее устройство и ждёт окончания работы DMA. Вроде всё нормально, но что будет если что-то пойдет не так и мне нужно будет прервать DMA? При работе с Flow control я мог это сделать. А вот при работе с waitrequest пока не ясно, ведь нельзя прервать транзакцию на половине.

-

Как только процессор записал последние данные для настройки DMA, DMA тут же пытается считать данные из моего компонента, а так как компонент требует дальнейшей настройки, то связка master-dma и slave-мой_компонент зависает. Почему зависает Nios не ясно может из-за того, что следующая команда в программе идёт именно продолжение настройки моего компонента, т.е. обращение к занятому компоненту. Как я понял разницу между Flow control и waitrequest: Flow control - не производит чтение или запись если устройство не готово waitrequest - производится, чтение или запись даже если устройство не готово и зависает в режиме ожидания пока устройство не будет готово. При этом занятый Slave нельзя нельзя ни записать ни прочитать другому мастеру, т.к. нельзя прервать транзакцию.

-

Чего-то я не допонимаю. Кратко опишу принцип работы моего компонента: Работает в режиме Slave. Имеет один memory-mapped интерфейс к которому подключены два мастера - один от Nios, второй чтение от DMA. Сам компонент имеет множество регистров по разным адресам в которые Nios записывает настроечные параметры, есть адрес с которого DMA считывает данные передавая их в память. Как было раньше: Nios записывает настроечные параметры в регистры, затем настраивает DMA, затем запускает внешнее устройство и ждёт окончания работы DMA. Как сейчас: Nios записывает настроечные параметры в регистры, затем настраивает DMA и далее зависает. И не удивительно, ведь сейчас выставлен сигнал ожидания waitrequest и доступ к компоненту блокируется следовательно внешнее устройство не запускается, данные не поступают и ожидание длится вечно. С Flow control такой ерунды не было. Какие варианты решения могут быть?

-

Мой компонент работает с memory-mapped. Переделывать сейчас не вариант. Сейчас нужно адаптировать по быстрому.

-

Я так понимаю, что в современной спецификации на шину Avalon нет сигналов Flow Control, я имею ввиду readyfordata и dataavailable. Но у меня есть довольно старый компонент, который как раз и предназначается для чтения и записи данных с использованием DMA и который использует сигналы readyfordata и dataavailable. Подскажите как обновить этот компонент для работы по современной спецификации. Какие есть замены для сигналов readyfordata и dataavailable?

-

Как оказалось компонент Altera Serial Flash Controller не любит когда из него читают данные. При открытии Memory View в Eclipse для адреса PIO, также происходит чтение и соседних адресов. А так как адрес Altera Serial Flash Controller соседствует с адресом PIO, то происходит и его чтение, что и приводит к зависанию. Присвоение Altera Serial Flash Controller адреса достаточно далёкого от PIO решает проблему.

-

Да я так и делаю сейчас после добавления Altera Serial Flash Controller. Причём такое происходит не зависимо от того загружается ли процессор с EPCQ или же с Onchip memory. Т.е. само наличие контроллера EPCQ, а точнее Altera Serial Flash Controller в Qsys вызывает подобное поведение при отладке. Если же вместо Altera Serial Flash Controller использовать в Qsys Legacy EPCS/EPCQx1 Flash Controller, то всё нормально и регистры доступны при отладке.

-

Подскажите пожалуйста в чём может быть проблема. Собрал простую Qsys систему для Cyclone V - Nios, jtag, onchip memory и PIO для светодиода. Компилирую, запускаю, в отладочном режиме в Eclipse открываю Memory View забиваю адрес PIO и вижу состояние регистров, т.е. всё в порядке. Добавляю в Qsys Altera Serial Flash Controller для QUAD EPCQ32 Компилирую, запускаю, в отладочном режиме в Eclipse открываю Memory View забиваю адрес PIO и вижу Target request failed: Unable to read memory, т.е. регистры не читаются. Далее отладка отключается. Подскажите в чём может быть проблема.

-

У меня тоже не ругается. Но как же тогда ссылка в первом сообщении? Там же сказано, что VCCIO должно быть 2.5В для использования ножки как вход/выход, если меньше то только вход.

-

А какой ещё может быть выход если VCCIO = 1.8В Смущает, что написано, что при VCCIO = 1,8В, VCCPD = 2,5В и использовании LVDS - пин в том же банке может использоваться только как вход. Или я что-то не так понимаю?

-

VCCIO и VCCPD для Cyclone V

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Нашёл вот такую ссылку: https://www.altera.com/support/support-reso...1312014_45.html Как я понял там говорится, что если VCCIO = 1,8В и VCCPD = 2,5В, а также имеются LVDS входы или выходы, то ножка на 1,8В в этом банке может использоваться только как вход. Так ли это? -

Quartus тормозит

djhall ответил djhall тема в Среды разработки - обсуждаем САПРы

Как это сделать? Вообще у меня стоит две версии 12.1 и 16.1 разница в скорости открытия проекта огромна: на 12.1 около 5 секунд, на 16.1 около 20 секунд. Тоже и с диалоговыми окнами открытия файлов. Оба установлены на диске D. -

Quartus тормозит

djhall опубликовал тема в Среды разработки - обсуждаем САПРы

Последние версии Quartus жутко тормозят при работе: очень долго открывается проект, а также диалоговые окна открытия файлов. Подскажите это у всех так или может что дополнительно установить требуется? -

VREF pins

djhall ответил djhall тема в Работаем с ПЛИС, области применения, выбор

В этой микросхеме VREFB может использоваться только как опорное напряжение, как IO её использовать нельзя. Возможно ли что из-за того что они ни к чему не подключены не будет работать вход для тактовой частоты (3.3 V LVCMOS)? -

VREF pins

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Подскажите, что будет если на Cyclone 5 оставить ножки VREFB ни к чему не подключёнными. Микросхема: 5CEFA5U19C7N. Используемые стандарты: 3.3-V LVCMOS, 2.5 V, 1.8 V и LVDS. -

Структуры КИХ и БИХ фильтров

djhall ответил djhall тема в Алгоритмы ЦОС (DSP)

Спасибо за ссылку - изучу. Но всё-таки это матлаб, а мне хотелось бы понять как именно преобразовывать коэффициены, т.е. хотелось бы теории. Моя задача написать С++ прогу для фильтрации, которая могла бы фильтровать последовательно поступающие отсчёты сигнала, а также фильтровать уже имеющиеся массивы данных с помощью свёртки.